基于LabVIEW for FPGA的高速并行视觉检测系统设计

姜阔胜, 侯佳淑, 范再川, 毛中元, 周远远, 陈赛

(安徽理工大学机械工程学院, 淮南 232001)

“十四五”规划中更加注重推动人工智能平台建设,强化生产过程中的智能化[1]。机器视觉为智能化生产过程中最后一个环节,对生产的零部件进行质量检测,扮演着十分重要的角色。现有对生产的零部件检测主要有人工检测法和机器视觉检测法。传统的人工检测存在误检率、漏检率及成本高等问题,现有的机器视觉检测系统下位机大多以可编程逻辑控制器(programmable logic controller, PLC)为核心处理器,限制了零部件的检测效率[2]。面向未来的视觉检测高速并行的需求,对如何提高系统的运行效率的研究具有重要的意义。

国外在视觉检测上的研究相较中国起步早,早在20世纪70年代,视觉检测技术已经应用于工业生产过程中[3]。Westinghous公司利用不同照明光路与电荷耦合元件(charge coupled device, CCD)线阵相机相结合,为钢板表面的缺陷检测提供了一种新的检测方案[4]。Fang等[5]分析和对比表面缺陷检测计数的各种方法,并对视觉缺陷检测的剩余挑战和未来的研究趋势进行了综述性的讨论和预测。胡艺等[6]提出了一种改进的基于遗传算法的二维最大类间方差法的快速迭代算法,解决印刷电路(printed circuit board, PCB)板缺陷检测分割中存在分割效果差、运行速度慢以及适用范围小的问题。董元发等[7]采用模糊自适应的视觉检测方法解决了手工装配中微小金属件容易漏装的问题,并在工业现场成功应用。

随着视觉检测行业的发展,图像、视频等所需处理的数据量呈爆炸性增长,图像处理系统的计算能力和传输能力需要不断提高,现场可编程门阵列(field programmable gate array, FPGA)作为可编程的硬件,可以根据应用需要实现硬件动态重构,具备高度并行的流水处理能力[8]。现提出一种基于LabVIEW for FPGA的高速并行视觉检测系统,以LabVIEW作为FPGA的开发平台,利用该软件适应内、外部变化能力强的柔性特点,将软件高度开放,精简数据存储系统[9],且基于LabVIEW语言开发FPGA,相比于利用VHDL语言或者Verilog语言进行代码编写的FPGA开发模式更加简便,提高检测系统的可行性、可移植性和通用性。相较于传统视觉检测系统,本文设计的系统能够满足图像处理应用对高速数据传输和处理的需要,性能也更加的稳定。

1 检测系统总体架构

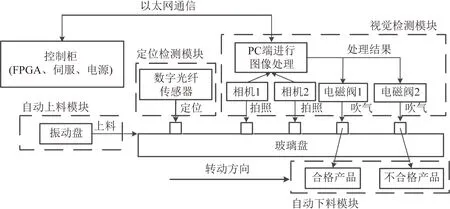

系统总体架构主要包括电源模块、自动上料模块、定位检测模块、视觉检测模块和自动下料模块,如图1所示。

检测系统通过电源降压模块将220 V交流电转化为24 V和5 V直流电,供伺服控制系统、传感器、相机等使用。为了实现自动化检测,需要对系统进行预处理设置,即拍照定位和吹气定位,利用工件从光纤传感器到相机(吹气口)之间的相对脉冲值,对每个相机(吹气口)进行精确定位,并存储定位脉冲数据。定位设置完成,系统开始运行并检测,工件通过自动上料模块(振动盘),均匀地分布在玻璃盘上,伺服电机控制玻璃盘匀速运动,当工件经过光纤传感器时,触发系统记录此时工件的初始脉冲。当实时脉冲值为初始脉冲值和定位脉冲值之和时,即工件到达相机下方,此时触发相机拍照。对采集的图像进行分析处理,得到被检测工件是否符合预设要求的结果,将合格或者不合格的处理结果传给FPGA,由FPGA根据不同的处理结果控制不同的电磁阀工作,将不同质量的工件进行分区。

2 硬件系统组成

硬件系统由上位机处理计算机、FPGA、伺服控制器和伺服电机、数字光纤传感器、工业相机、电磁阀组成。硬件各功能之间的具体联系如图2所示。

图2 系统硬件图Fig.2 System hardware diagram

3 检测系统程序设计

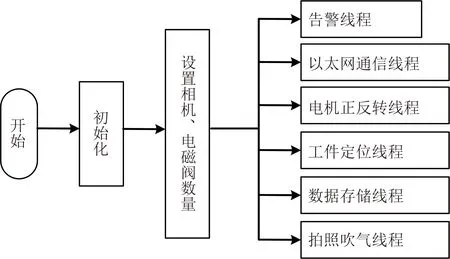

该系统软件由初始化告警线程、以太网通信线程、电机正反转线程、工件定位线程、数据存储线程和拍照吹气线程组成。FPGA下位机程序设计是整个系统的核心,初始化告警线程可以实现设备初始化和处理各类紧急情况;以太网通信线程保证了下位机和上位机的通信;电机正反转线程控制伺服电机带动玻璃盘运动;工件定位线程用来获取脉冲数据;数据存储线程实现对大量采集到脉冲数据的存

图1 检测系统总体架构Fig.1 Overall architecture of the detection system

储;拍照吹气线程用于获取工件图像信息以及对工件进行分类处理。各线程之间相互独立、并行实现,依托LabVIEW高移植性设置多相机、多电磁阀程序,根据具体应用要求,对上位机指令进行设置。

首先下位机上电复位、各设备初始化,系统运行,在FPGA上进行数据处理、存储,图像信息通过以太网传输到上位机,再由上位机程序处理照片得到工件的处理结果返回到FPGA,实现对数据的分析处理从而达到对工件进行处理的目的。程序流程如图3所示。

图3 程序流程图Fig.3 Program flow chart

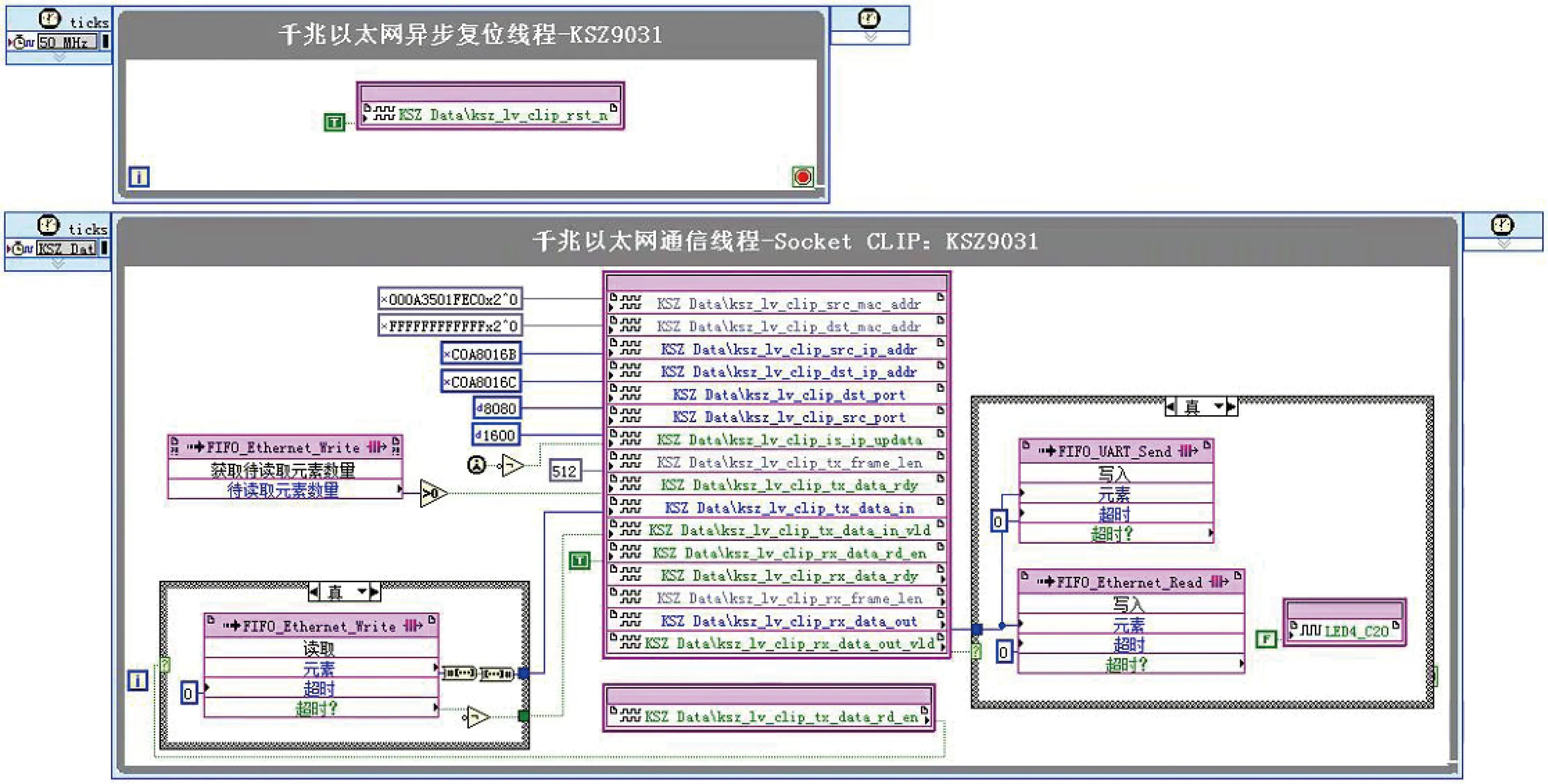

3.1 以太网通信线程

与传统的控制器局域网络(controller area network, CAN)、RS485、RS232等通信方式相比,以太网速度快、通用性更好,并且能接入Internet网络实现更大范围的远程访问[10],适用于数据传输量大的情况。FPGA的以太网数据传输是目前应用较为广泛的一种传输手段,但大多数支持千兆以太网的物理芯片并未集成传输协议栈以及接口转换模块,导致其无法直接进行数据传输[11]。针对这一问题,提出采用Socket calling line identification presentation (CLIP)技术将整个KSZ9031千兆以太网双向收发用户数据报协议(user datagram protocol, UDP)通信过程,封装成CLIP使用,然后采用LabVIEW里面的Socket CLIP方法进行整体封装。这种方法不仅提高了时钟约束能力,也进一步加快了编译速度。以太网通信的整体程序框图如图4所示。

3.2 电机正反转线程

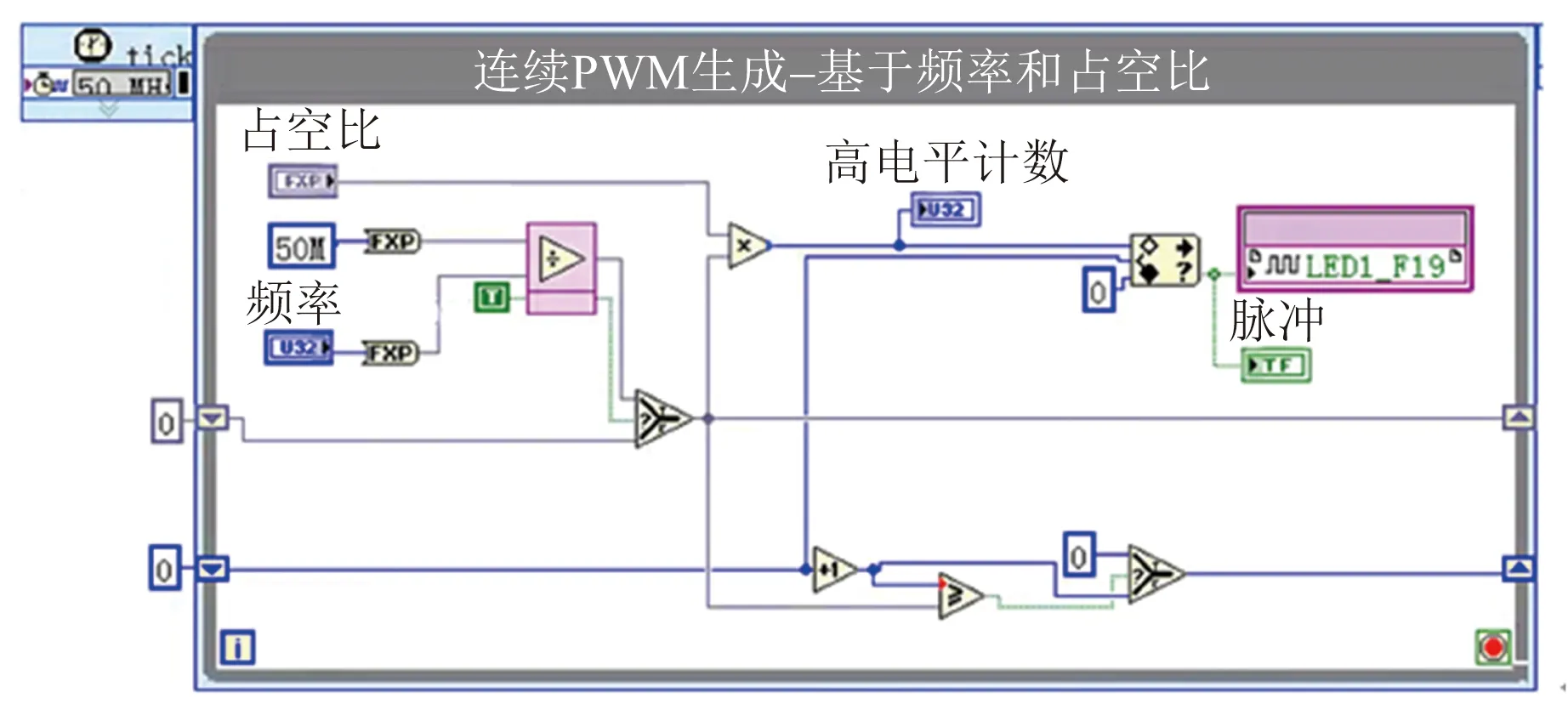

本系统利用LabVIEW for FPGA生成频率和占空比任意调节的脉冲宽度调制(pulse width modulation, PWM)信号来控制伺服电机的速度。PWM的频

KSZ_Dataksz_1_lv_clip_rst_n为以太网芯片复位;KSZ_Dataksz_lv_clip_src_mac_addr为FPGA端的MAC地址;KSZ_Dataksz_lv_clip_dst_mac_addr为目标端的MAC地址;KSZ_Dataksz_lv_clip_src_ip_addr为FPGA端的IP地址;KSZ_Dataksz_lv_clip_dst_ip_addr为目标设备的IP地址;KSZ_Dataksz_lv_clip_dst_port为目标设备的IP端口;KSZ_Dataksz_lv_clip_src_port为FPGA端的IP端口;KSZ_Dataksz_lv_clip_is_ip_updata为参数更新使能信号;KSZ_Dataksz_lv_clip_tx_frame_len为FPGA发送UDP数据包长度;KSZ_Dataksz_lv_clip_tx_data_rdy为FPGA通知CLIP准备好接收FPGA发送的数据;KSZ_Dataksz_lv_clip_tx_data_in为CLIP数据输入端口;KSZ_Dataksz_lv_clip_tx_data_in_vld为CLIP数据输入有效端口;KSZ_Dataksz_lv_clip_rx_data_rd_en为FPGA接收到PC下发的UDP包;KSZ_Dataksz_lv_clip_rx_data_rdy为FPGA接收的UDP包是否有效;KSZ_Dataksz_lv_clip_rx_frame_len为FPGA过滤出来的有效UDP包里面的真实数据长度;KSZ_Dataksz_lv_clip_rx_data_out为FPGA过滤出来的有效UDP包里面的数据区;KSZ_Dataksz_lv_clip_rx_data_out_vld为数据有效信号;KSZ_Dataksz_lv_clip_tx_data_rd_en为CLIP是否能接收FIFO里面的数据使能信号;FIFO_Ethernet_Write为以太网写数据缓存;FIFO_Ethernet_Read为以太网读数据缓存;FIFO_UART_Send为以太网读数据缓存图4 以太网通讯程序Fig.4 Ethernet communication program

率和占空比可由上位机自由设定。其中PWM的频率对应电机转速,PWM的脉冲宽度对应电机转过的角度。上位机通过以太网通信发送相应的指令来控制伺服电机的正反转和速度。电机正反转线程的设计如图5所示。

图5 电机正反转线程Fig.5 Motor forward and reverse thread

3.3 数据存储线程

系统的运行过程中需要对大量数据进行高速存取,在高速大容量的存储系统中,传输通道为实时的双向链路,需要采用面向存储的高性能双向串行外围接口(serial peripheral interface, SPI)传输接口来实现[12]。为了满足对存储容量和速度的要求,系统选用Flash存储数据。光纤传感器产生信号触发Flash执行脉冲数据写入操作;相机拍照触发Flash执行脉冲数据读取操作。

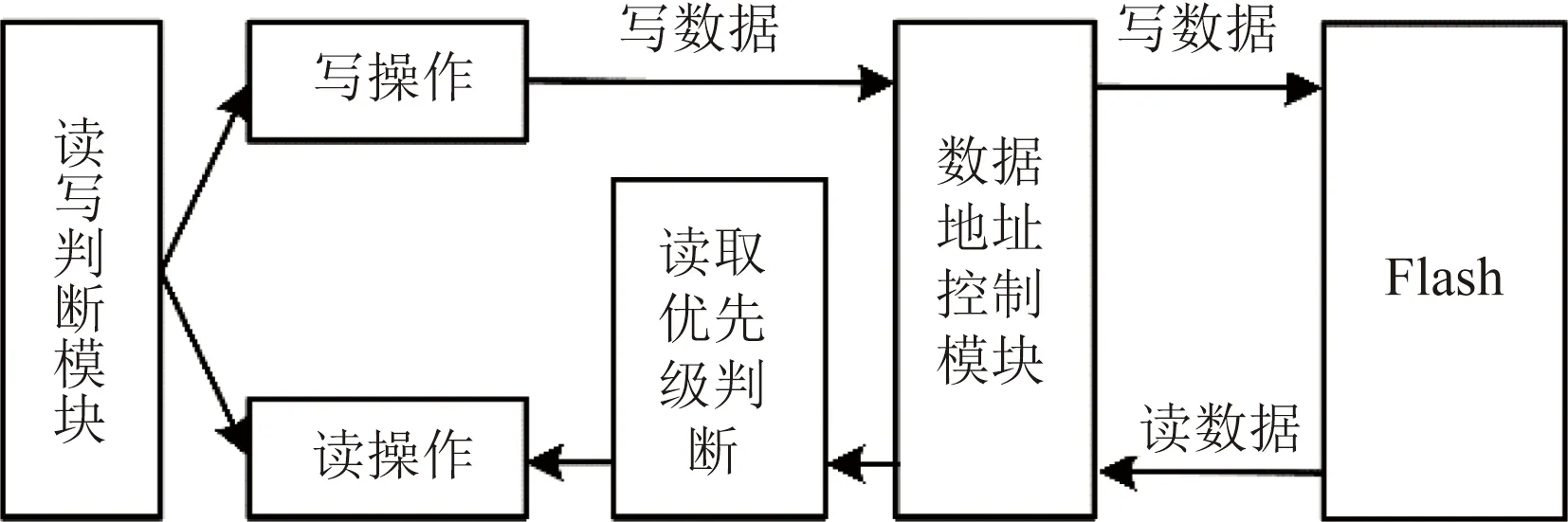

在实际应用中,由于Flash同一时刻只能允许有一个主控,为解决在数据存取过程中同时有多个数据读取请求的问题,设计读取数据防冲突模块,完成对Flash多通道实时读取的需求。数据处理流程如图6所示。

图6 数据处理流程图Fig.6 Data processing flowchart

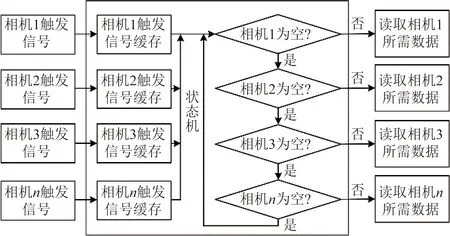

读取优先级判断模块如图7所示,相机的个数可根据实际情况由PC端设定。

4 实验与结果分析

4.1 实验分析

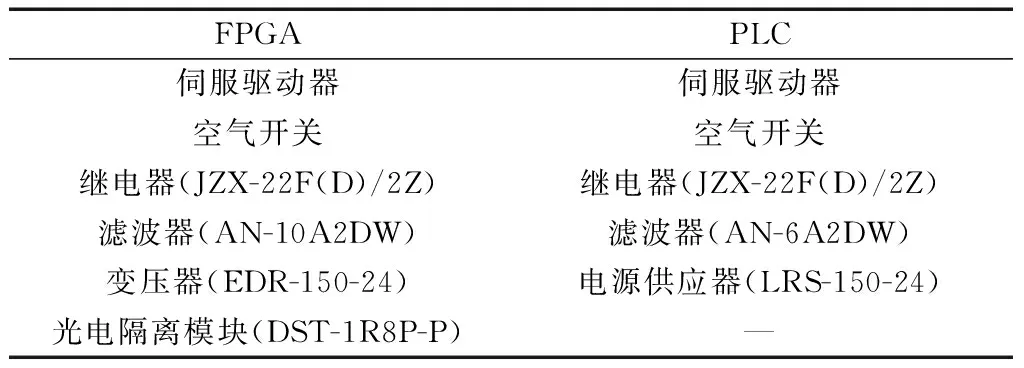

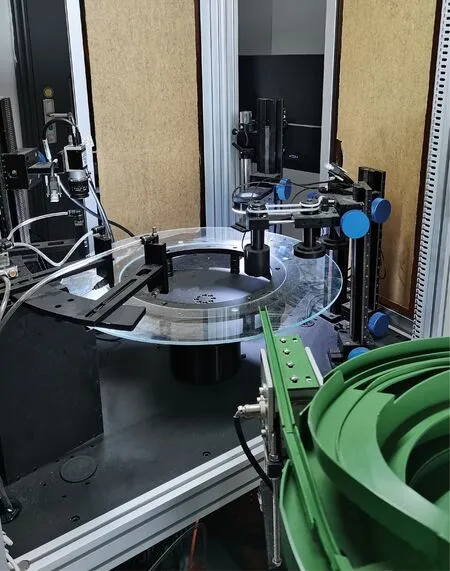

为证明设计的基于LabVIEW for FPGA的高速并行视觉检测系统的有效性、可靠性以及高效性,设置如下实验,将原有的PLC视觉检测系统作为实验中的对比系统进行对比实验。实验中配置的设备具体如表1所示。本视觉检测系统实物图如图8所示。

图7 读取优先级判断模块Fig.7 Read priority judgment module

表1 实验台配置Table 1 Test bench configuration

图8 检测系统实物图Fig.8 Physical image of the detection system

4.2 实验结果

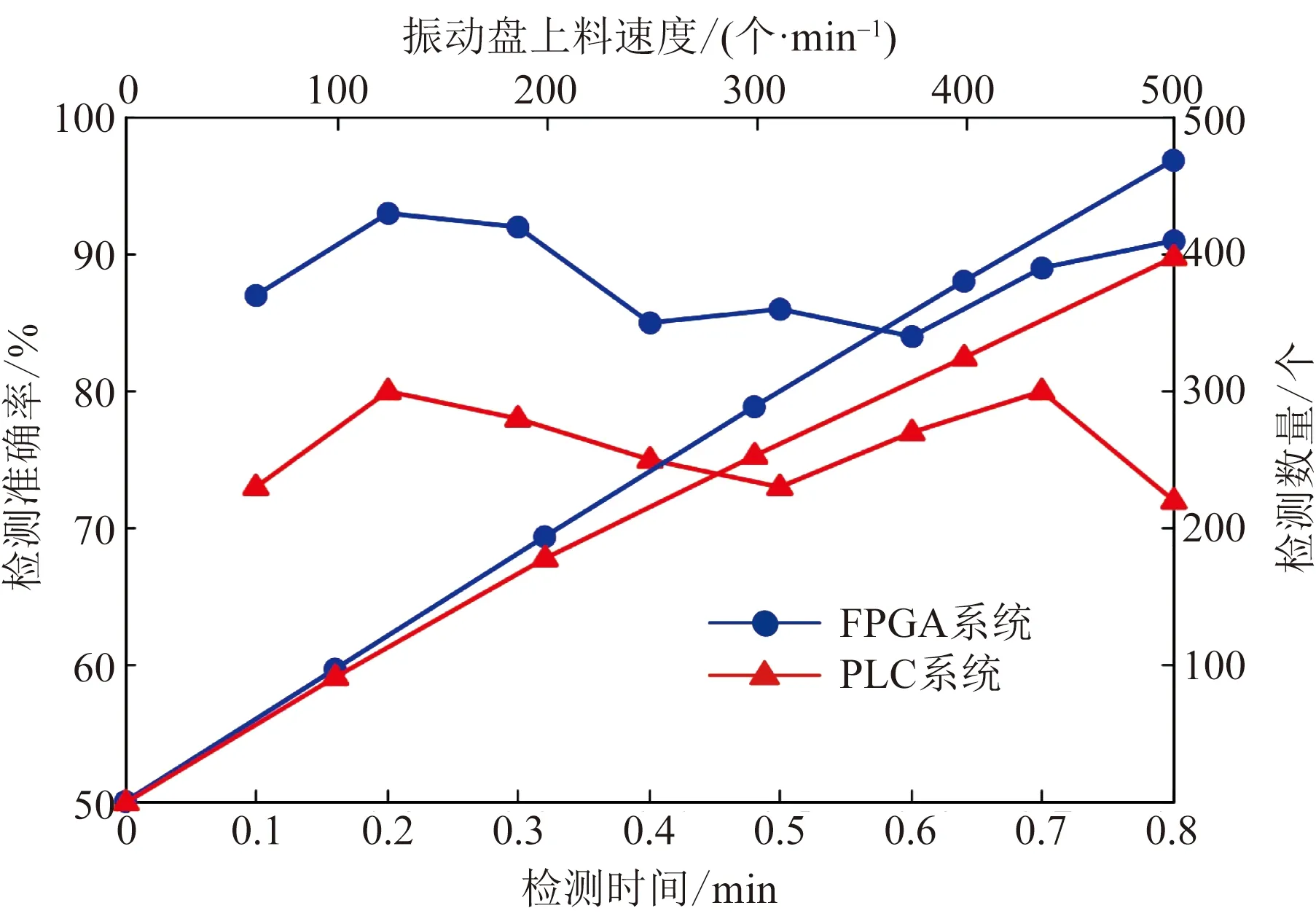

利用上述实验参数和实验装置进行实验验证,实验结果如图9所示。可以看出,在振动盘上料速度较为缓慢时,两种系统有效处理工件数相近;当振动盘上料速度加快时,基于LabVIEW for FPGA的高速并行视觉检测系统处理工件数量明显多于传统基于PLC的视觉检测系统。分析检测准确率可知随着检测时间的增加,基于LabVIEW for FPGA的高速并行视觉检测系统和基于PLC的视觉检测系统

图9 实验数据对比Fig.9 Comparison of experimental data

的检测准确率都在变化,但本文系统的准确性始终位于传统系统的准确性之上,证明本文系统的检测准确性更高。实验结果表明本系统的检测用时较少,检测效率和准确率都高于传统检测系统。分析原因,FPGA执行速度更快能够更好的保证工件处于相机视野中心,因此易于获得理想照片和分析处理结果。

5 结论

设计了一种基于LabVIEW for FPGA的视觉检测设备测控系统,在设计的系统总体框架上搭建实验平台,并进行硬件选型,用FPGA控制代替PLC控制有效地解决了PLC串行执行限制系统运行速度的问题,提高了系统的稳定性、运行速度和检测效率。使用图形化语言在LabVIEW平台上编写软件程序,增加了系统的柔性,降低了开发难度。实验证明,采用FPGA设计视觉检测系统,能满足视觉检测的实际需求。