基于射频收发器的高中频DBF系统设计

吴彬彬, 全英汇,*, 肖国尧, 李亚超, 邢孟道

(1. 西安电子科技大学电子工程学院, 陕西 西安 710071;2. 西安电子科技大学雷达信号处理国家重点实验室, 陕西 西安 710071)

0 引 言

数字波束形成技术通过改变数字基带域各个通道的幅相参数,在数字阵列天线上形成空域波束,具有宽角度扫描、抗干扰和波束捷变的能力。同时,数字波束形成技术也面临着体积、功耗、性能、多通道同步等方面的严峻挑战。随着雷达与通信技术的发展,无人机、导弹、微纳卫星等小型无人平台对数字波束形成技术的需求不断增加,研制一种灵活、小型、高精度、自适应、抗干扰、高性能的数字波束形成系统具有重要意义。

早期人们对数字波束形成系统的研究主要在于数字发射和接收(transmitter and receiver,T/R)组件与接收多通道数字下变频(digital down converter,DDC)技术。Garrod在1995年首次研制了基于数字T/R组件的16单元相控阵雷达测试平台。从2000年开始,美国海军研究实验室、林肯实验室等一起设计完成了一套基于直接数字合成(direct digital synthesizer,DDS)的发射数字波束形成(digital beam forming, DBF)技术和基于模数转换器(analog to digital converter,ADC)的接收多通道DDC技术的数字阵列雷达。Applied Radar公司在2010年研制了4通道500 MHz宽带收发的全数字T/R组件。国内,1998年研制出4单元基于DDS技术的DBF发射阵,2000年9月研制成功8单元一维收发全数字波束形成试验系统,2018年提出了一种各通道独立的数字中频架构相控阵接收组件。

近年来,许多学者在DBF系统方面提出了不同的设计方案,德国航空航天中心微波和雷达研究所在2015年提出一种星载高集成双频数字波束形成系统,采用二维贴片天线单元实现波束形成,这种结构不利于多通道间一致性校准,造成灵活性较差。东南大学在2017年提出了一种采用时变矢量调制的S波段数字波束发射系统,通过DDS产生射频信号,再由矢量调制器对各个通道进行移相和调幅。韩国科学技术高等学院在2017年提出了一种基于软件无线电的高分辨率数字波束形成技术,利用数字混频器和数字信号源设计了数字移相器,具有较高的灵活性,但由于采用零中频架构,射频频率受限于软件无线电芯片,无法满足高频段需求。佛罗里达国际大学在2019年提出了基于Xilinx公司射频片上系统(radio-frequency system-on-chip,RFSOC)的小型数字波束形成方法,采用直接射频采样的发射机和接收机架构,但由于采样率极高,在大规模阵列应用上将极大地增加功耗。电子科技大学在2020年完成了基于射频收发器AD9371的数字波束形成收发机测试平台,采用零中频架构实现5G通信系统的64天线单元的数字波束形成,无法满足6 GHz以上高频段的通信和雷达系统要求。

针对上述问题,本文研究并分析了一些现有数字波束形成方案。考虑到集成化、高精度、宽带、灵活、低功耗和Ku波段的需求,对比了各个方案的优缺点,提出一种基于射频收发器的高中频架构数字波束形成系统,实现了64通道接收、64通道发射、全数字、100 MHz带宽、Ku射频波段的功能,并具备高精度、高性能、灵活的特点。

1 接收机和发射机架构分析

1.1 现有DBF发射机方案分析

常见的DBF发射机方案包括程控移相器方案、DDS移频移相方案、数字中频时延方案、直接射频采样方案、零中频架构方案。

程控移相器方案在射频前端的每个通道放置程控移相器,一般用于子阵级的简单波束形成,电路简单,有利于模块化设计,但移相器量化精度有限,难以满足高精度高性能的要求。

DDS移频移相方案采用DDS芯片产生发射波形,通过控制各个通道DDS的初始频率和初始相位,实现波束形成。该方案能够产生高质量的单频和线性调频信号,降低波形设计复杂度。但在线性调频信号产生周期内,无法实时控制信号的相位和幅度。在宽带阵列波束形成中易发生“孔径渡越”现象。

数字中频时延的方式在数字域中实现波形的精确延时,包括时钟周期整数倍延时和分数延时,然后通过高速数模转换器(digital to analog converter,DAC)转换成模拟中频信号。该方案有效地减轻了射频前端的设计难度。但由于数字时延算法复杂,在大规模数字阵列中将极大地提高数字信号处理复杂度。

直接射频采样方案可直接在射频域实现数字和模拟的互相转换,采样率可高达10 Gsps,极大地提高了信号瞬时带宽和波形可重构能力。但极高的采样率同样带来了极大的功耗,也不适用于高射频波段。

零中频架构将基带信号与射频信号直接通过正交混频器进行互相转换。一般采用集成了DAC、ADC和正交混频器的射频收发器实现,零中频架构方案有利于小型化设计。但由于射频收发器的调谐频率范围有限,零中频架构将难以适用于高射频波段的应用。

1.2 本文高中频架构方案

1.2.1 高中频架构原理

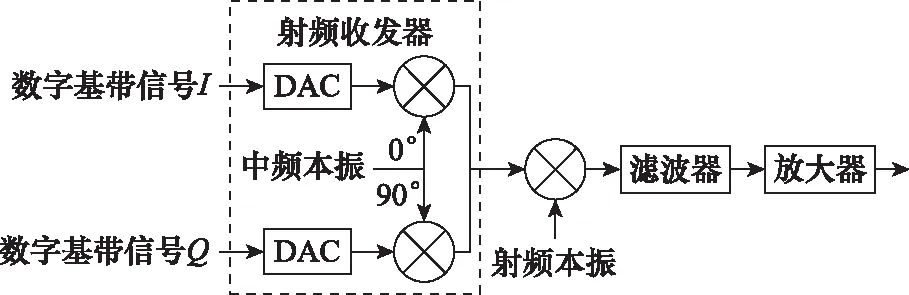

本文高中频架构的发射机采用射频收发器实现基带数字信号与中频模拟信号的转换,如图1所示,两路正交的基带数字信号通过两个DAC转换成基带模拟信号,由正交混频器生成一路中频信号。再通过外部元件依次实现二次混频、滤波和功率放大,最终产生Ku波段的射频信号。其中,在不改变射频信号频率的情况下,中频本振和射频本振的频率可在较大范围内灵活调谐,尽可能地避开干扰杂散。同理,接收机与发射机的设计思路一致,如图2所示,射频信号从天线阵列接收之后,依次经过低噪声放大、下变频、滤波,然后进入射频收发器,实现正交下变频和模数转换,最终产生数字基带信号。

图1 高中频架构发射通道示意图Fig.1 Schematic diagram of transmission channel of high intermediate frequency architecture

图2 高中频架构接收通道示意图Fig.2 Schematic diagram of receiving channel of high intermediate frequency architecture

1.2.2 高中频架构的频率规划分析

除了精度和噪声系数之外,组合频率干扰也是影响接收机和发射机性能的一项主要指标。由于混频器的非线性特点,其输出的组合频率分布为±,其中为混频器输入信号频率,为本振信号频率,,=0,1,2,…。阶数=+越大,组合频率的影响越小。

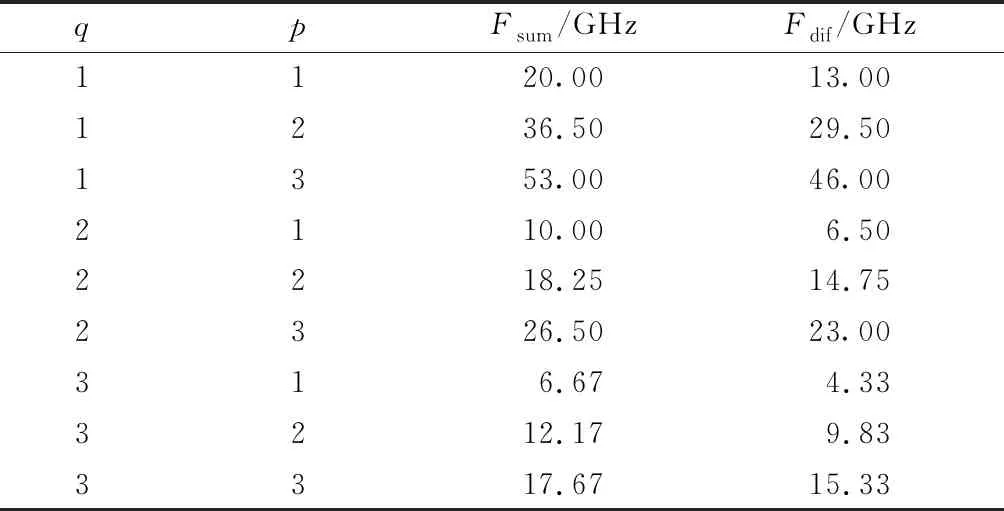

若设计时没有考虑到接收机和发射机的信号频率规划,易导致干扰信号、射频信号和本振信号形成的多种频率组合,窜入中频信号带宽内。接收机的射频频率输入范围在12~15 GHz,中频频率为3.5 GHz,当接收器调谐频率为13 GHz时,本振频率取值为=3.5 GHz+13 GHz=16.5 GHz,可计算出可能引起带内的×杂散频率分布为(±),取,=1,2,3,结果如表1所示。

表1 FLO=16.5 GHz的p×q杂散频率分布

表1中的14.75 GHz和12.17 GHz杂散信号在12~15 GHz范围的通带内,其中14.75 GHz与16.5 GHz的本振信号经过混频器可产生16.5 GHz×2-14.75 GHz×2=3.5 GHz的杂散信号,对原本的中频信号进行干扰。

若采用传统的超外差式接收机架构,由于ADC接收的数字中频信号带宽较窄,如果进行一级混频,则接收机将很难抑制镜像频率。所以一般需要经过两次混频,或者采用基于ADC、DDS的数字中频方式,而第一中频信号的中心频率固定不变。在调谐射频频率时,难以避免×杂散频率带来的干扰。同时为了抑制大量的非目标频率,对滤波电路的要求通常也非常高。

而本系统采用的高中频接收机和发射机架构,在不改变射频信号频率的情况下,可通过灵活的中频频率调谐能力,有效避开×杂散频率。将上述接收机的中频频率调谐至5 GHz,为了接收13 GHz的射频信号,则本振调节至18 GHz,可计算出如表2所示的×杂散频率分布。

表2 FLO=18 GHz的p×q杂散频率分布

除了表2中的13 GHz所需频率,还有13.6 GHz的杂散在12~15 GHz通带内,但13.6 GHz杂散与18 GHz本振的频率组合无法生成5 GHz的干扰。而其余的杂散均分布在通带之外,经过滤波器抑制掉。

1.2.3 高中频架构方案总结

基于高中频架构的发射机和接收机具备许多优点。首先,高集成度的射频收发器不但将ADC、DAC、正交混频、数字有限脉冲响应(finite impulse response,FIR)滤波、中频模拟滤波、幅度衰减等功能集成在同一块芯片上,尽可能减少了电路板布局面积,有利于实现小型化设计,同时也极大地减少了布线误差与板级电磁干扰。其次,较宽的中频调谐范围使得板内的基带、中频、射频信号之间能够灵活避开干扰频率,有利于提高系统性能。此外,数字域中对基带正交信号进行处理,可灵活地处理各通道的幅度与相位加权,同时充分利用较低的采样频率实现更多的波形处理功能,减轻了数字信号处理难度。

本文高中频架构方案,相较于程控移相器方案,波形的相位调节精度更高,可实现低副瓣波束加权和更高性能;相较于DDS移频移相方案,波形重构能力更强,易于宽带幅相矫正;相较于数字中频时延方案,较大程度地减少了用于延时计算的数字信号处理难度,提高了实时性;相较于直接射频采样方案和零中频架构方案,提高了射频工作频段。

总之,高中频架构方案在满足收发全数字、高精度、高性能、宽带和Ku波段的要求之外,还尽可能地简化了电路设计,减小了电路体积和系统设计难度。

2 硬件设计

2.1 高中频架构设计

高中频架构的接收器和发射器需要生成频率较高的中频,为了能够自适应地避开杂散频率干扰,还需要拥有灵活的中频本振频率调谐功能。

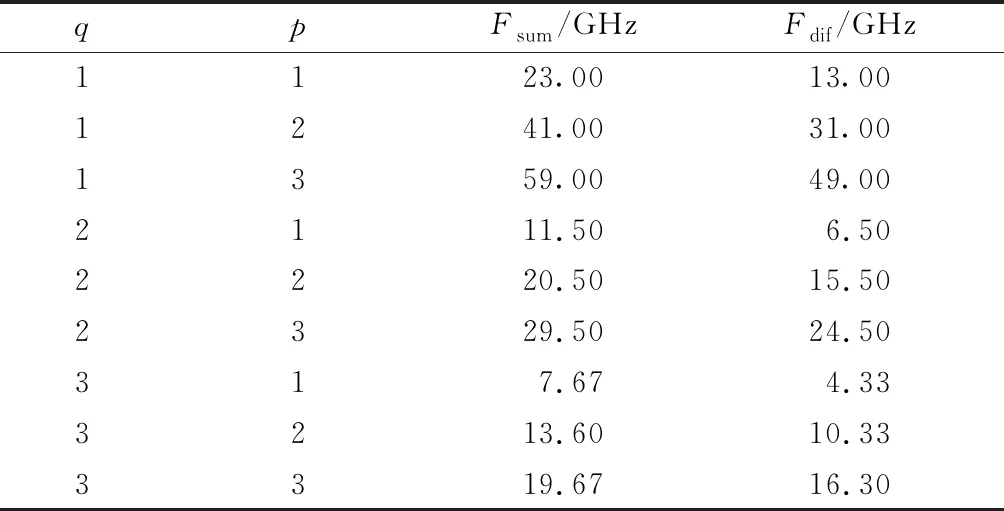

AD9371射频收发器集成了正交混频器、中频滤波、数字FIR滤波、程控放大器、ADC以及DAC,将模拟与数字信号链做在同一个硅片上。射频收发器AD9371由现场可编程逻辑门阵列(field programmable gate array,FPGA)驱动与控制输出。基于AD9371的高中频架构如图3所示,可实现300 MHz至6 GHz大范围的中频本振调谐,并配合射频前端的射频本振调谐,能够尽可能地避开由混频器带来的组合频率杂散干扰。

图3 高中频架构Fig.3 High intermediate frequency architecture

由于AD9371的高集成度,将数模混合电路集成在同一个硅片上,尽可能减少了印制电路板带来的误差,同时也能很大程度地降低功耗和体积。AD9371芯片拥有2个接收通道和2个发射通道,接收增益为16 dB,噪声系数为19 dB,瞬时带宽100 MHz,功耗约为5 W,封装面积为12 mm×12 mm。对比等效的超外差架构,高中频架构设计可以减少50%左右的面积,功耗降低30%左右。其次,基于AD9371的高中频架构对于抑制干扰杂散具有很大优势。AD9371片内集成正交纠错(quadrature error correction,QEC)校准功能,能达到75~80 dB的镜像抑制性能。

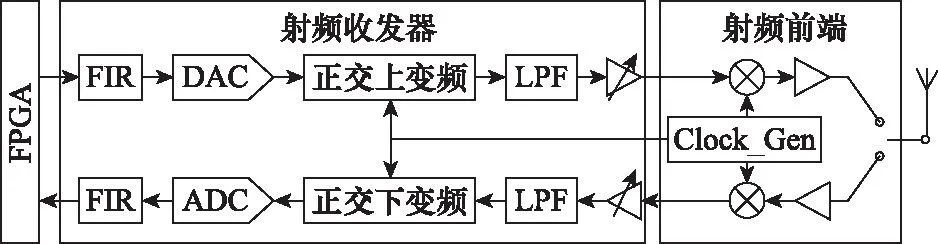

2.2 系统框架设计

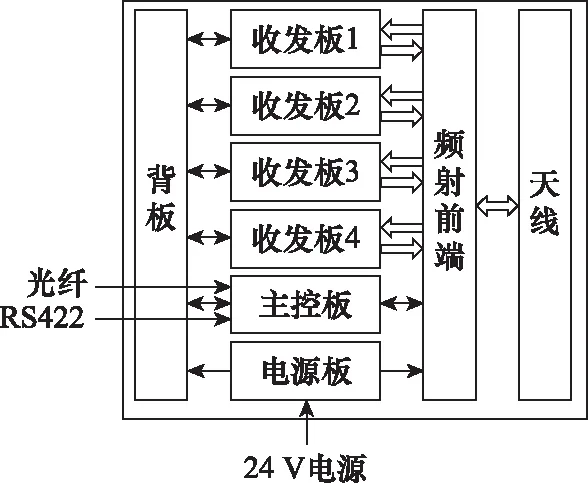

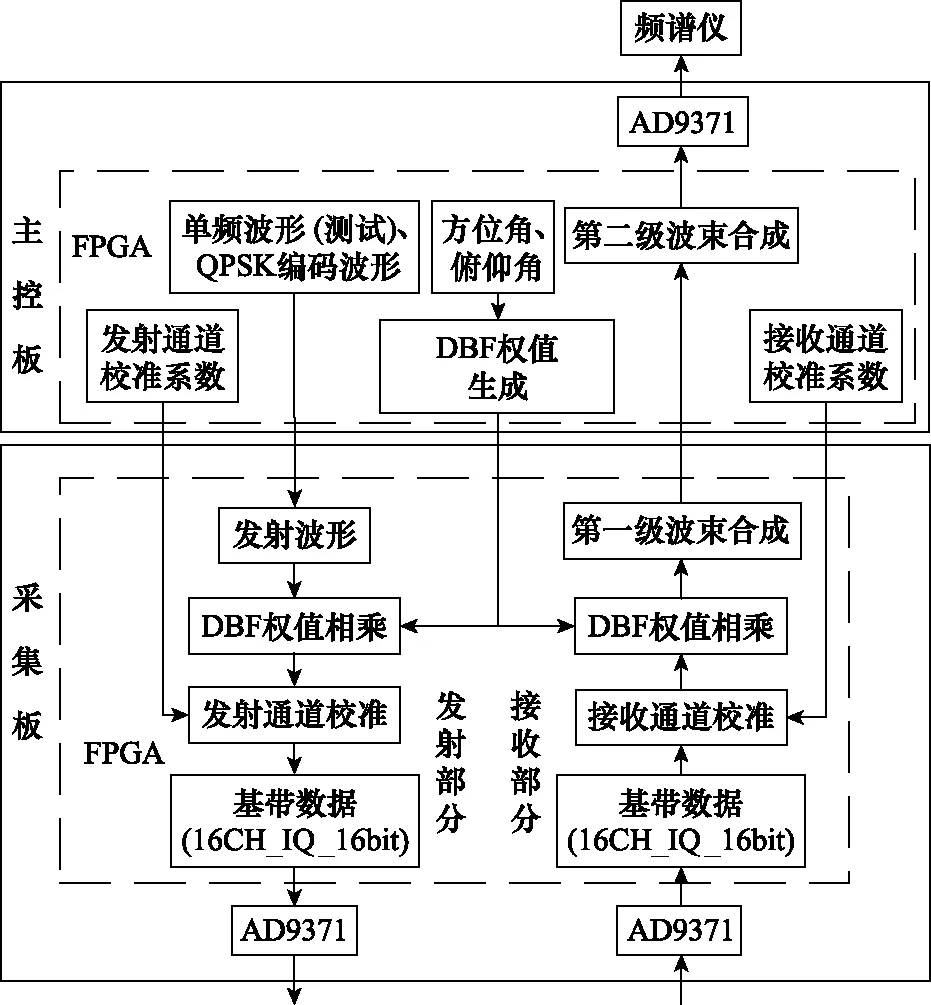

图4显示的是系统的框架图,主要由收发板、主控板、电源板、背板、射频前端模块和天线阵列组成,根据系统的收发通道数量来适当调整收发板和射频收发器的个数。为了提升系统的灵活性,采用VPX标准总线架构,收发板、主控板和电源板的尺寸按照6U标准设计,收发板1~4与射频前端是对插结构。

图4 系统框图Fig.4 System block diagram

收发板完成采集接收数据、第一级合成接收波束、产生发射数据、分配发射DBF权值、正交混频。主控板完成多通道校准、光模块基带数据收发、DBF权值计算、来波方向估计、第二级合成接收波束。电源板用于将24 V输入电源转换成12 V并输出至背板,提供系统电源。背板用于收发板与主控板之间的信号连接以及12 V的电源输入。射频前端模块用于对发射通道和接收通道实现上下变频、信号放大和通道校准。天线阵列的阵元数量有8×8个,天线阵列模块可通过超小型连接器(sub-miniature-P,SMP)射频接插件与射频前端。

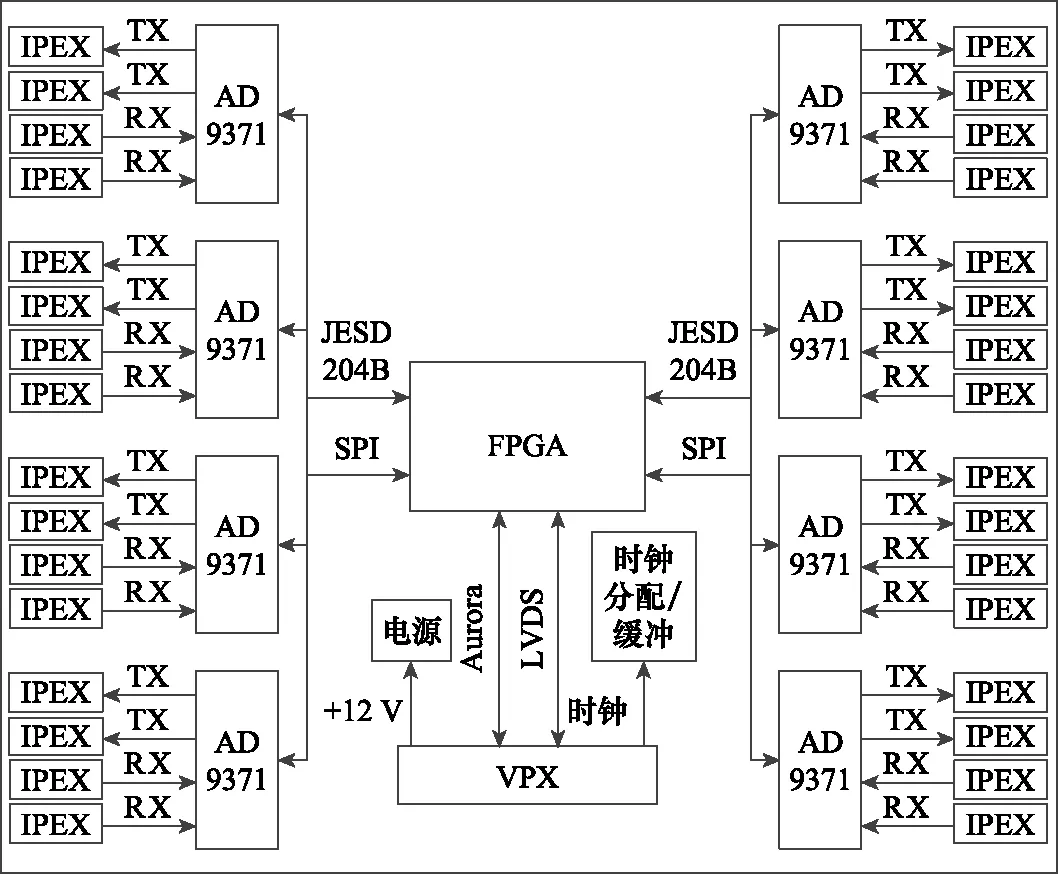

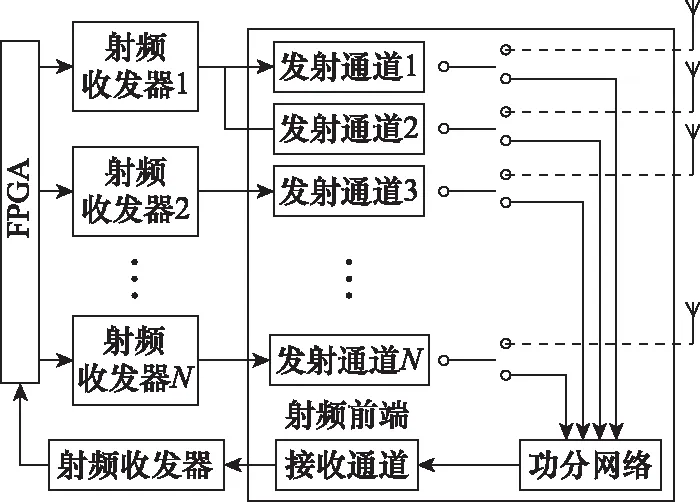

2.3 收发板设计

收发板主要由FPGA和射频收发器AD9371组成。单片AD9371集成了2路发射通道与2路接收通道,通过串行外设接口(serial peripheral interface,SPI)接口配置工作模式,以JESD204B高速串行数据链路连接FPGA。按照6U板卡的尺寸来设计,一块收发板能放置8片AD9371以及相应的外围电路,所以有16个发射通道和16个接收通道,总共需要4块收发板就能实现数字多波束形成系统的64发射通道和64接收通道。收发板的框架图如图5所示。对于收发板的FPGA选型,重点考虑的是千兆比特收发器(gigabyte transceiver,GT)的数量,而不是逻辑资源。一片AD9371的JESD204B接口收发各有4 lane,正好一个bank的GT接口,一块板卡上有8片AD9371,所以共需要8个bank共32对GT接口。加上需要留有余量和主控板进行高速互联,会占用更多GT资源,所以选用拥有64对GT资源的Xilinx公司Virtex-7系列的XC7VX690T芯片。

图5 收发板框图Fig.5 Block diagram of transceiver board

考虑到系统小型化与功耗,收发板的电源电路设计、射频接插件选型和印制电路板(printed circuit board,PCB)布局需要重点关注。FPGA的电源芯片采用集成了开关控制器、功率场效应管、电感器和其他相关元件的DC/DC开关电源LTM4628和LTM4644,只需外接少量的阻容即可构成完整的电源电路,尽可能减少布局面积。AD9371的供电选用型号为ADP5054的DC/DC开关电源,可配置为2路1.3 V、1路1.8 V和1路3.3 V分别提供到AD9371的4路电源输入,1片ADP5054可满足2片AD9371的供电需求,1块收发板只需要4片ADP5054即可。由于采用8片AD9371,共16发16收的射频通道,PCB对称布局将很好地保证模拟电路的多通道一致性。将FPGA布置于板卡中心,射频收发器及其模拟通道分布在两侧,尽可能隔离数字电路对模拟电路的干扰。射频接插件采用超小型封装的IPEX型号,并通过射频同轴线转接到板卡前的SSMP接插件上,方便和射频前端模块直接进行对插。整个收发板的实物图如图6所示。

图6 收发板实物Fig.6 Physical transceiver board

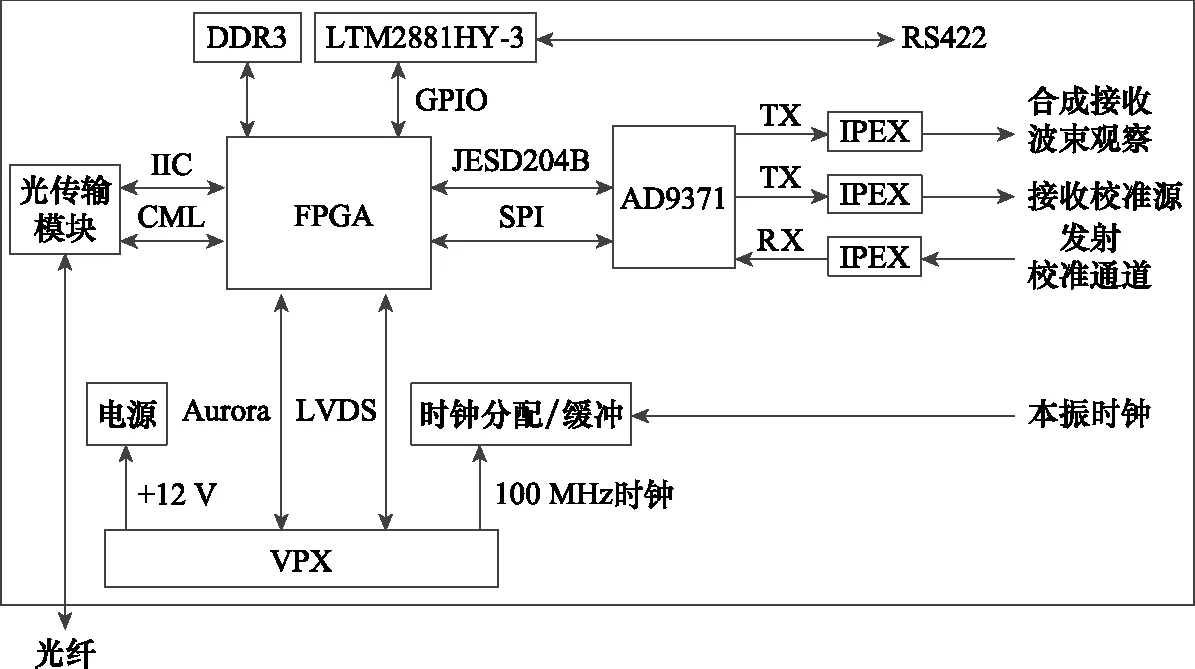

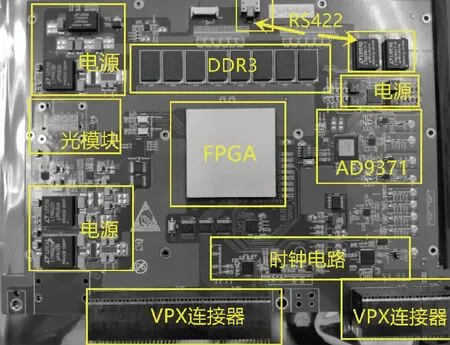

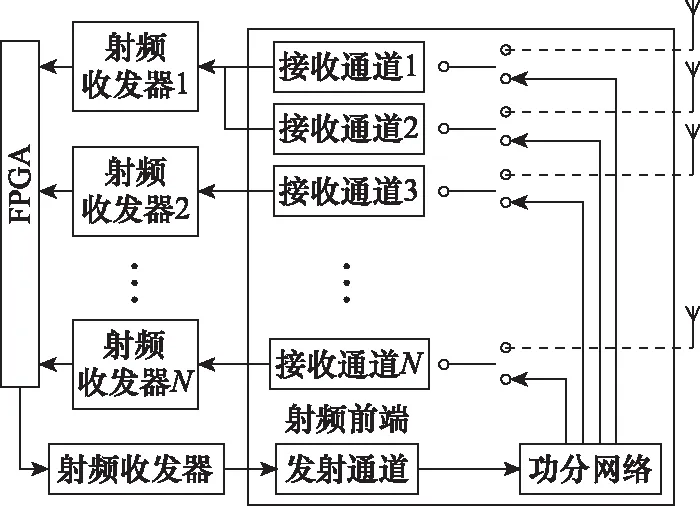

2.4 主控板设计

主控板作为整个系统的控制、数据交换与算法实现的中心,主要部件包括FPGA、双倍速率(double data rate 3,DDR3)同步动态随机存储器、光纤传输模块、射频收发器、对外控制接口。FPGA选型需要满足接口数量和逻辑资源的要求,并考虑到调试方便,选用与收发板相同的Virtex-7系列XC7VX690T芯片,对应的电源电路也相同。DDR3存储器选用8片Micron公司的MT41J256M16HA芯片,用于对数据的缓存与算法实现。光纤传输模块为中航光电的HTG8503-MH-T001YY,可12路并行收发,单通道传输速率为10.312 5 Gbps。主控板还放置1片AD9371,作为通道校准模式下的发射参考信号源和接收参考通道。对外接口芯片采用ADI公司的LTM2881HY-3为专用的隔离型RS485/RS422收发器,用来控制射频频综模块。

在与收发板的高速互联方面,FPGA之间通过Aurora协议进行高速数据传输,单链路速率最高支持0.5~6.6 Gbps。主控板分别提供2个bank的GT接口到每个收发板,总共需要8个bank,也就是32 lane,通过背板进行连接。主控板的框架图与实物图如图7和图8所示。

图7 主控板框图Fig.7 Block diagram of main control board

图8 主控板实物Fig.8 Physical main control board

3 软件设计

3.1 底层驱动设计

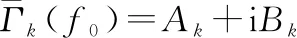

射频收发器AD9371、时钟生成器CDCM6208和光模块需要通过SPI或集成电路总线(inter-integrated circuit,IIC)接口对内部寄存器进行配置,才能进行正常的工作。由于AD9371芯片没有公开功能寄存器地址映射表,而提供了基于C语言库函数的源代码,本文介绍一种通过Xilinx嵌入式处理器软核Microblaze的方式实现系统初始化配置。

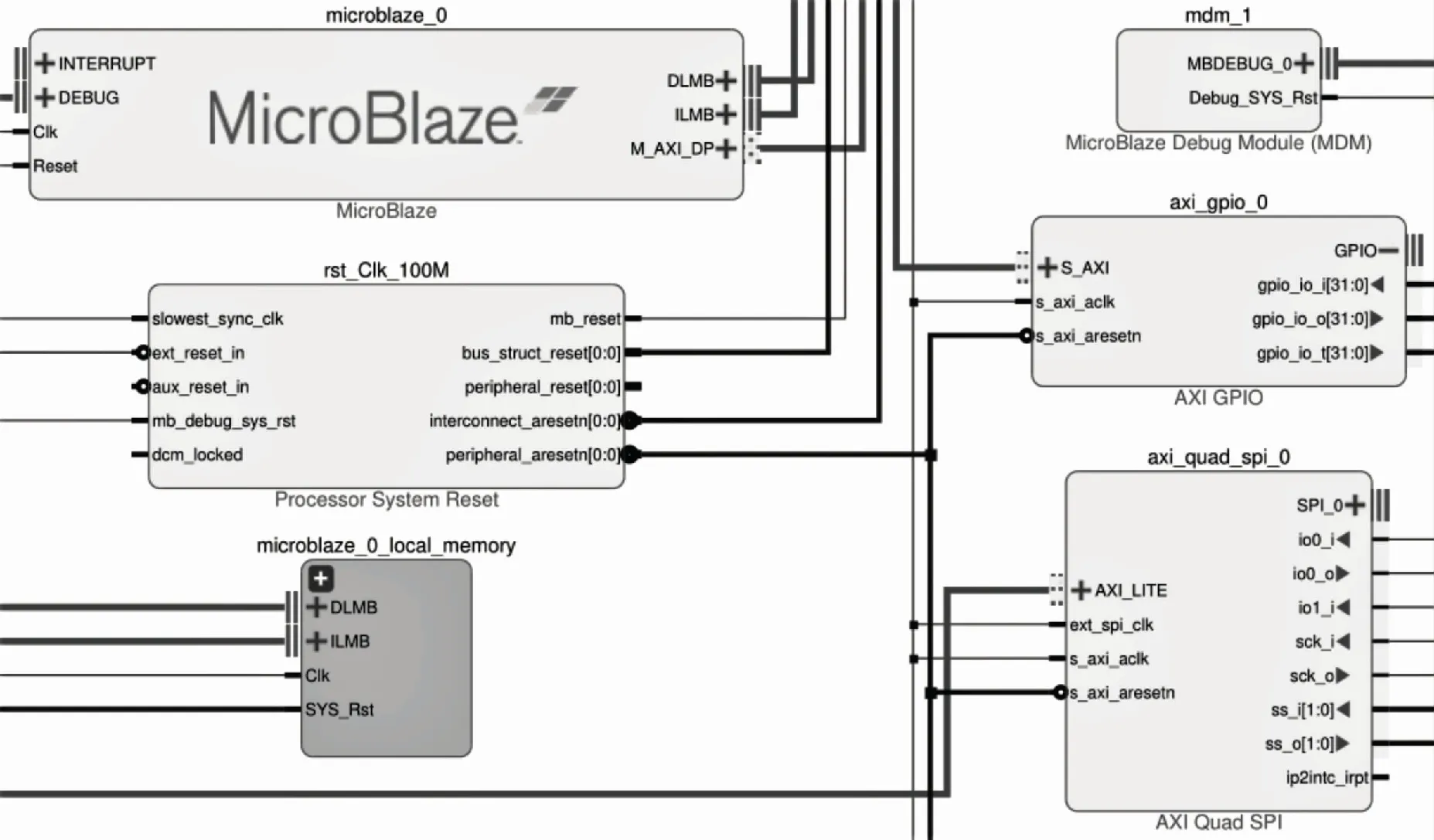

Microblaze最小系统的框图如图9所示,在Vivado设计套件中,创建Block Design,在Block Design中添加Microblaze IP以及相应的外围模块,包括Processor System Reset、MicroBlaze Debug Module、AXI Interconnect、Local memory,组成嵌入式软核最小系统。再添加一些对外接口IP,如AXI Quad SPI和AXI GPIO,用于对外初始化配置的接口连接。在SDK工具中编写C语言代码,调用ADI官方提供的库函数,即可实现初始化配置。

图9 Microblaze最小系统Fig.9 Microblaze minimum system

3.2 通道间幅相校准

由于射频收发器AD9371不具备多片本振相位同步功能,本振时钟源通过AD9371管脚输入,经过内部二分频成为两个正交的载频信号,用于正交混频。在这过程中,无法保证每片AD9371的载频初始相位,即每一次初始化AD9371的过程,各通道间的波形相位都随机改变。而初始化完成之后,各通道间的波形相位会保持固定。加上系统中硬件的误差,各通道幅度与相位不能完全保持一致,需要在软件上进行修正。

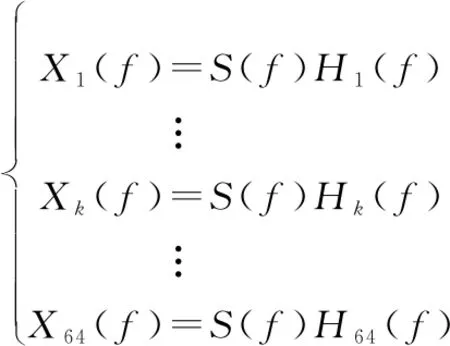

为分析通道幅相误差来源,建立系统信号模型。以发射模式为例,FPGA产生多路相同的信号(),其对应的快速傅里叶变换(fast Fourier transform,FFT)为(),各通道的传递函数为(),各通道对应的输出频率响应()可表示为

(1)

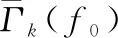

系统多通道间误差来源于(),取第一个通道为参考通道,将其他每个通道与参考通道作比较即可得出通道间的相对误差。按照此思路,对式(1)进行如下变化:

(2)

(3)

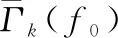

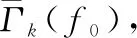

图10 发射通道间幅相校准示意图Fig.10 Schematic diagram of amplitude and phase calibration between transmitting channels

同理,接收通道校准与发射通道校准的计算方法相同,接收通道的校准过程如图11所示。不同于接收校准的是,在系统初始化后,采集各通道实际信号的方式。在接收校准模式中,关闭射频前端的天线单元通道开关,切换到功分网络。主控板持续产生基准信号,经过功分网络后分成64个通道由收发板同时接收。此时,收发板通过接收到的实际信号,计算出各通道接收校准系数,并完成接收通道校准。

图11 接收通道间幅相校准示意图Fig.11 Schematic diagram of amplitude and phase calibration between receiving channels

3.3 DBF实现流程

波束形成是指对空间传感器的采样加权求和以增强特定方向传播波信号抑制其他方向的干扰信号或提取波场特征参数等为目的的空域滤波。DBF权值的计算方法有很多种,本文不作具体介绍,重点讲述本系统的DBF实现流程。

首先,主控板中的FPGA根据方位角和俯仰角计算出DBF权值,并发送到各个收发板中。在发射模式下,主控板将发射波形分发到各个收发板,收发板接收到发射波形之后复制成16路,再依次乘以DBF权值和发射通道校准系数,最后通过JESD204B传输到AD9371。

在接收模式下,收发板中的FPGA将16路原始接收数据依次乘以接收通道校准系数和DBF权值,再将16通道数据进行相加,合成一路,完成第一级接收波束合成。4个收发板的第一级波束合成结果通过Aurora协议传到主控板,并由主控板的FPGA再次进行相加,得到第二级接收波束合成,最后通过AD9371发射通道输出,在频谱仪实时观测接收波束合成结果。图12所示为DBF实现流程图。

图12 DBF实现流程图Fig.12 DBF implementation flowchart

4 实验测试

4.1 通道间幅相一致性测试

通道间幅相一致性测试分为发射通道和接收通道两部分。在发射模式下,系统首先完成发射通道间幅相校准,由于天线阵列模块的工艺误差较小,可直接通过高速示波器观测射频前端模块发射通道输出波形的方式来测试发射通道间幅相一致性。在接收模式下,系统首先完成接收通道间幅相校准,各个接收通道数据通过Aurora协议从收发板发送到主控板中,再通过Vivado软件的集成逻辑分析器(integrated logic analyzer,ILA)工具来观测接收通道的幅相一致性。

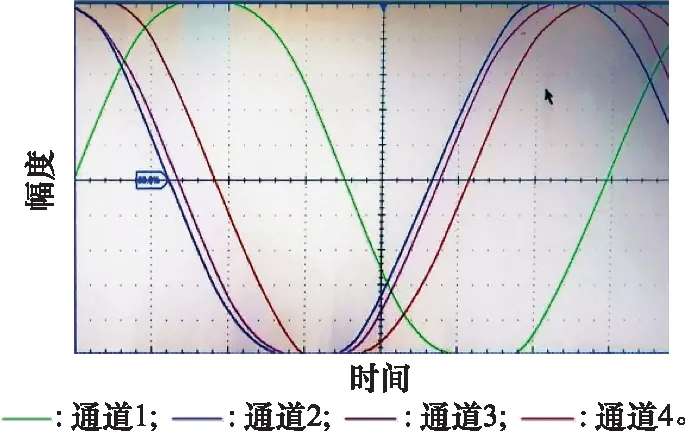

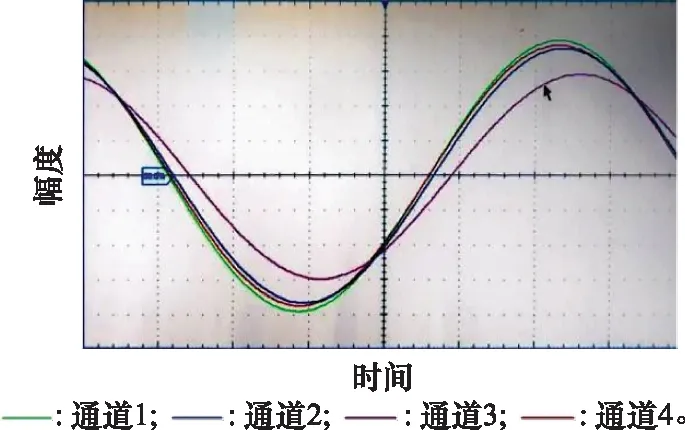

发射通道间的幅相一致性测试,先将系统设置为发射模式,使用输入信号带宽20 GHz以上的多通道高速示波器随机连接射频前端的4个发射通道输出端口。图13~图15均为多通道高速示波器的测示结果显示界面,图中的横纵轴分别表示时间和信号幅度。图13显示了发射通道间幅相校准前的射频前端模块发射通道输出波形,此时收发板的各个AD9371中频本振相位不一致,加上收发板和射频前端模块的器件误差和布线误差,使得发射波形幅相一致性差。图14显示了经过系统发射通道间幅相校准之后的射频前端模块发射通道输出波形,能明显观察到发射波形的幅相一致性已经得到来很大改善。由于射频前端中用于校准的功分网络存在布线误差,经过在线幅相校准之后,还需要通过在FPGA中将发射数据再次乘以补偿系数,并同时观测示波器进行手动幅相误差补偿。图15显示了发射通道经过手动幅相误差补偿之后的射频前端模块输出波形。

图13 发射通道间幅相校准前Fig.13 Before amplitude and phase calibration between transmitting channels

图14 发射通道间幅相校准后Fig.14 After amplitude and phase calibration between transmitting channels

图15 发射通道间幅相误差补偿后Fig.15 After amplitude and phase error compensation between transmitting channels

表3所示为与参考文献[22]的幅相误差对比结果。实验表明,本文的DBF发射通道一致性效果更好。

表3 发射通道间幅相误差补偿结果对比

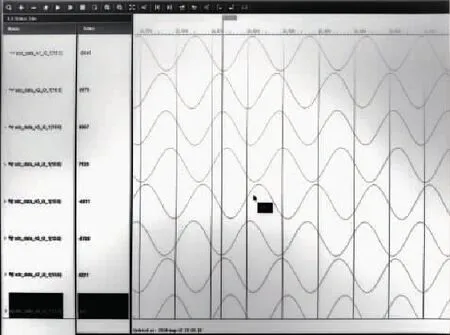

接收通道间的幅相校准,可以在暗室中进行测试,在天线阵列的远场法线方向上放置标准喇叭天线并发射信号源,由本系统接收。通过Vivado的ILA观察接收通道间幅相校准后的波形。

图16显示了ILA窗口中接收通道间幅相校准前的原始接收波形,图17显示了接收通道间幅相校准之后的波形。可以看出,经过接收通道间幅相校准之后的各个通道接收波形幅度与相位基本能保持一致。

图16 接收通道间幅相校准前Fig.16 Before amplitude and phase calibration between receiving channels

图17 接收通道间幅相校准后Fig.17 After amplitude and phase calibration between receiving channels

4.2 发射波束方向图

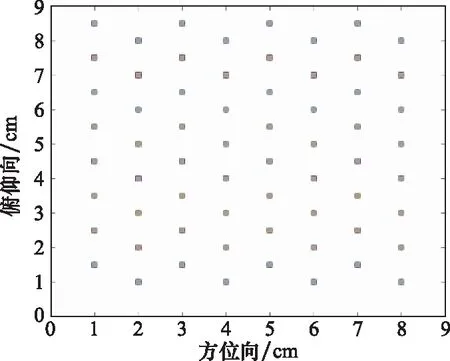

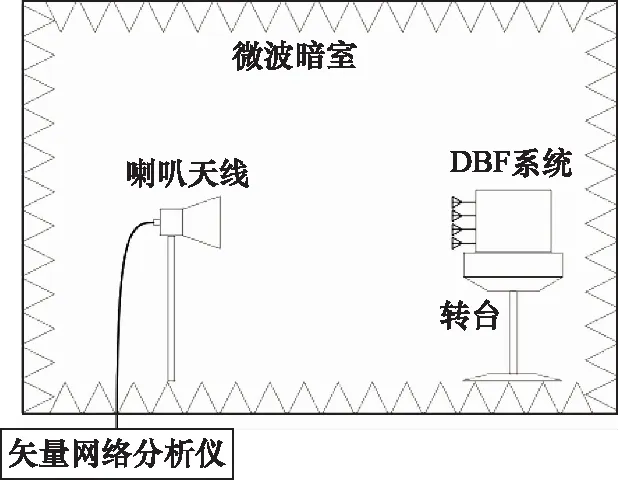

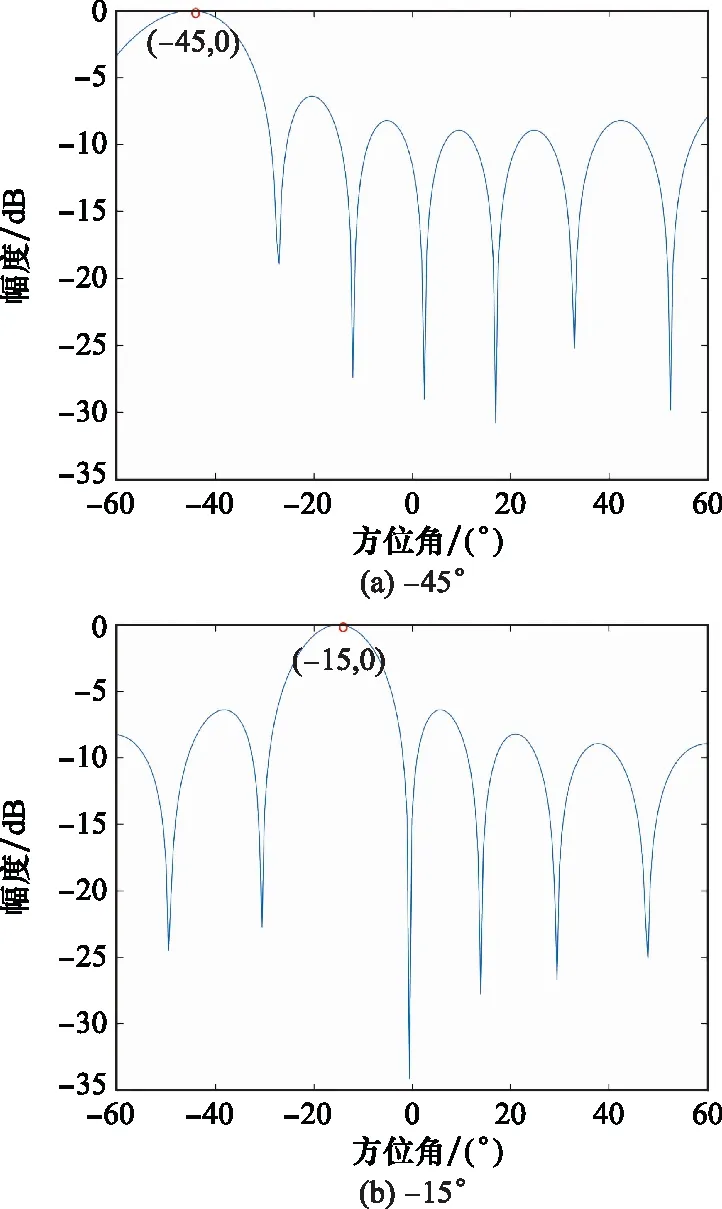

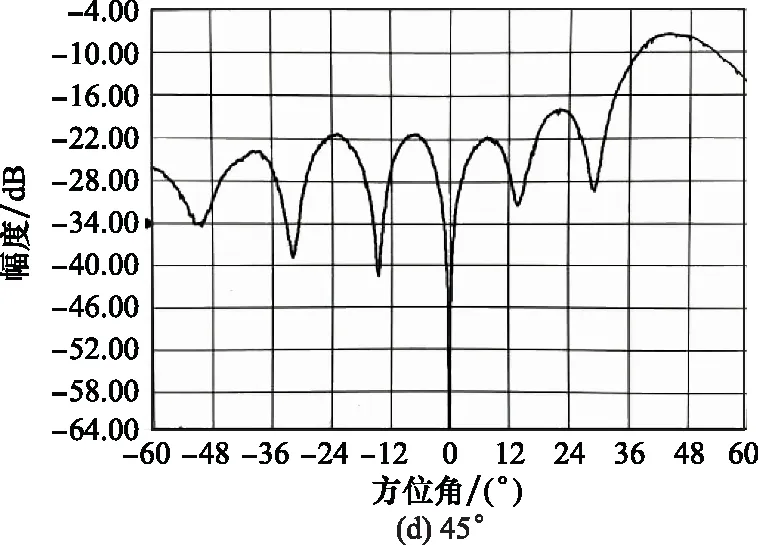

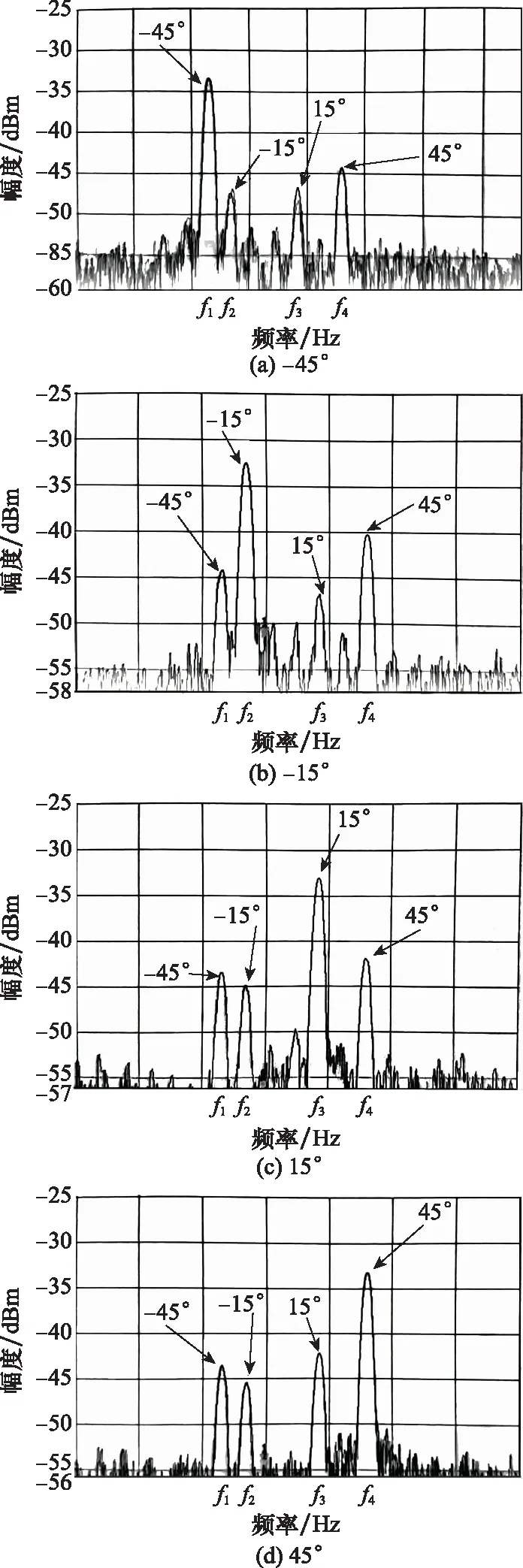

本系统的测试天线采用相邻阵元错开排列的64阵元二维平面天线阵列,发射通道与接收通道时分复用同一个天线阵列。图18为二维平面天线阵列的阵元排列示意图。图19为本系统的暗室测试环境。系统机箱放置于转台上,转台可通过电脑远程控制俯仰角与方位角。在天线阵列法线方向的远场距离处放置喇叭天线进行接收,喇叭天线外接矢量网络分析仪测出信号功率大小。矢量网络分析仪的纵坐标显示接收信号功率大小,横坐标表示时间。随着转台从-60°转至60°的方位角,矢量网络分析仪也同时进行接收测试,其横坐标的时间就对应了转台的角度。在此过程中,本系统的DBF权值保持不变,而系统机箱的方向随着转台而改变。图20分别显示了-45°、-15°、15°和45°方位角指向权值时的软件仿真单波束方向图。图21分别显示了-45°、-15°、15°和45°方位角指向权值时的实测发射单波束方向图。可以看出,本系统的实测发射单波束方向图与仿真结果十分近似。在多波束发射模式下,同时产生频率为、、、的4个波束,4个波束对应的方位角分别指向-45°、-15°、15°和45°,由喇叭天线接收,并通过频谱仪显示各个波束的幅值。图22显示了被测天线对喇叭天线的方位指向角分别为-45°、-15°、15°和45°时,喇叭天线接收到的信号频谱。可以看出,在本系统的发射数字多波束形成模式下,波束能在指定方向上实现正确指向。

图18 天线阵元排列示意图Fig.18 Schematic diagram of antenna array element arrangement

图19 暗室测试环境Fig.19 Darkroom test environment

图20 不同指向权值的单波束仿真方向图Fig.20 Single beam simulation pattern with different pointing weights

图21 不同指向权值的发射单波束实测方向图Fig.21 Measured directional patterns of transmitting single beams with different pointing weights

图22 天线不同方向时多波束发射频谱Fig.22 Multi-beam emission spectrum when antennas are in different directions

5 结 论

小型化设计在无人机、导弹和微纳卫星平台上尤为重要,大规模天线阵列的DBF系统在功耗与体积上具有很大的优化空间。本文提出了一种新的DBF架构设计,通过射频收发器AD9371的高集成特性,以高中频架构为思路,完成了高精度、高性能、小型化、低功耗和Ku工作波段的全数字多波束形成系统设计。实验结果表明,本系统能实现精确的收发通道幅相校准和灵活的全数字波束形成,并具备很高的性能,验证了本文设计的可行性与工程价值。