基于FPGA云的实时图像处理在线验证平台设计

黄继业,刘鑫,董哲康

(杭州电子科技大学电子信息学院,杭州 310018)

0 引言

高清视频编码、传输技术的快速发展对传统图像处理系统的实时性提出了更高的要求,现场可编程门阵列(Field Programmable Gate Array,FPGA)技术在视频、图像处理领域的应用愈发广泛[1-2]。如何在行业标准不断变化、算法快速更新迭代的大背景下,实现对基于FPGA的图像处理算法的快速验证成为行业发展关键之一。算法快速验证平台通过提供通用的测试环境,允许用户在硬件条件未达到的情况下,以FPGA实现目标算法的硬件逻辑设计,评估算法的效果与可行性[3]。

FPGA云基于FPGA 即服务(FPGA as a Service,FaaS)技术,其作为公有云基础设施的一部分,向用户提供基于FPGA的云服务[8-9],具备强大的计算力、良好的迁移性和使用灵活性,近年来被广泛应用于各类计算加速系统[10-12]。对于图像处理算法验证这一典型的计算密集型应用场景,FPGA 云技术具有极高的适用性。

本文针对FPGA 图像处理算法快速验证需求,构建基于FPGA云的实时图像处理在线验证平台,通过设计通用FPGA算法测试平台、定义统一的虚拟用户接口,抽象测试平台底层逻辑设计,简化外设架构,使用户能够专注于算法设计和验证本身,降低开发成本,缩短研发周期,提高验证效率。

1 在线验证平台软硬件架构设计

1.1 平台总体设计

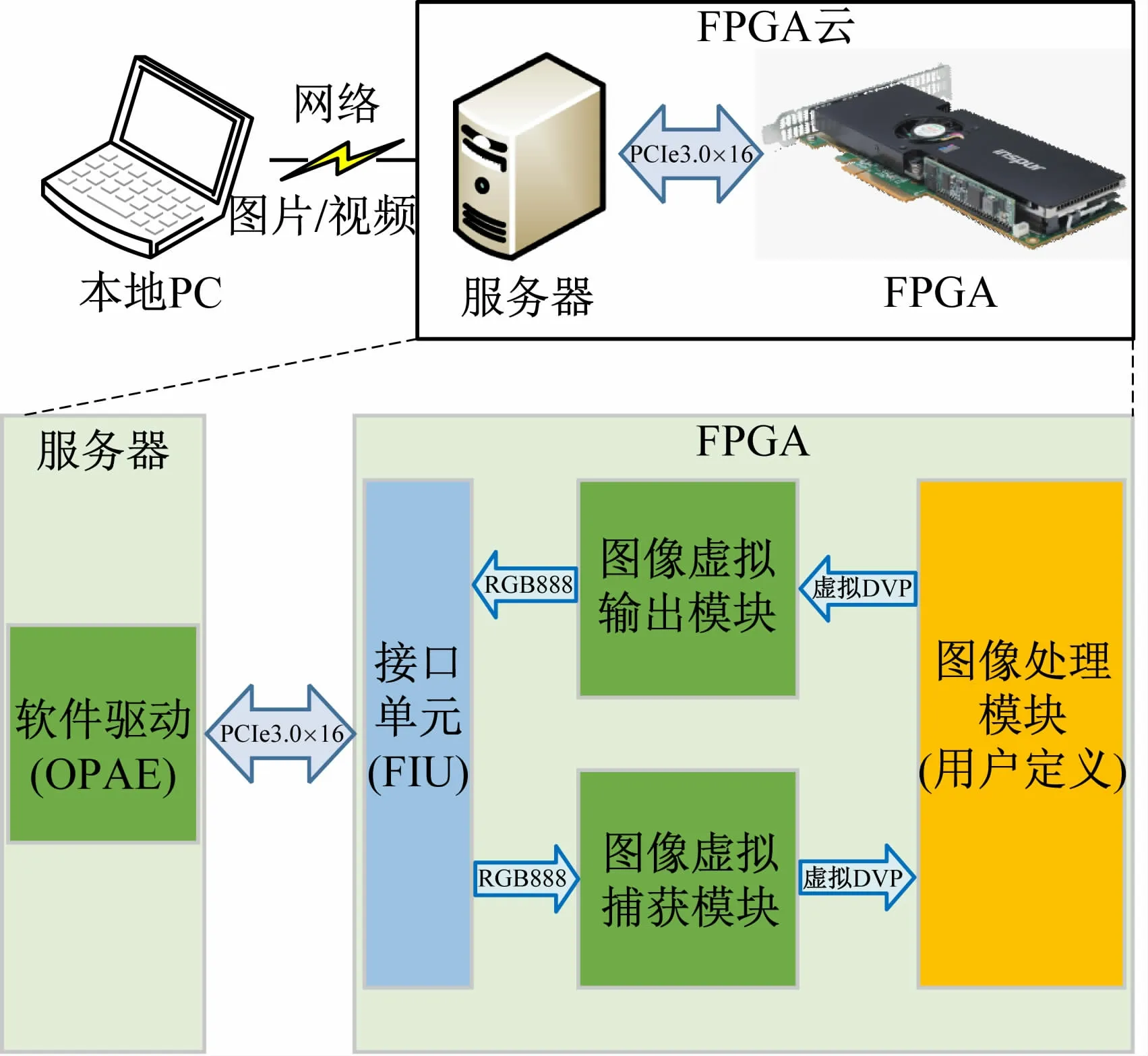

传统图像处理验证平台以高速相机实时采集数据作为输入,以显示器显示图像作为输出,通过高速硬件接口进行数据传输;本文提出的基于FPGA 云的实时图像处理在线验证平台,以图片或视频作为虚拟输入、输出,通过虚拟的数字视频端口(Digital Video Port,DVP)进行模块间数据交互,二者对比如图1 所示。

图1 2种验证平台对比

在线验证平台搭建基于具有FPGA计算加速功能的云服务器。硬件逻辑主要包括图像虚拟捕获模块、图像虚拟输出模块以及虚拟DVP 接口3 部分。软件驱动基于Intel 开源可编程加速引擎[13](Open Programmable Accelerator Engine,OPAE),实现用户应用与FPGA逻辑间的高效数据交互。在线验证平台总体结构如图2 所示。

图2 基于FPGA云的实时图像处理在线验证平台总体结构

在线验证平台利用软件驱动将服务器上用户自定义图片或视频数据通过PCIe3.0 ×16 高速数据接口写入FPGA。FPGA接口单元(FPGA Interface Unit,FIU)接收数据,转换为核心缓存接口协议(Core Cache Interface Protocol,CCI-P)格式向后级模块发送。图像虚拟捕获模块以RGB888 格式捕获图像数据进行帧缓存,存满1 帧后通过虚拟DVP接口发送至图像处理模块。图像处理模块执行用户自定义算法进行数据处理,处理结果经虚拟DVP 接口、图像虚拟输出模块、FPGA接口单元、PCIe3.0 ×16 接口返回服务器。

本文设计的平台采用阿里云弹性计算服务(Elastic Compute Service,ECS)服务器FPGA 计算型F1 实例实现,该实例搭载Intel Arria10 GX1150FPGA,板载8 GB DDR4 内存,以PCIe3.0 ×16 高速数据接口实现服务器与FPGA 之间的高速数据传输,满足本设计在资源和带宽方面的需求。

1.2 FPGA逻辑设计

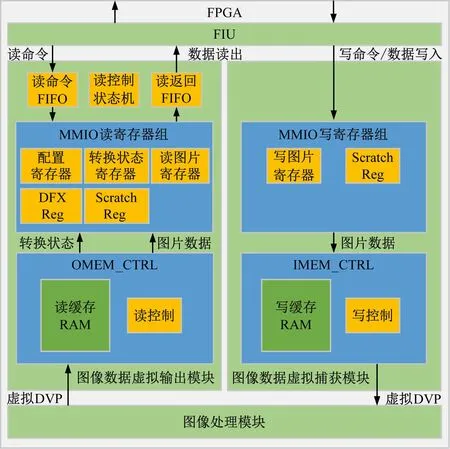

FPGA逻辑设计基于FIU,FIU是Intel定义的CPU与FPGA 加速功能单元(Accelerator Functional Unit,AFU)间的通信接口,负责CPU 侧PCIe3.0 ×16 接口与AFU侧CCI-P接口之间的数据格式转换。FPGA逻辑主要包含图像虚拟捕获模块,图像虚拟输出模块和虚拟DVP用户接口,总体设计架构如图3 所示。

于是康师傅根据这个情况因地制宜,帮助当地建立了十几万亩的环境友好蔬菜基地。仅此一个项目,就带动贫困人口6000人,使贫困农民人均年增收近万元。康巴诺尔基地生产的蔬菜既新鲜又安全,深受消费者喜爱,满足了当前消费者消费升级的需求。

图3 FPGA逻辑总体设计架构

1.2.1 图像虚拟捕获模块

本文的图像虚拟捕获模块实现图像数据捕获,帧缓存,以及虚拟DVP 接口输出时序控制,如图3 右侧框图所示。

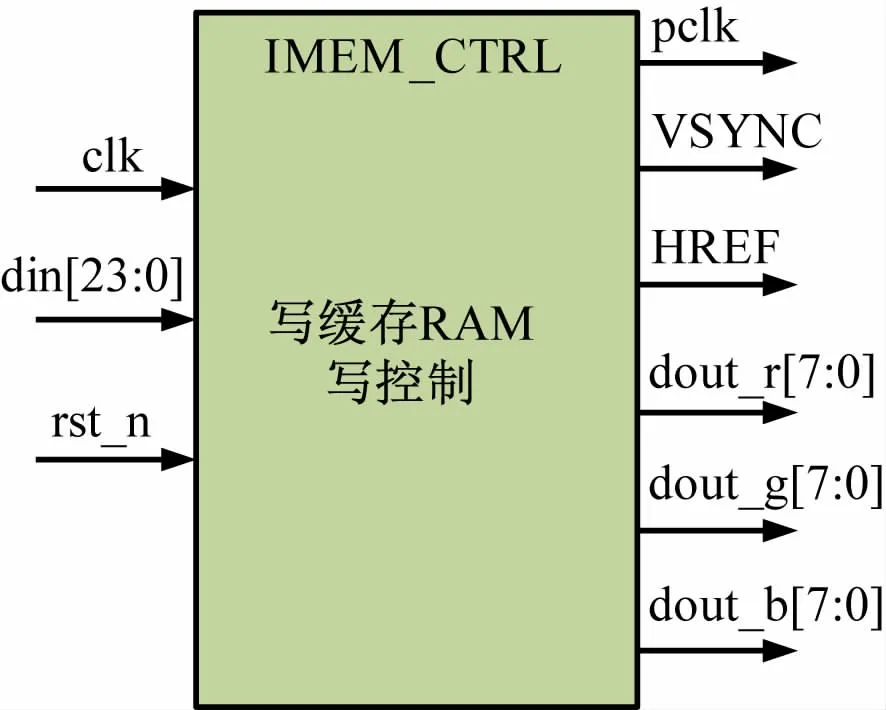

CPU 对FPGA 数据写入基于BAR 寄存器,通过OPAE C应用程序编程接口(Application Programming Interface,API)中的fpgaWriteMMIO64 函数实现。对应的,在图像虚拟捕获模块中,设置写图片寄存器和Scratch Reg,用于捕获图像数据和写测试命令。寄存器位宽64 bit,使用低24 bit 进行数据传输,系统工作频率可调,默认100 MHz,默认带宽300MB/s。此外,设计IMEM_CTRL 子模块进行帧缓存以及虚拟DVP输出时序控制,IMEM_CTRL子模块如图4 所示。

图4 IMEM_CTRL模块

IMEM_CTRL模块内置24 位宽,深度为640 ×480的写缓存RAM,当检测到写数据请求后开始连续捕获图像数据进行帧缓存,写满1 行后以HREF 信号进行行同步,写满1 帧(640 ×480)后以VSYNC 信号进行帧同步,开始向图像处理模块连续发送1 帧数据。限于研发时间成本,本平台写缓存RAM使用片上BRAM实现,但此设计模式完全适用于容量更大、带宽更高的DDR4 实现,此结论已在另一Xilinx平台上得到验证。

图像虚拟捕获模块与后级模块通信采用虚拟DVP接口。目前常见的CMOS 相机接口为DVP 接口和移动产业处理器接口(Mobile Industry Processor Interface,MIPI)2 种。DVP 是并行数据接口,支持8/10/12bit数据传输,像素时钟极限频率在96 MHz 左右,传统使用中存在易受干扰、信号完整性差问题。MIPI是MIPI联盟发起的为移动应用处理器制定的开放标准规范,采用低压差分串行传输,抗干扰能力强。

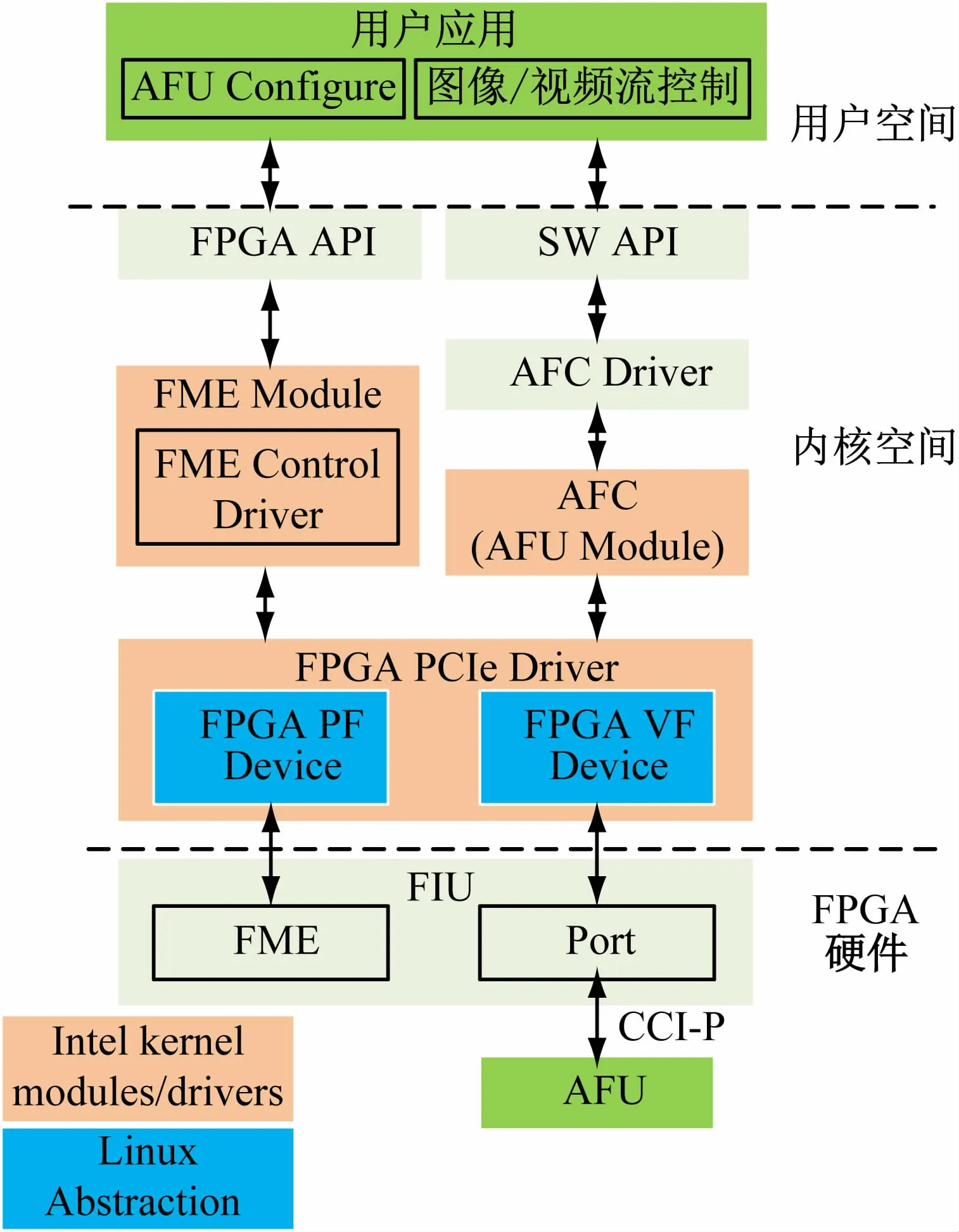

本文设计提供给用户的时钟默认为100 MHz,接口时钟频率不受接口限制,且由于是虚拟接口,对接口抗干扰性要求不高,因而采用时序更为简单的DVP时序及接口。主要使用DVP 接口的HREF、VSYNC、PCLK、DATA共4 个信号。由于标准DVP接口只有1路DATA信号用于数据传输,而本文设计需要同时传输RGB的3 通道共24 bit数据,因而额外增加2 路数据通路。虚拟DVP接口简化时序图如图5 所示。

图5 虚拟DVP输出时序

1.2.2 图像虚拟输出模块

本文的图像虚拟输出模块接收图像处理结果进行帧缓存,收到CPU读命令后开始输出图像数据,如图3左侧框图所示。

CPU通过OPAECAPI 中的fpgaReadMMIO64 函数向FPGA发送读命令并从指定寄存器读出数据。读命令包括读图像数据命令和其他命令,读返回数据包含调试输出信息和图像数据等。为避免命令冲突,同时实现对读返回数据流的控制,设计预读式读命令FIFO和读返回FIFO对读命令和读返回数据进行缓存。设置配置寄存器、转换状态指示寄存器、读图片寄存器、调试寄存器(DFX)以及Scratch Reg用于平台配置、返回处理状态、返回图像数据、输出调试信息以及读测试。

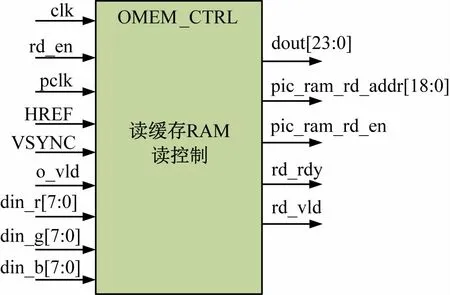

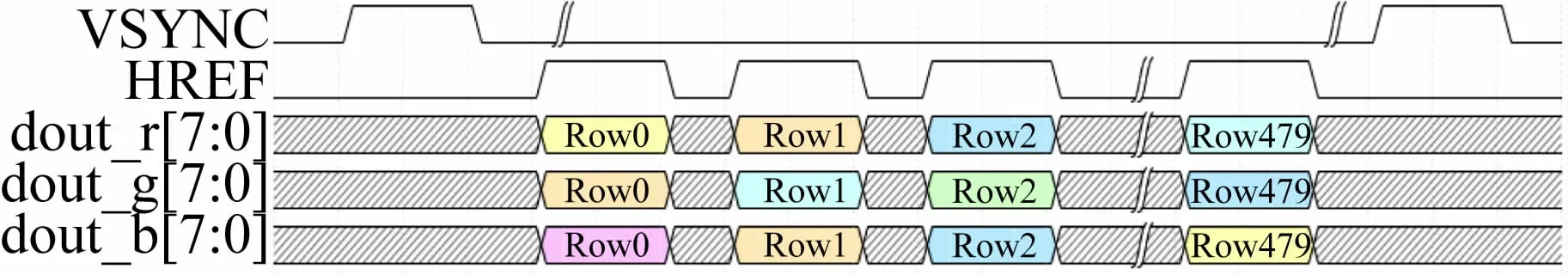

设计的OMEM_CTRL 子模块接收处理后图像数据并实现读时序控制,如图6 所示。OMEM_CTRL 模块控制读缓存RAM的写使能信号,将1 帧图像数据连续存入RAM,当1 帧数据存满后将处理状态指示输出信号置为1。模块输入采用DVP时序,简化时序图如图7 所示。图像虚拟输出模块工作状态受有限状态机(Finite State Machine,FSM)控制。其工作过程为FSM启动后进入命令等待状态,接收到读命令后判断是否为读图像数据命令:若是,则检查图像处理模块处理状态,处理完成后输出图像数据;若非,则根据命令中包含的寄存器地址(Memory Map I/O,MMIO)直接输出对应寄存器中所含信息。状态转移图如图8 所示。

图6 OMEM_CTRL模块

图7 虚拟DVP输入时序

图8 图像虚拟输出模块状态转移图

各状态含义:0000 为IDLE;0001 为接收并解读命令;0010 为获取非图像数据;0100 为获取图像数据;1000 为输出图像或其他信息。

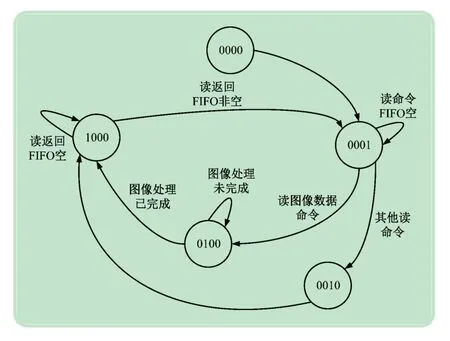

1.3 基于OPAE的FPGA PCIe设备驱动框架

OPAE将底层FPGA 硬件资源进行抽象,在用户空间为软件开发人员提供通用的API;在Linux内核空间实现完整的FPGA PCIe 设备驱动;在FPGA 硬件上实现FIU单元,为用户提供CCI-P 接口。OPAE 框架下FPGA PCIe设备驱动架构如图9 所示。

图9 FPGAPCIe设备驱动框架

CPU 将FPGA 视为PCIe 设备,以FPGA PCIe Driver驱动部署在FPGA 硬件上的FPGA 管理引擎(FPGA Management Engine,FME)和AFU。其中,FME负责向CPU提供AFU 的错误报告、资源报告以及其他运行信息,与内核空间的FPGA PCIe Driver 直接交互;AFU是加速功能单元,允许用户自定义,对应本文FPGA逻辑设计部分,通过Port 与内核驱动交互。AFU内置可配置MMIO 地址空间,CPU 通过BAR 寄存器对其进行访问。

基于上述架构,本平台在用户应用层实现了AFU快速配置和图像/视频流控制。配置功能基于OPAE C API,实现枚举AFU、开启AFU、Map MMIO、关闭AFU等操作。图像/视频流控制部分基于通用C API,实现图像数据的存取、预处理、发送/接收图像数据。

2 实验验证

2.1 彩色图片高斯滤波实验

实时图像处理系统在获取图像过程中容易受干扰而引入高斯噪声,表现为幅值强度按照高斯分布函数分布在整个图像中。高斯滤波器作为一种低通线性平滑滤波器,以中心像素点及其邻域像素的线性组合取代中心点像素值,对高斯噪声有很好的抑制作用。

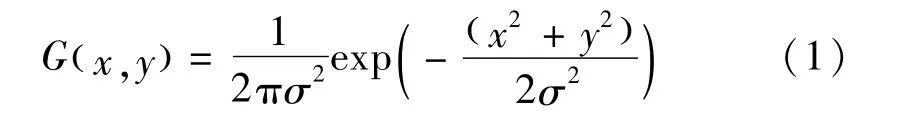

二维高斯分布函数数学定义如下[14]:

式中:x为二维坐标系横坐标;y为二维坐标系纵坐标;σ为高斯函数的标准差;G(x,y)为坐标(x,y)处的高斯函数值。

生成高斯滤波模板,需要将其离散化[15]:

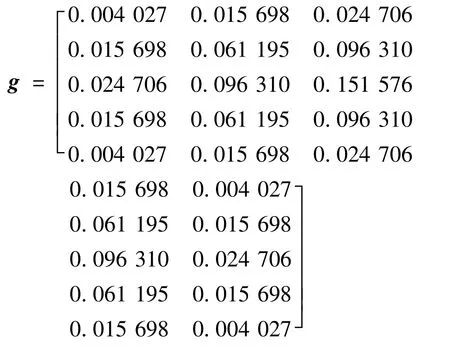

式中:r为高斯滤波模板的半径,通常取为偶数,则模板尺寸为2r;i为模板横坐标,i∈N,i≤2r;j为模板纵坐标,j∈N,i≤2r;G(i,j)为坐标(i,j)处的高斯函数值。对于5 ×5 模板,r=2,若取σ =1.05,根据式(2)计算得到的高斯系数矩阵:

对上述g矩阵进行归一化和取整处理后得到高斯滤波模板系数矩阵:

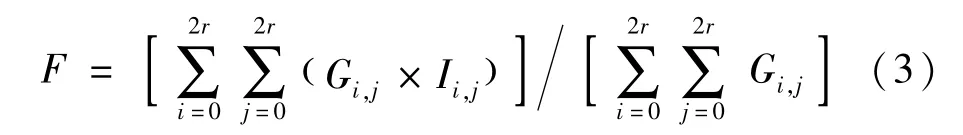

此时,高斯滤波算法可表示为

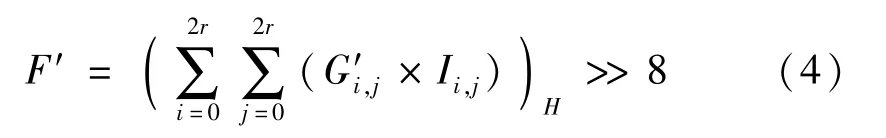

式中:r=2;Gi,j为G第i行第j列元素;Ii,j为5 ×5 像素矩阵I 第i行第j列元素;F为高斯滤波值。使用FPGA实现时需要对高斯滤波模板进行量化。设上述G的分子矩阵为G′,分母近似取为256,则式(3)可改写为

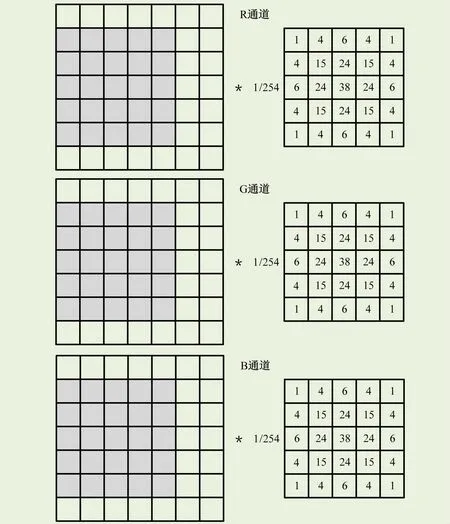

式中:代表矩阵G′第i行第j列元素;F′为十六进制表示的高斯滤波值;H表示十六进制;>>表示右移运算。本文实验根据式(4)进行彩色图片高斯滤波实验,使用5 ×5 模板,对测试图片的RGB的3 通道数据分别进行高斯滤波,处理后通过软件驱动重新融合RGB数据并写入新图片。彩色图像高斯滤波实验原理如图10 所示。

图10 彩色图像高斯滤波原理

2.2 彩色图片高斯滤波实验结果分析

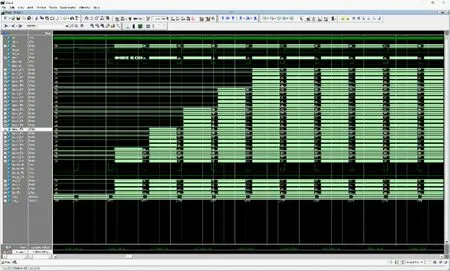

高斯滤波算法实现包括方形窗生成和中心像素点计算2 步。本文实验在对每个通道进行高斯滤波时,使用shift_ram,通过缓存5 行数据的方式生成5 ×5 方形窗[16],该过程的QuestaSim仿真结果如图11 所示。

图11 5 ×5方形窗QuestaSim仿真结果

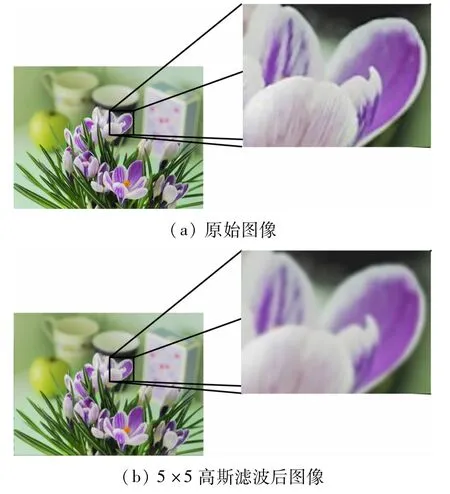

图12 为高斯滤波实验前后的结果对比,对前几行像素数据,由于邻域像素不完整,无法完成高斯滤波计算,故而在图12(b)高斯滤波后图像底部可见明显黑色线条。为便于展示实验结果,将高斯滤波前后图片进行局部放大,对比原始图像与经高斯滤波后的图像,前者花瓣边缘明显,线条清晰,后者整体上较前者更为模糊,细节不明显,达到了高斯滤波的预期效果。

图12 实验结果对比图

3 结语

本文设计了一个基于FPGA云的实时图像处理在线验证平台,完成了FPGA 图像处理算法通用测试环境搭建。相较于传统验证模式,基于FPGA 云的在线验证平台简化了外设架构,使用灵活性更高。通过彩色图像高斯滤波实验表明,本文设计的平台能够快速整合、验证用户自定义图像处理模块,提高图像算法研发和验证效率;对亟需验证FPGA 图像处理算法而又不具备验证条件的工程研发人员,具有一定使用价值。同时,也可作为高校复杂图像处理实验教学平台。