基于负载跟踪技术的低漏失大电流LDO 的设计

茅欣彧 ,汪西虎, ,姚和平, ,闫兆文,

(1.西安邮电大学 电子工程学院,陕西 西安 710121;2.上海电子线路智能保护工程技术研究中心,上海 201202;3.上海维安电子有限公司,上海 201202)

便携式电子产品在当代生活中有着广泛需求,例如手机、智能手机、PAD、MP3 等产品。随着电子产品性能的进一步提升,LDO 作为它们的供电电源需具有更为宽泛的输入电压和更小的漏失电压以提高工作效率,在中低频需具有较高的电源抑制比(Power Supply Rejection Ratio,PSRR)以消除前级功率放大器产生的电池电压纹波,保证良好的音质。针对以上要求,本文设计了一款低漏失高稳定性高PSRR 的LDO。

LDO 由多级放大器级联而成,环路中存在多个零极点,位于LDO 输出端的极点动态变化影响环路相位裕度,如何保持环路稳定是设计关键[1]。文献[2]采用ESR 补偿功率管输出极点,通过密勒补偿对运算放大器内部极点进行补偿,但ESR 补偿只能在固定范围内进行补偿,密勒补偿电容面积大,低频PSRR 较低。文献[3]通过一种电流模式方法,建立左半平面零点,抵消低频极点,但会消耗额外的电流,增加功耗。

本文采用负载跟踪技术对环路进行补偿。通过高精度采样网络,控制工作在深线性区的MOS 管栅极电压,将该MOS 管等效为可变电阻,与频率补偿电容串联接入环路,对动态极点进行补偿。同时设置负载电流监测电路,精准控制MOS 管等效电阻阻值。为进一步提高环路稳定性,缓冲级采用阻抗衰减缓冲器,降低缓冲级输出阻抗,在单位增益带宽积内具有足够大的相位裕度。

1 传统的LDO 结构

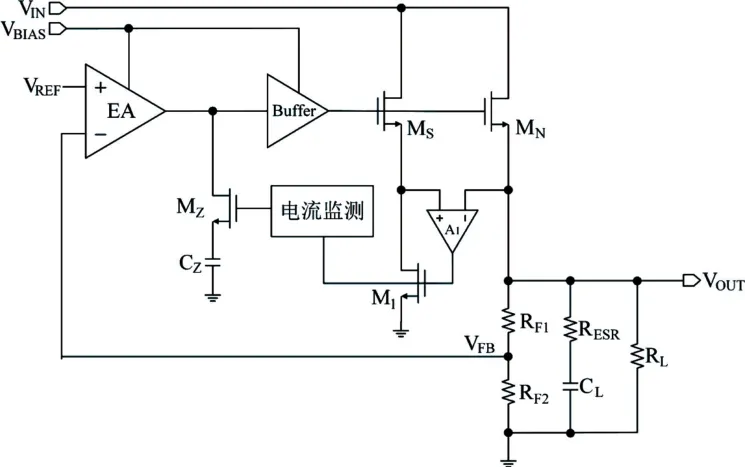

图1 为传统LDO 结构,由基准电压(VREF)、误差放大器(Error Amp,EA)、缓冲器(Buffer)和功率管PMOS 组成,电阻RF1和RF2为反馈电阻,RL和CL分别为负载电阻和负载电容,RESR为ESR 电阻。在结构形式上,LDO 属于电压串联负反馈电路,具有输出电压稳定、输出电阻小、驱动能力强的特点[4-5]。反馈电压VFB与基准电压经过误差放大器进行比较,通过调整控制功率管栅极电压,对输出电压VOUT和负载电流IOUT进行控制。由于内阻和寄生电容的存在,环路中的极点分别位于误差放大器输出端、功率管栅极和LDO 输出端:

图1 传统LDO 结构Fig.1 Traditional LDO structure

式中:rOEA是误差放大器输出端的输出阻抗;CBuf是缓冲器输入端等效电容;rOBuf是缓冲器的输出阻抗;CP是功率管栅极的输入电容;rout是LDO 输出端的等效电阻。为了提高环路的稳定性,要求rOEA和CP都要很小,保证极点P1和P2处于远离单位增益频率的高频位置。然而随着rOEA的减小,环路增益下降,LDO 电压输出精度受到影响;同时,减小CP需要减小调整管的尺寸,这将使得LDO 不能满足低漏失、驱动大负载电流的特性需求。

2 电路设计

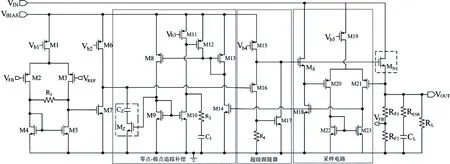

本文设计的低漏失大电流LDO 采用负载跟踪技术。主要由以下模块构成:误差放大器、阻抗衰减缓冲器、电流监测模块、动态零点补偿模块、采样管和功率管,电路结构如图2 所示。

图2 负载跟踪补偿方案的LDO 结构Fig.2 LDO structure of load tracking compensation scheme

在此设计中,采用N 型MOS 作为功率管,VIN为其供电,相较于文献[6]使用电荷泵为NMOS 栅极供电,该方法节约面积,减小电路冗余度,可获得低漏失电压、大输出电流特性。补偿方案采用新颖的负载跟踪补偿方案,同时添加负载电流监测电路,保证重载下动态零点更好地追踪输出极点;采用阻抗衰减缓冲器进一步减小缓冲器的等效输出电阻。

2.1 低漏失高稳定性LDO 电路设计

本文提出的LDO 结构图,由误差放大器、采样电路、负载电流监测电路和零点-极点跟踪补偿电路组成,如图3 所示。

图3 提出的LDO 具体电路Fig.3 The proposed LDO specific circuit

误差放大器采用两级运放结构,相比于折叠式运放与套筒运放,两级运放的功耗和噪声较低[7]。第一级采用差分放大器,NMOS 和PMOS 作为输入对管都可以确保合适的工作点,但由于误差放大器中差分输入对管的闪烁噪声在LDO 输出噪声中占主导地位,选择闪烁噪声更小的PMOS 作为输入级[8]。在中频段,即误差放大器主极点和带宽之间的频段处,主极点对PSRR 造成影响,PSRR 在主极点处开始衰减,且PSRR 随着频率的增加越来越差。为保证该频段处的PSRR,将极点PEA1推离原点。

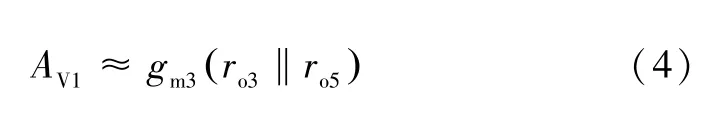

传统PMOS 管输入差分放大器增益为:

输出端极点为:

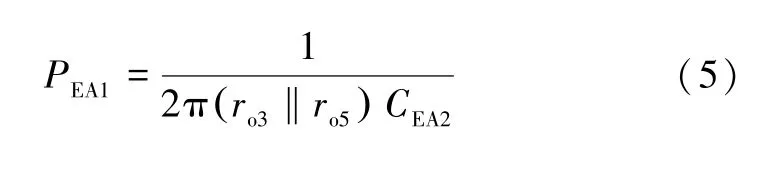

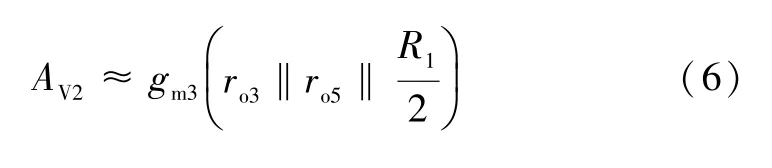

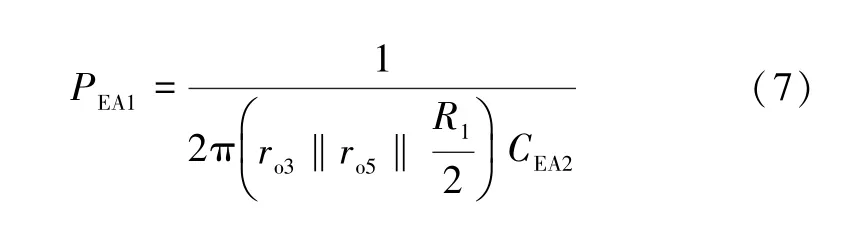

输入对管M2、M3 漏极间跨接电阻R1,该级增益可表示为:

第一级运放输出端极点变为:

其中,R1/2 远小于ro3,R1/2 远小于ro5,运放输出端变为低阻节点,极点PEA1远离原点。该方式相较于传统的前馈纹波消除技术降低功耗[9],不需要大的带宽,避免对频率补偿造成影响。相较于主极点处于LDO 输出端,更利于环路补偿[10]。如图4 所示,PSRR 会在较高的频率处开始衰减。

图4 主极点对PSRR 的影响Fig.4 Influence of primary pole on PSRR

第二级为共源极放大器,输出为高阻节点,为环路提供主要增益,放大输出摆幅。缓冲器采用阻抗衰减跟随器结构,M17 与源极跟随器M16 输出并联形成负反馈结构,有效减小了源跟随器的输出电阻rOBuf[11]。

当负载电流增加时,源跟随器M16 输入电压恒定,输出电压增加时,流过M16 的电流增大,使得R4两端的电压增大,最终M17 管的电流增加,进一步减小了源跟随器的输出电阻。需要强调的是,R4阻值要足够大以保证负反馈M17 管在不同负载条件下都处于导通状态。源跟随器的输出阻抗为:

阻抗衰减跟随器的输出阻抗为:

由式(8)、(9)对比可知,阻抗衰减跟随器可以大大降低缓冲级的输出阻抗rOBuf。

负载跟踪补偿电路由采样电路、补偿电路、负载电流监测电路构成。采样电路由采样管MS、功率管MN、M19~M23 管构成的运放和尺寸相同的M14、M18 管组成。运放和M18 管为正反馈增益buffer,钳位MS和MN的源极电压,因此MS和MN的三端电压均相等。该种电流采样结构与常用的电阻网络相比,温漂小,采样精度高,采样电流IOUT_S由下式给出:

式中:(W/L)Ms和(W/L)MN分别为采样管MS和功率管MN的宽长比。

电流镜将采样电流IOUT_S拷贝到M8~M9 支路,以控制MOS 管MZ的栅极电压,MZ和CZ产生的零点,其中M8~M9 支路电流I8,9为:

控制MZ管栅极电压为:

补偿过程中,MZ管等效电阻RZ与负载电流的关系可结合式(10)~(12)得出:

由式(13)可看出,RZ与负载电流成反比,所得零点可跟踪功率管输出端极点进行补偿。

M11~M13 管组成负载电流监测电路,通过电流镜拷贝M10 上采样电流,与偏置电流比较来控制M12,使得MZ栅极电压缓慢变化,更好地控制动态零点。

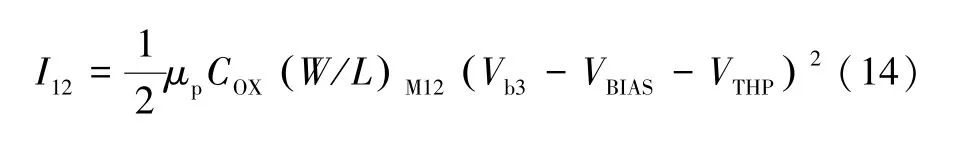

I12上的电流为:

式中:μP为电子迁移率;COX为栅氧化层电容;VTHP为PMOS 管的阈值电压。负载电流监测环路中M13 的栅端极点PM13为:

式中:gm13为M13 的跨导;CM13为寄生电容。随着M12 抽走部分电流,M13 的跨导减小,极点PM13会随负载电流增大进入带宽内,设置R3、C1构成零点对其进行补偿,扩展采样电流监测环路带宽,提高响应速度。

2.2 稳定性分析

图5 为设计LDO 的等效小信号模型。

图5 LDO 小信号等效电路Fig.5 The small signal equivalent circuit

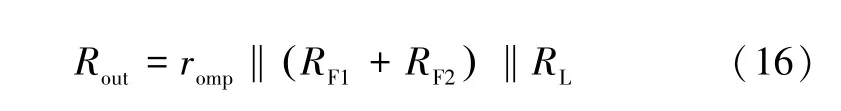

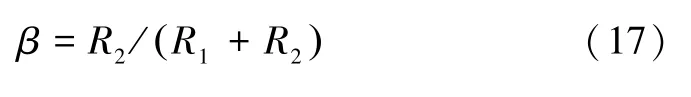

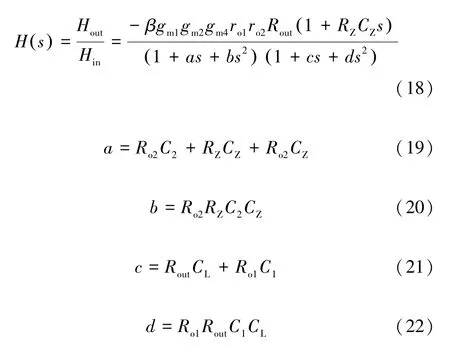

LDO 主环路的小信号等效模型中gm1、gm2和gmn分别为差分放大器、共源极放大器、缓冲级和功率管MN的跨导,Rout为输出端等效电阻。

β为反馈系数:

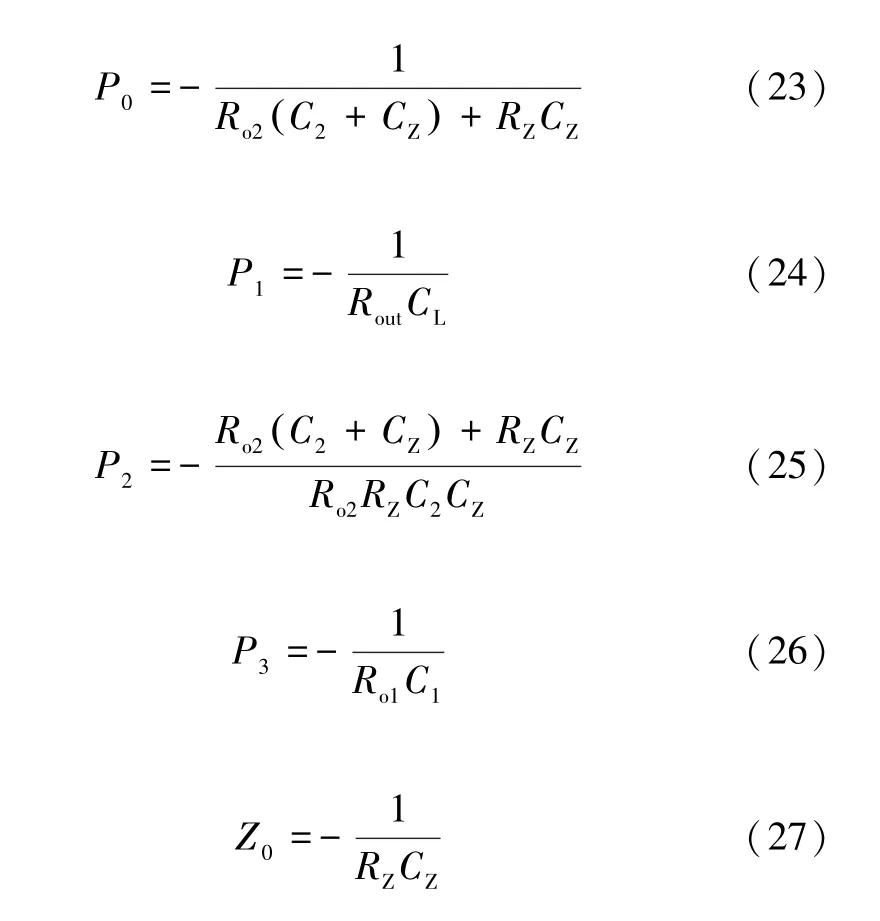

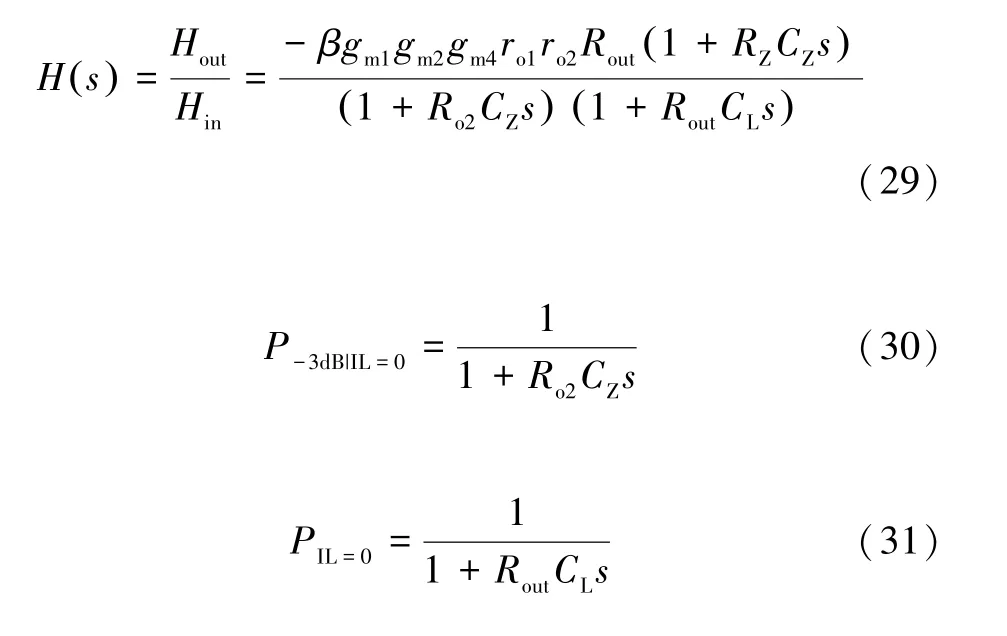

如前节所述,超级跟随器的输出为低阻节点,且在LDO 的整个负载范围内均远高于带宽,因此在下面环路稳定性的讨论中忽略此处极点。环路传输函数极点推导得出:

由式(18)可知,环路增益为负,输出电压调节为负反馈。此外,分母为四阶多项式,即环路中存在一个零点与四个极点:

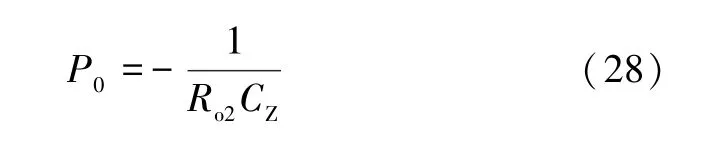

由于C2远大于CZ,Ro2远大于RZ,极点P2在单位增益带宽外,对环路稳定性没有影响。同样,由于Ro1很小,使得极点P3在带宽之外可以忽略,极点P0可近似为:

式(18)中H(s)可近似为:

式(30)、(31)分别为H(s)的主极点和次极点。

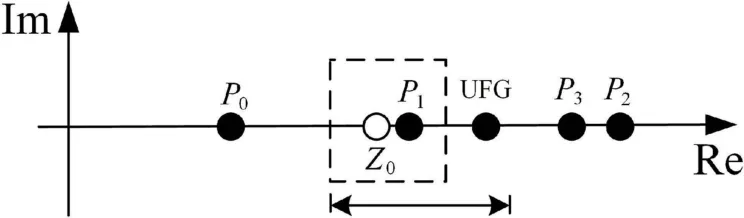

环路中零极点位置如图6 所示。

图6 环路零极点分布Fig.6 Loop zero pole distribution

由于LDO 设计的最大负载电流为500 mA,Rout变化单位较大,次极点位置动态变化。因此,需要在不同负载电流条件下研究环路稳定性。重载时,Rout非常小,极点P1处在高频段,环路近似于单极点系统。空载时,P1向低频移动,零点Z0对其进行补偿,环路保持稳定。

3 仿真结果及分析

电路采用0.18 μm CMOS 工艺,基于Cadence 仿真平台对电路性能进行仿真验证。图7 为LDO 的版图设计。

图7 LDO 版图设计Fig.7 The design of LDO layout

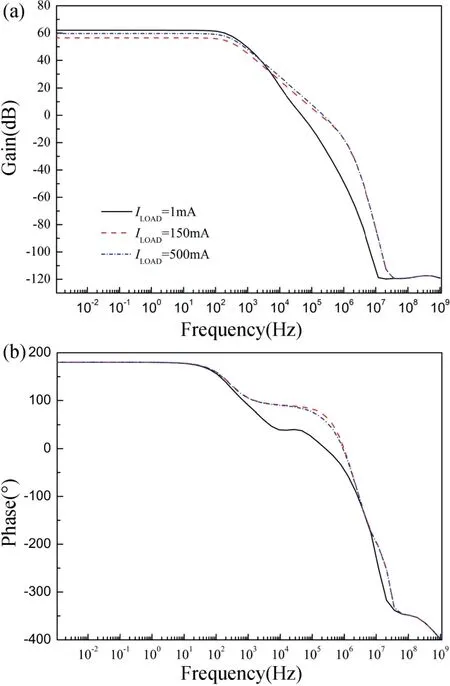

电源VIN电压为1.5 V,输出电压为1.2 V,LDO 分别在1,150 和500 mA 负载电流下的频率稳定性如图8 所示。仿真结果表明,重载下,环路中仅有一个极点,相位裕度约为83°,与理论分析一致。轻载下,通过负载跟踪补偿结构,稳定性得到改善,相位裕度为52°。负载电流在1~500 mA 范围内,相位裕度均能满足要求,电路稳定性较好。

图8 不同负载电流下的频率稳定性。(a)增益;(b)相位裕度Fig.8 Frequency stability under different load currents.(a) Gain;(b) Phase margin

LDO 在输出电压1.2 V,负载电流150 mA 时,不同工艺角下VIN和VBIAS的PSRR 曲线如图9 所示。可以看出VIN的PSRR 均为85 dB 左右,VBIAS的PSRR 均为90 dB 左右,LDO 具有较高的PSRR。

图9 不同工艺角下电路的PSRR。(a)VIN的PSRR;(b) VBIAS的PSRRFig.9 PSRR of the circuit under different process corners.(a)PSRR of VIN;(b) PSRR of VBIAS

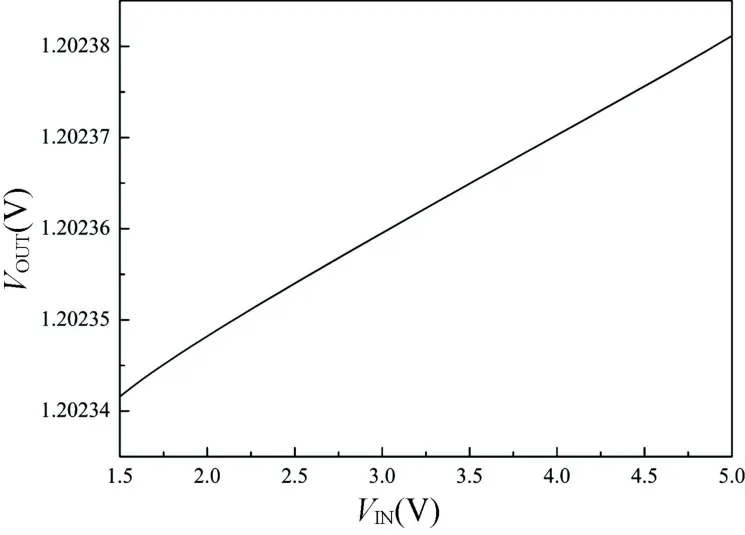

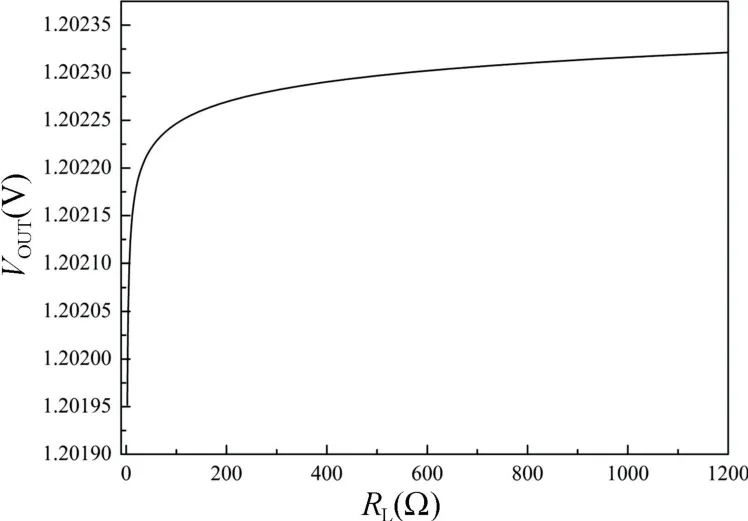

图10 和图11 分别为LDO 线性调整率和负载调整率的仿真,仿真结果表明:LDO 在1.2 V 输出电压下,线性调整率为0.01%/V,负载调整率为0.4 mV。

图10 线性调整率Fig.10 Line regulation

图11 负载调整率Fig.11 Load regulation

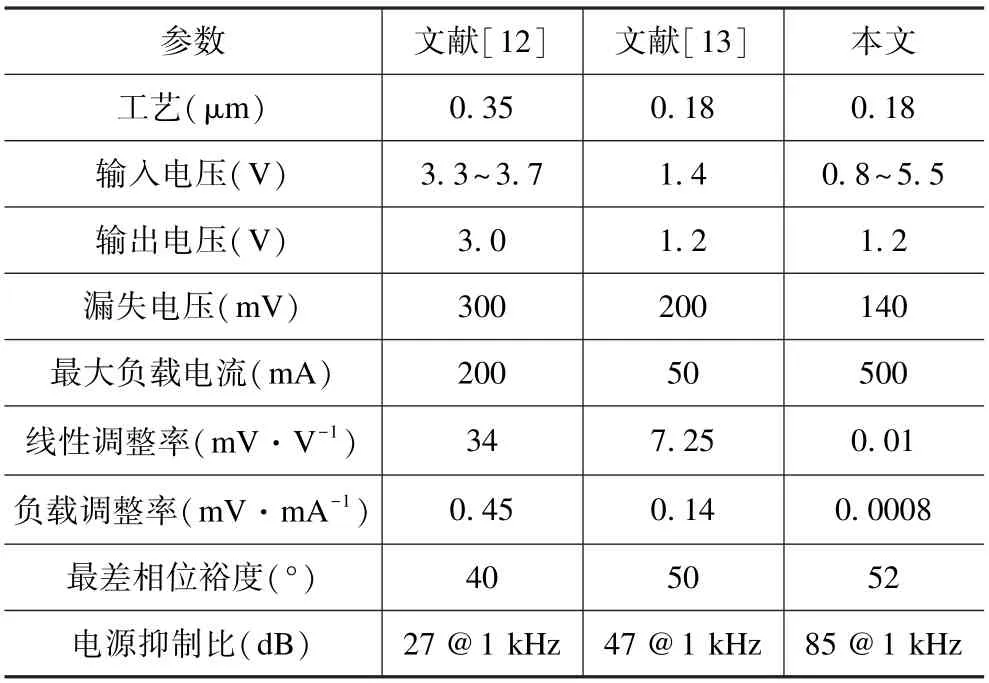

本文设计的LDO 与文献[12]和文献[13]仿真结果比较如表1 所示,在更大的负载驱动电流下,本设计具有更好的稳定性与PSRR。

表1 LDO 功能参数对比Tab.1 LDO functional parameter comparison

4 结论

本文中LDO 采用负载跟踪补偿技术实现了全负载范围内环路的稳定,保证1 kHz 时有较高的PSRR,输出电压稳定。文中详细介绍了LDO 环路补偿原理和电路结构的设计,基于0.18 μm CMOS 工艺完成了电路仿真以及版图的设计。电路最大负载电流可达500 mA,仿真结果表明,全负载范围内LDO 环路的相位裕度均大于52°,电路具有较小的负载调整率和线性调整率,满足便携式电子设备的电源需求。