数字CR-(RC)n滤波器的脉冲成形技术研究

杨小艳,洪旭,周建斌

(成都理工大学核技术与自动化工程学院,四川成都,610059)

0 前言

近几年,数字化谱仪的出现使得放射性测量变得更加准确和便捷。数字脉冲成形算法是数字化谱仪的关键。脉冲成形是指将探测器输出信号成形为特定的形状,以改变信号的信噪比、宽度、幅度等参数,进而改善测量系统的能量分辨率和计数率。梯形脉冲成形算法是常用的数字脉冲成形算法,它能够将指数衰减信号成形为等腰梯形[1]。在要求高能量分辨率测量时,可通过增加上升时间参数,提高信噪比;在高计数率测量环境时,可减小平顶宽度参数使成形脉冲变为三角形,以减小堆积。此外,探测器输出信号也被成形为高斯或类高斯波形,以提高探测器输出信号的信噪比[2]。周建斌等利用数值微分建立Sallen-Key电路的递推等式,并将其应用于核脉冲信号类高斯脉冲成形和谱线平滑中[3]。M.NaKhostin基于CR-(RC)n电路,采用z变换得到不同n值时CR-(RC)n电路的数字迭代算法[4]。本文采用数值微分的方式,分别建立CR电路、RC电路的数学模型,然后通过控制RC电路数学模型的迭代次数实现不同n值时的数字CR-(RC)n脉冲成形,得到类高斯波形。

1 CR-(CR)n数字实现

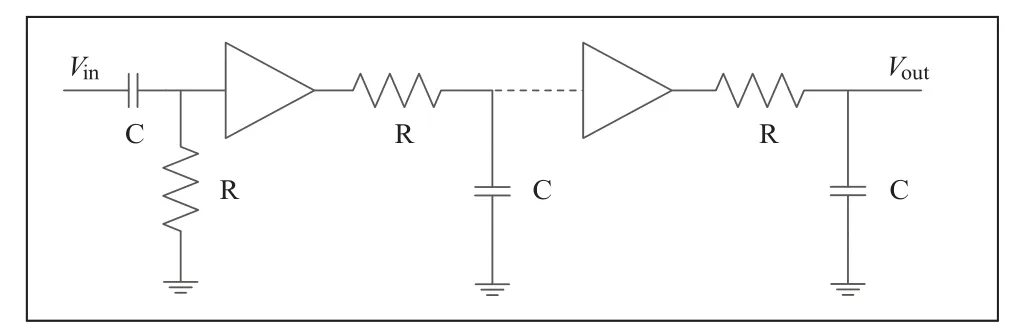

CR-(CR)n电路如图1所示。由图可以看出,它是由1级CR电路和n级的RC电路组成,n通常等于4,各级电路间用跟随器隔离。

图1 CR-(RC)n电路

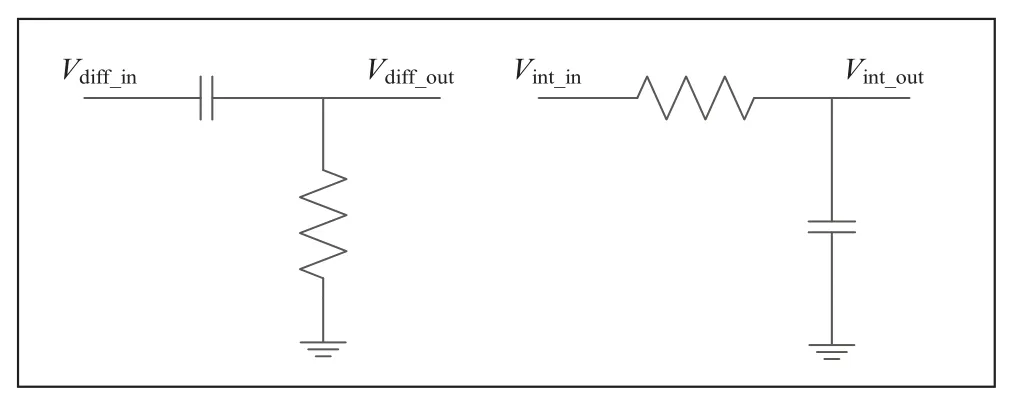

跟随器的特点是输入阻抗大,输出阻抗小,其输出信号近似等于输入信号。因此,可将CR-(CR)n电路拆分为CR成形网络和RC成形网络,如图2所示。探测器输出信号经过CR电路后,其输出接入RC电路,以此类推便可得到CR-(RC)n电路的输出。其中,当CR电路的成形时间常数τdiff与RC电路的成形时间常数τint相等时,即τdiff=τint=τ,CR-(CR)n电路输出脉冲波形近似为高斯波形,且该高斯脉冲的达峰时间为 nτ[5]。

图2 CR电路与RC电路

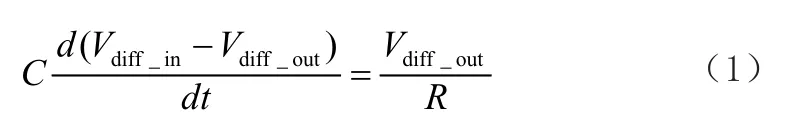

根据基尔霍夫电流定律,可以建立CR电路的电流等式,如式(1)所示

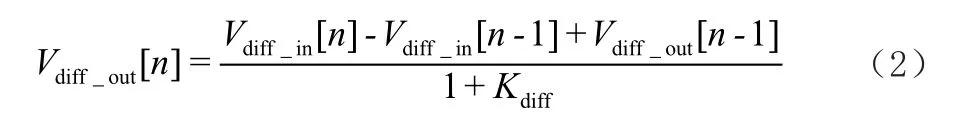

在式(1)中利用数值微分代替微分操作,即dVdiff_in=Vdiff_in[n]-Vdiff_in[n-1],dVdiff_out=Vdiff_out[n]-Vdiff_out[n-1],dt=ΔT。其中,ΔT为[n-1,n]间的时间间隔,在数字谱仪系统中表示ADC的采样时间间隔。则式(1)可写成式(2)。

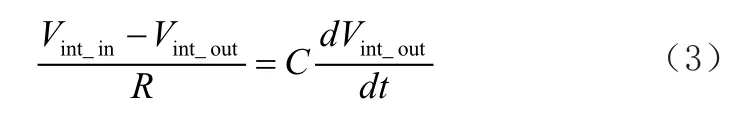

其中,Kdiff=ΔT/RC=ΔT/τ。式(2)即为CR电路的数学模型。同理,可建立RC电路的电流等式,即

整理得到RC电路的数学模型如式(4)所示。

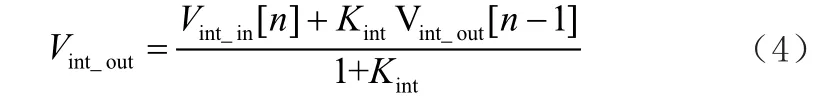

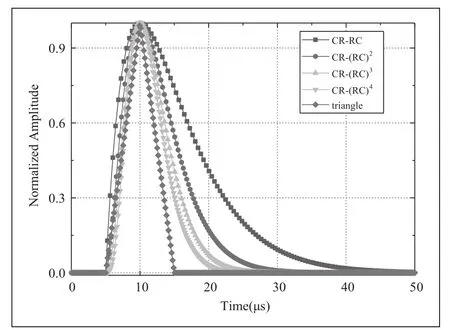

其中,Kint=RC/ΔT=τ/ΔT。利用式(2)和式(4)可对阶跃信号进行数字CR-(RC)n脉冲成形。不同n值的输出只需将上一级输出作为式(4)的输入即可。图3是不同n值时的CR-(RC)n脉冲成形结果,其中CR-(RC)n脉冲成形的达峰时间相同。由图3可以看出,随着n值增加,成形脉冲越趋近于高斯型,且n值越大,成形脉冲回到基线越快,脉冲宽度越小,但成形脉冲幅度衰减大。

图3 不同n值时的数字CR-(RC)n脉冲成形

2 仿真实验

噪声按产生的原理可以分为热噪声、散粒噪声和1/f噪声。热噪声也称作电压噪声或串行噪声(serial noise),它是由电阻或导体中载流子热运动引起的,与电阻或导体的温度有关;散粒噪声也称为电流噪声或并行噪声(parallel noise),它是由载流子的产生和消失的随机性引起的,与平均电流有关;1/f称为低频噪声,它普遍存在于电子管、双极性晶体管、场效应管等器件中,它主要与半导体器件材料的表面特性有关。

在核辐射测量系统中,探测器、前置放大器中均存在串行噪声、并行噪声。系统中的总噪声为串行噪声、并行噪声平方和的二次方根,串行噪声、并行噪声随测量系统中滤波成形电路的成形时间常数变化。因此,当滤波成形电路的成形时间常数使得系统中串行噪声、并行噪声相等时,系统总噪声最小,此时对应的成形时间常数称为噪声转角时间常数(noise corner time constant)。

2.1 能量分辨率

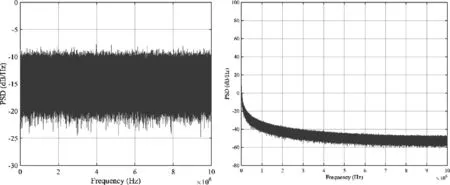

利用Matlab模拟串行噪声和并行噪声,然后分别叠加到阶跃信号上,产生带噪声的阶跃信号来研究CR-(RC)n脉冲成形对不同噪声的滤波性能。实验中,阶跃信号的上升时间为0,宽度为30μs,总计50000个脉冲信号;串行噪声通过Simulink工具中的Band-Limited White Noise模块产生;并行噪声由Band-Limited White Noise模块输出经过积分后产生。两种噪声的功率谱密度如图4所示。

图4 串行噪声、并行噪声功率谱密度

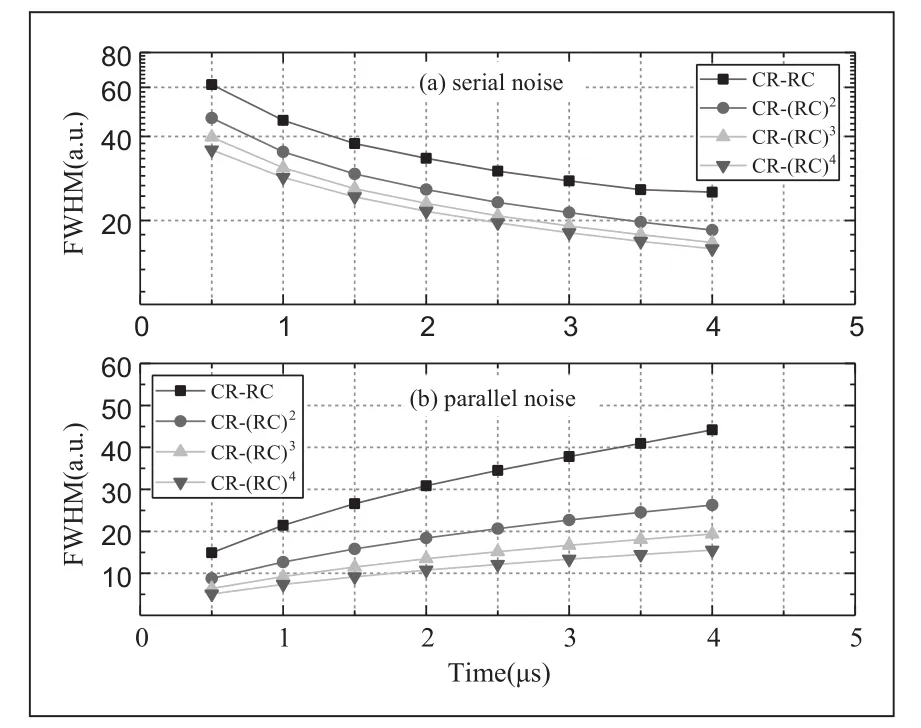

产生的带噪声阶跃信号先进行CR-(RC)n脉冲成形,然后将得到的类高斯脉冲做幅度甄别,生成幅度谱。生成的幅度谱利用高斯函数拟合,计算其半高宽FWHM。不同噪声下所得幅度谱的FWHM随达峰时间的变化结果如图5所示。由图5可以看出,串行噪声占主导时,所得幅度谱的FWHM随达峰时间增大而提高,CR-(RC)4脉冲成形滤波效果最佳;并行噪声占主导时,所得幅度谱的FWHM随达峰时间增大而损失,CR-(RC)4脉冲成形滤波效果最佳。

图5 不同噪声FWHM随达峰时间变化

当CR电路和RC电路的时间常数相等时,CR-(RC)n电路的传递函数可写成式(5),其中τ=RC。

输入信号为阶跃信号时,对应的拉普拉斯变换表达式如式(6)所示,其中阶跃信号的幅度为1。

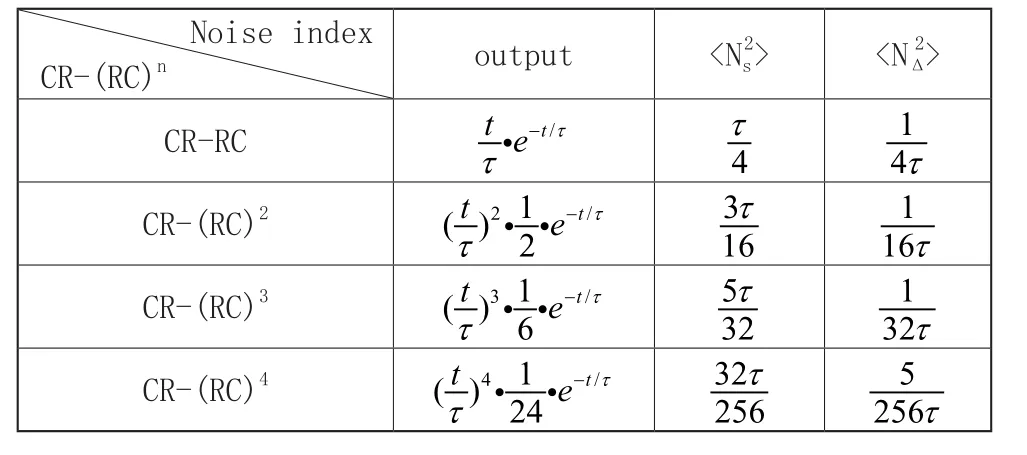

利用拉普拉斯逆变换可以得到CR-(RC)n电路输出信号的时域表达式,而不同n值对应的噪声指标

表1 不同n值滤波器对应输出及噪声指标

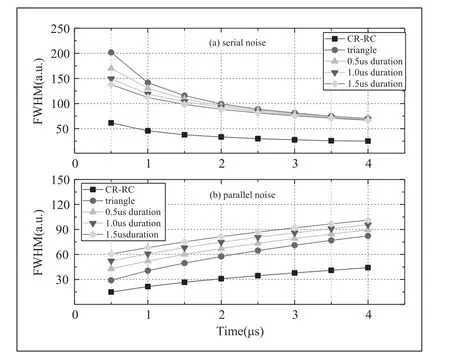

采用文献[1]中的阶跃信号梯形脉冲成形算法,对带噪声的阶跃信号先做梯形脉冲成形处理再进行幅度分析,并将得到的幅度谱的FWHM与CR-RC滤波器所得幅度谱的FWHM比较,结果如图6所示。由图6可以看出,相同达峰时间条件下,无论是串行噪声还是并行噪声,CR-RC脉冲成形较梯形脉冲成形具有更好的滤波能力;对于梯形脉冲成形,平顶宽度越大对串行噪声的抑制效果越好,三角滤波器对并行噪声的抑制效果最佳。

图6 CR-RC脉冲成形所得幅度谱与梯形脉冲成形所得幅度谱对比

2.2 计数率

由图3可以看出,相同达峰时间条件下,n=4时得到的成形脉冲宽度最小。将图3中信号做幅度归一化后与相同达峰时间的三角脉冲成形输出做对比,结果如图7所示。由图7可以看出,三角脉冲成形得到的输出较CR-(RC)n脉冲成形输出脉冲的宽度小。在高计数率测量条件下可以选用三角脉冲成形算法处理核脉冲信号。在保证能量分辨率的同时提高计数率可以采用CR-(RC)4脉冲成形。

图7 幅度归一化的CR-(RC)n脉冲成形与三角脉冲成形输出对比

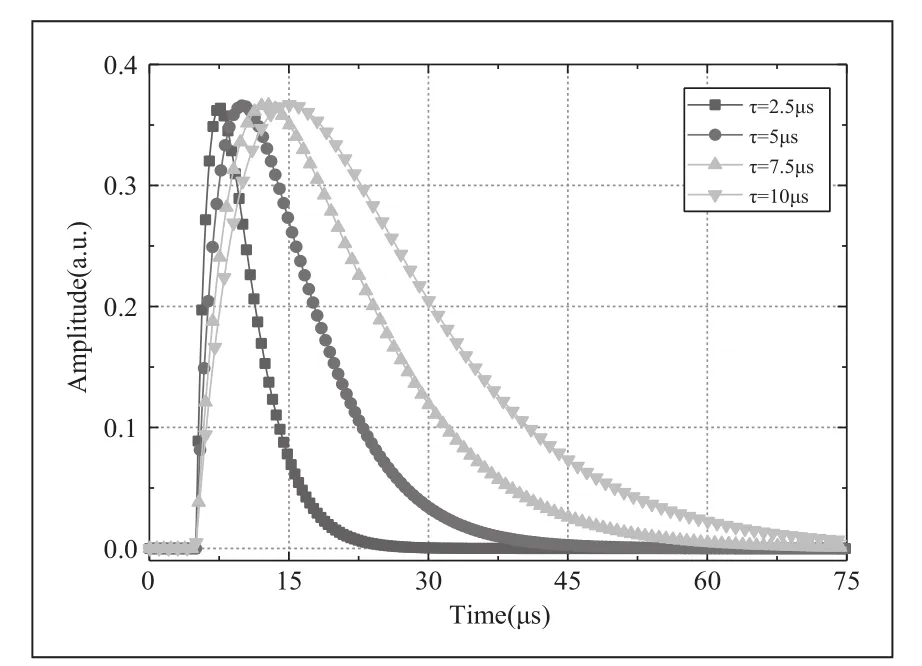

当n=1时,CR-(RC)n脉冲成形输出脉冲宽度最大,最容易产生堆积脉冲。不同达峰时间时,CR-RC脉冲成形对阶跃信号的输出脉冲如图8所示。由图8可以看出,随着达峰时间的增大,CR-RC输出脉冲宽度增大。对于相同宽度的输入信号,采用较长达峰时间的CR-RC脉冲成形更易产生堆积脉冲。

图8 不同形成时间常数的CR-RC脉冲成形输出

2.3 弹道亏损

由于电荷收集时间以及前置放大器中分布电容的影响,探测器输出信号通常存在一定的上升时间。探测器输出信号存在的上升时间会引起成形脉冲的幅度亏损,即弹道亏损。以梯形脉冲成形为例,当输入的信号存在上升沿时,成形脉冲幅度存在亏损,但可以通过增加梯形脉冲的平顶宽度减小由于输入信号上升时间引起的成形脉冲幅度亏损[1]。

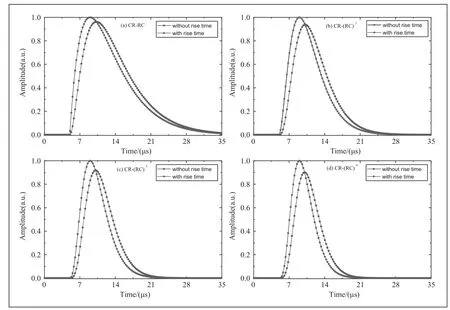

为研究CR-(RC)n滤波成形对输入信号上升时间的免疫能力,模拟带上升沿的阶跃信号,将得到的成形脉冲与无上升沿时得到的成形脉冲作对比。模拟的阶跃信号宽度为30μs,上升时间为1μs。达峰时间为5μs时,CR-(RC)n滤波输出如图9所示。

图9 CR-(RC)n弹道亏损

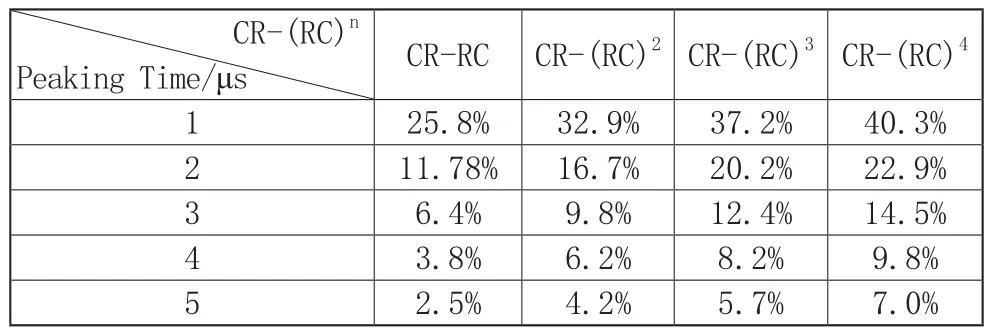

由图9可以看出,上升时间使CR-(RC)n滤波成形输出出现不同程度的幅度亏损。分别模拟达峰时间为1μs,2μs,3μs,4μs时CR-(RC)n滤波成形对阶跃信号、带上升沿阶跃信号的输出。以阶跃信号作为输入时通过CR-(RC)n滤波成形得到输出作为未发生幅度亏损的输出,计算上升沿引起的CR-(RC)n滤波成形输出的弹道亏损。计算结果如表2所示。由表2可以看出,相同达峰时间下,CR-RC滤波器输出信号弹道亏损最小;增加达峰时间可以减小CR-(RC)n滤波成形输出信号的弹道亏损。

表2 不同达峰时间CR-(RC)n滤波器输出弹道亏损

3 结论

根据前面的实验研究,可以得出如下结论:

(1)相同达峰时间,CR-(RC)4滤波成形对串行噪声、并行噪声滤波效果较CR-RC、CR-(RC)2、CR-(RC)3滤波成形好。

(2)相同达峰时间,CR-RC滤波成形对串行噪声、并行噪声较梯形滤波器好;串行噪声占主导时,增加梯形滤波器平顶宽度可提高信噪比,改善能量分辨率;并行噪声占主导时,减小梯形滤波器平顶宽度可提高信噪比,改善能量分辨率。

(3)CR-(RC)n滤波成形输出脉冲宽度随达峰时间的增加而增加;相同达峰时间,CR-(RC)4滤波成形输出脉冲宽度最小,可提高计数率。

(4)CR-RC滤波成形对上升时间的免疫能力最强,当输入信号存在上升时间时,弹道亏损造成的幅度损失最小;适当增加CR-RC滤波成形的达峰时间可以减小弹道亏损,但同时应该避免达峰时间增大造成脉冲堆积。