一种单传输零点LTCC高通滤波器的设计与制备

黄昆,钟茂锋,王霞辉,沓世我,李勃

(1.广东风华高新科技股份有限公司,广东肇庆,526020;2.新型电子元器件关键材料与工艺国家重点实验室,广东肇庆,526020;3.清华大学深圳国际研究生院材料研究院,广东深圳,518055;4. 肇庆学院,广东肇庆,526020)

0 引言

随着移动通信、航空航天等技术的发展,滤波器作为收发系统中的重要元件之一,向着小型化、高温度稳定性、高性能、高集成化的方向发展。LTCC技术使用低温共烧陶瓷材料,烧结温度接近900℃,可以使用低电阻率的银作为布线导体,降低器件在高频下的导体损耗,介质损耗相比传统的PCB材料低,可有效地降低器件的介质损耗,而且LTCC材料体系丰富多样,提供更大的设计空间。LTCC技术可实现在三维空间的布线,将电容、电感从传统的二维排布变成三维分布,极大地提高了集成密度,促进了器件小型化[1-2]。

戴永胜等通过一种新型的谐振单元设计的LTCC带通滤波器具有体积小、性能优异的特点[3]。王尔凡等通过在滤波器上表贴变容二极管设计了一种可调频的LTCC带通滤波器[4]。沓世我等通过电容耦合和电感耦合双耦合原理,设计并制备了一种中心频率为3.5 GHz的5G通信用LTCC带通滤波器[5]。滤波器的电路设计原理分为两大类:分布参数和集总参数,基于集总参数设计的滤波器更稳定和可控,当应用频率越来越高,元件之间的寄生参数带来的影响不容忽视[6],为了弥补寄生参数带来的不良影响和增强滤波器的性能,增加传输零点是一种常见设计方法[8],柴永强等利用谐振器交叉耦合增加传输零点[9],张博等通过混合电磁耦合引入传输零点[10]。

本文基于集中参数电路设计原理,以七阶的LC高通滤波电路为原型,为了在不增加元件的前提下提高滤波器在低频的抑制性能,利用电感耦合作用在串联支路增加并联谐振,从而引入传输零点。利用现有的工艺条件制备出一种具有单传输零点的LTCC高通滤波器。

1 LTCC高通滤波器的原理与设计

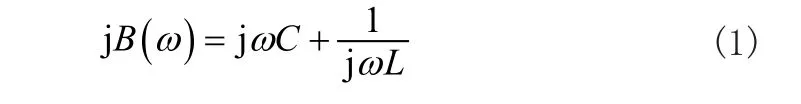

1.1 电路原理

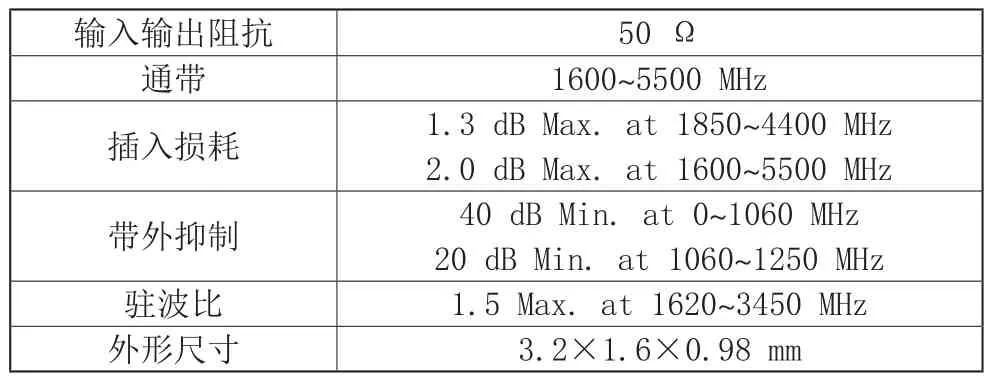

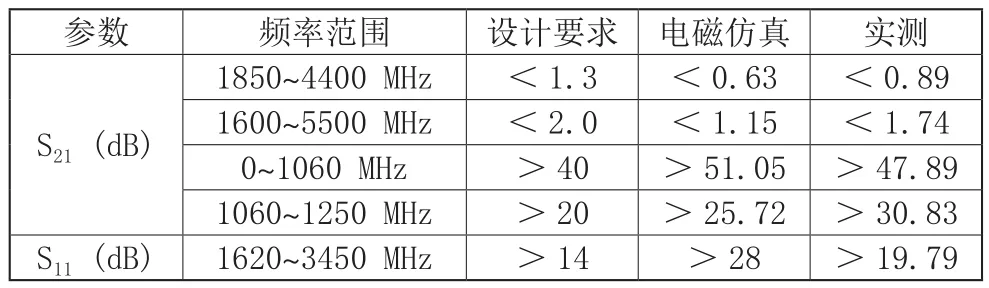

高通滤波器的设计指标如表1所示,这是一款通带为1600~5500MHz的高通滤波器,该滤波器在低频段对滤波性能有特别要求,在0~1060MHz频段内抑制强度要大于40dB。本文的高通滤波器基于集总参数LC电路设计,为了实现高带外抑制、低带内插损,选用七阶的高通滤波器作为设计原型[11]。

表1 高通滤波器的设计指标

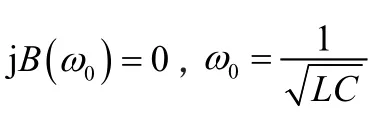

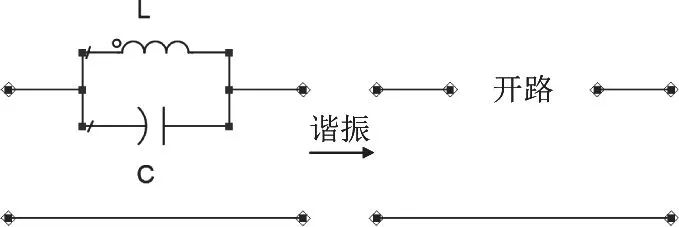

图1 串联支路的并联谐振

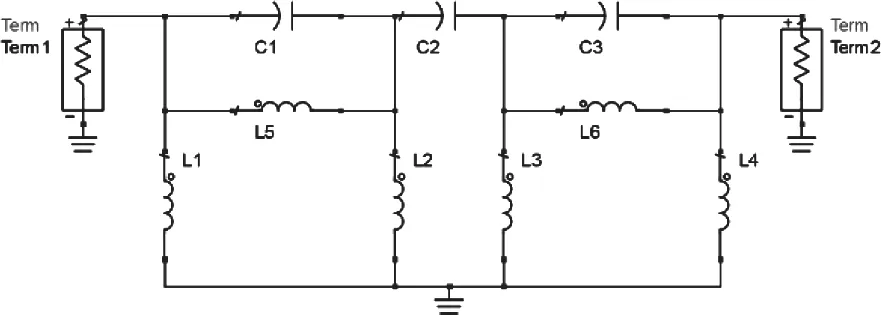

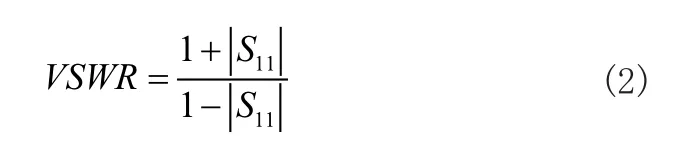

电路原理图如图2所示,C1与L5、C3与L6形成传输零点,经过ADS调谐优化,元件的具体数值为:C1=C3=2.61pF,C2=1.23pF,L1=L4=11.56nH,L2=L3=3.33nH,L5=L6=8.80nH。电路仿真结果如图3所示,低频段的带外抑制完全满足40 dB的要求,带内回波损耗在20dB以上,满足带内驻波比小于1.5的要求。电压驻波比(VSWR)与回波损耗(S11)的转换关系如公式(2)所示,带内驻波比小于1.5对应带内回波损耗大于14dB。传输零点出现在1GHz附近,可以有效地增强高通滤波器在此邻近频段的抑制能力。

图2 高通滤波器的电路原理图

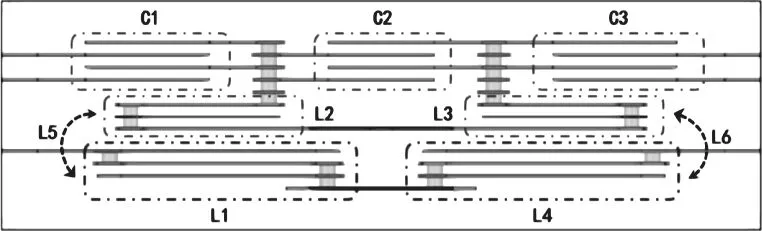

图3 高通滤波器的三维结构图

1.2 结构设计与电磁仿真

图2所示的电路原理图只是实物滤波器简化后的理论等效电路,在滤波器的实际结构中,电容和电感分布在器件里的三维空间,元件相互间将会产生寄生效应,这些寄生参数不可忽略,同时也无法完全消除这种寄生效应,利用这些寄生效应,替代电路原理图中的部分元件,既可以节省设计空间,又可以增强器件的性能。为了提高元件的Q值和自谐振频率,使用叠层电容和叠层螺旋电感来实现电路原理图的电容和电感,特别地,L5、L6分别通过L1和L2、L3和L4之间的耦合电感来实现,从而节省空间,并且L5与C1,L6与C3在串联支路形成并联谐振电路,引入传输零点。

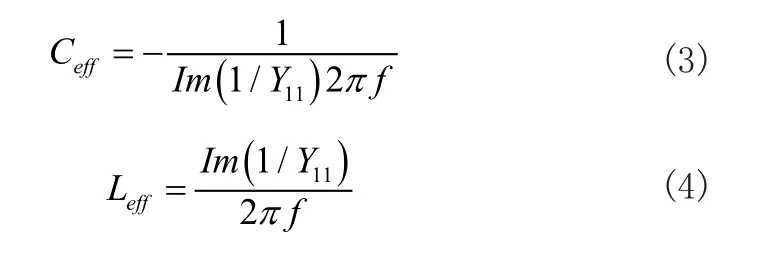

为了实现特定的元件,从理论等效电路转化为三维结构,可以对单一元件进行仿真,借助电容和电感参数提取公式(3)、(4),得到元件三维结构的基本信息。如叠层电容占用的面积、堆叠的层数,叠层螺旋电感占用的面积、堆叠的层数、走线的宽度等[12]。经过初步仿真,C1和C3由四层叠层电容提供;C2由占用面积较小的四层叠层电容提供;L1和L4由三层螺旋电感提供,L1和L2由相对较小的三层螺旋电感提供。初步仿真得到的结构尺寸大小不是最终器件上的结构尺寸,还需要将各个元件组合成一个完成的器件进行仿真。

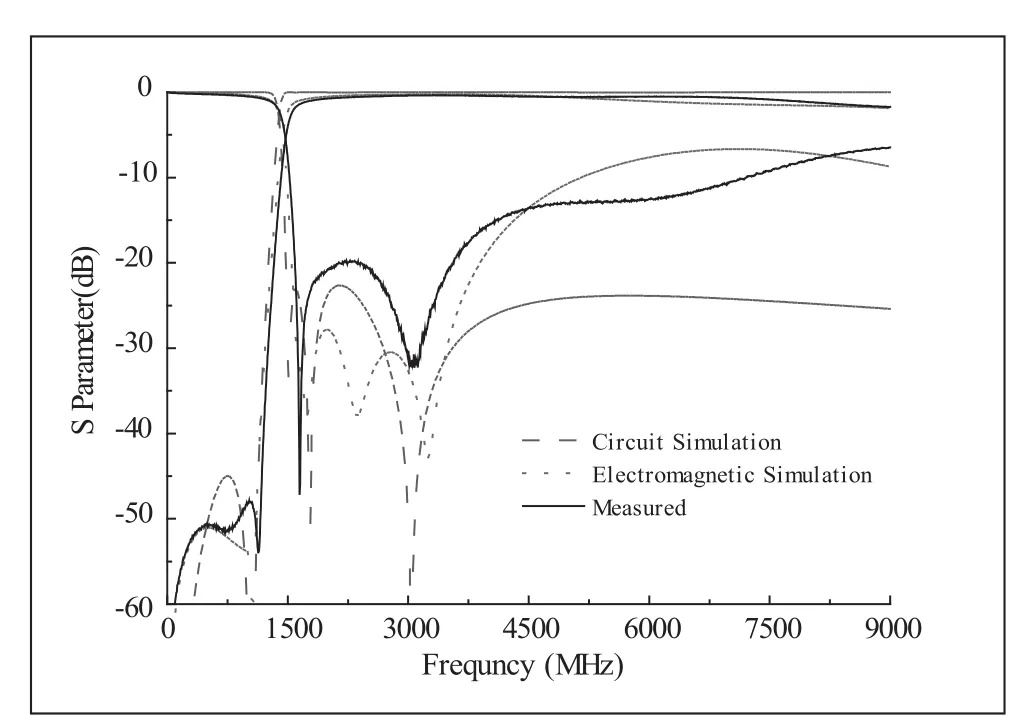

因为元件互连、元件与元件之间存在寄生参数,这些寄生参数对器件影响不可忽视。所以,在初步完成高通滤波器的三维结构建模后,还需要对器件的三维结构进行参数优化,才能实现器件的设计指标。为了使仿真结果和实测结果尽可能一致,在仿真过程中是带实际测试板仿真的,测试板上的输入输出端微带传输线的特征阻抗必须设计成50Ω,以便与测试使用的50Ω同轴线相匹配。仿真使用相对介电常数为5.5、损耗角正切值为0.004的陶瓷作为介质层,本文设计的高通滤波器的三维结构如图3所示,C1、C2、C3分布在最上方,L2和L3分布在中间,L1和L4分布在最下方,器件的两端为输入、输出端口,腰部有2个接地端,尺寸大小为3.2×1.6×0.92 mm,最终的电磁仿真结果如图4所示虚线部分,图中包含高通滤波器的插入损耗(S21)和回波损耗(S11)曲线。

图4 仿真结果与测试数据

2 高通滤波器的实现和测试分析

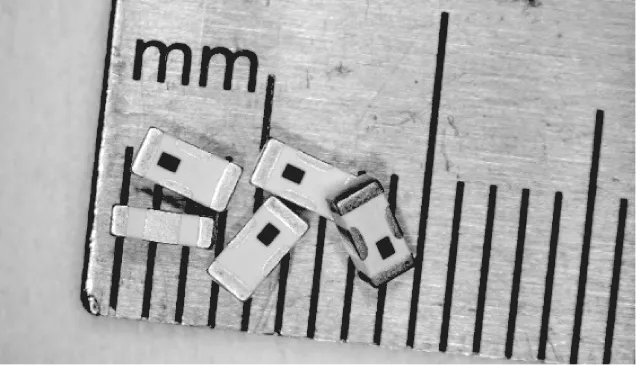

基于LTCC工艺,使用相对介电常数为5.5的瓷粉配料,配料过程需要向瓷粉加入分散剂、粘结剂等,在尼龙罐中混合、研磨1天,得到分散均匀的流延浆料,通过流延工艺得到厚度为57um的生瓷片。机械打孔机按照打孔图纸将产品内部的连通孔打在生瓷片上,通孔直径为100um;然后用丝网通过印刷工艺将产品的每一层图案印刷在生瓷片上,经过叠层、温水等静压(层压)、切割工序得到生坯产品,生坯经过排胶、烧结成型,通过封端烧端的方式将内电极引出到外电极端口,最后经过沉积、电性能测试得到最后的成品,LTCC高通滤波器的实物如图5所示。

图5 高通滤波器产品实物图

使用矢量网络分析仪Agilent N5222A对制备的滤波器进行测试,得到的实测数据如图4实线所示,实测结果与仿真结果有一定差异,但总体都满足设计指标。表2对比了实测数据与电磁仿真数据的差异,这里取数据的绝对值来对比损耗大小。实测带内插入损耗比仿真数据大,差别主要来源于截止频率的偏移以及测试条件带来的损耗,包括测试板、SMA接头、同轴线带来的损耗;另外,实际的内电极银的导体损耗和LTCC材料的介质损耗比仿真数值要大一点,也会导致实测插入损耗比仿真数值偏大。0~1060MHz的带外抑制性能,仿真与实测基本一致;1060~1250MHz的带外抑制性能,实测效果比仿真更好,这与前面提到的截止频率偏移有关,由图4可以看出,实测的截止频率相比仿真稍微往右偏移,这使得实际滤波器在低频段某些范围内的抑制变强了,但是带内插损也相应地增大了。实测的通带内回波损耗与仿真的曲线相差比较大,虽然两者都满足设计要求,但是实测的回波损耗比仿真的小,主要原因是实物与电磁仿真在通带内的谐振点的位置有偏差,谐振点的位置取决于电容和电感,由图4的回波损耗曲线可以看出,电磁仿真的通带内第二个谐振点被设计在2000 MHz附近,目的是实现1620~3450MHz 频段内具有较高的回波损耗,由表2可知在此频段内的回波损耗是大于28 dB的。实测通带内的第二个谐振点与第三个谐振点基本重合了,看起来只有第三个谐振点存在,这与实际制备过程中的误差有关,例如叠层偏差造成电容值减小、电感走线变宽等,导致谐振点往高频方向偏移。此外,实际器件的介质层厚度与设计值的偏差会对器件的性能产生整体范围的影响。

表2 电磁仿真与实测数据对比

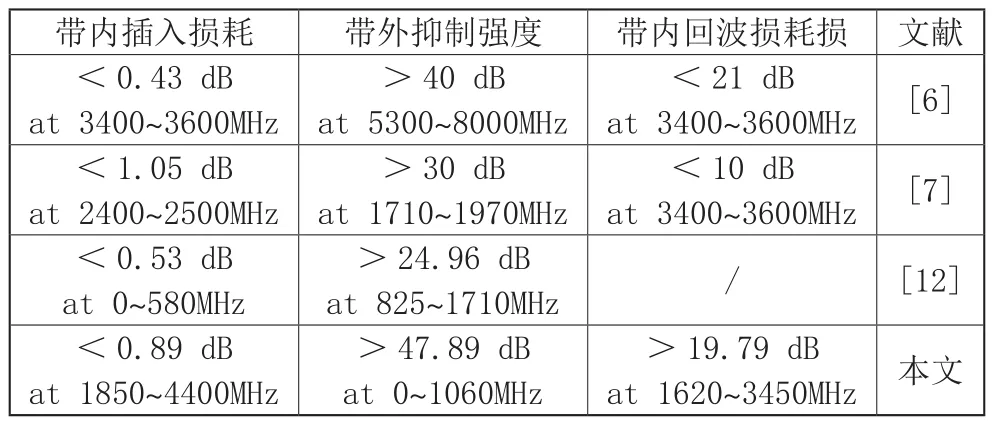

从图4的实测结果与仿真结果可知,实物很好地与设计贴合,仿真与实测性能都能满足设计指标。本文设计的高通滤波器,实测通带1850~4400MHz内的插入损耗只有不到0.89dB,带外0~1060Mhz抑制强度高于47.89dB,带内回波损耗大于19.79dB,即带内驻波比小于1.25。如表3所示,与其他滤波器性能相比,本文设计的LTCC高通滤波器具有带外抑制强度高,带内回波损耗大,带内插入损耗比较好的特点。

表3 滤波器性能对比

3 结论

本文基于LTCC技术设计和制备的高通滤波器,在3D空间中对元件进行巧妙布局,其新颖结构利用元件之间的耦合作用,在不增加器件尺寸的前提下引入传输零点,实现了优异的滤波性能,产品实测性能与仿真数据基本吻合,均满足设计要求,目前这款高通滤波器已形成商业化生产。随着电子系统朝着高度集成化、小型化、高性能、高可靠性的方向发展,LTCC射频器件可进一步发挥它的独特优势和作用。