T/R组件收发转换时间的测试方法

■ 章露/江苏金陵机械制造总厂

0 引言

T/R组件的构成随雷达系统对性能的要求有所不同,具体电路的实现也有很大的差异,从目前T/R组件的技术特点来看,T/R组件大体分为模拟式和数字式两类。模拟式T/R组件的输入、输出皆为射频信号,一般有三种基本结构,即收发分离结构、共用移相器结构和Common Leg结 构;数 字 式T/R组件直接通过数字频率合成(DDS)来控制组件的频率、幅度以及相位等参数,但DDS输出频率不是很高,通常需采用变频技术来达到T/R组件所需的工作频率。现阶段模拟式T/R组件的技术已经十分成熟,本文主要介绍收发分离结构的T/R组件收发转换时间测试的具体方法。

1 收发分离结构T/R组件

收发分离结构的T/R组件主要指有单独的发射通道和单独的接收通道的T/R组件,两者相互独立且具有较高的通道间隔离度。这种结构T/R组件的特点是线性度较好,通常应用于对系统隔离性能要求较高的场合。由于发射、接收采用各自的通道,每个通道都需要配置移相器和衰减器,应用的单元电路较多,电路结构也较为复杂。

T/R组件一般的主要性能指标包括工作频率、发射输出功率、占空比、接收支路增益、接收支路噪声系数、移相精度、衰减精度、输入输出驻波以及收发转换时间等。其中,收发转换时间是一个相对比较重要的性能指标,是指T/R组件在工作期间,从发射关闭状态切换到接收打开状态以及从接收关闭状态切换到发射打开状态需要耗费的时间。在高重复频率的工作方式下的T/R组件,精确测量其收发转换时间是非常重要的。

2 测试

2.1 芯片介绍

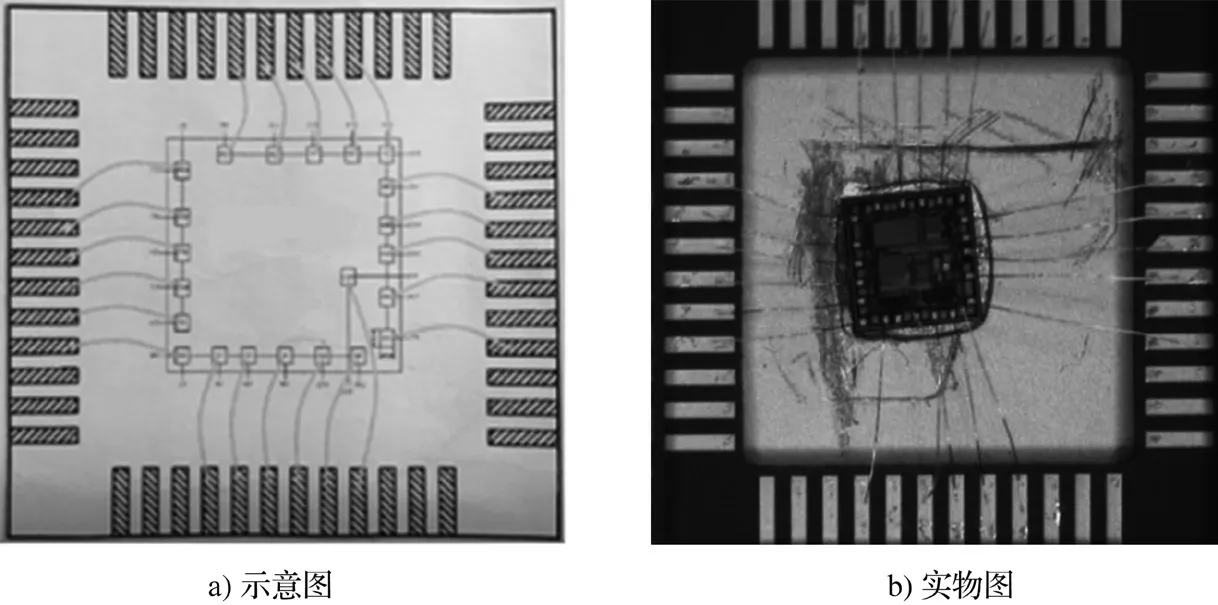

某型延时电路芯片采用CMOS工艺,内置基准延时电路,可将COMS/TTL输入脉冲信号延时并扩展占空比,输出高精确时隙的脉冲信号,其结构示意如图1所示。

图1 延时电路芯片结构示意图

2.2 工作原理

将T/R组件发射关闭至接收打开时间记为t1,接收关闭至发射打开时间记为t2,延时电路芯片引脚CON1、CON2、CON3、CON4为预留控制端,用于有限调整延时量,通过金丝键合接地实现调整。由于4个控制端有16种组合,反复键合易损伤焊盘,因此通过制作延时电路芯片单片测试系统寻找合适的组合,使t1、t2符合指标要求。

延时电路芯片上电后,在信号输入 端IN、RS1、RS2、TS1、TS2输 入COMS/TTL脉冲信号。通过测试R1、R2、T1、T2信号输出端来确定延时量。在T/R组件中,IN信号输入端由TP脉冲电平控制,RS1、RS2、TS1、TS2信号输入端由某型波束控制专用电路产生的接收控制字(STDR1、STDR2)和发射控制字(STDT1、STDT2)控制。接收控制字和发射控制字的加载由TR脉冲电平控制,且接收控制字与TR信号同向,发射控制字与TR信号反向。T/R组件收发控制时序如图2所示。TP信号上升沿超前TR信号上升沿,TP信号下降沿滞后TR信号下降沿。

图2 T/R组件收发时序控制示意图

经上述分析可得,通过脉冲信号发生器模拟TP、TR脉冲信号,提供延时芯片信号输入端IN、RS1、RS2、TS1、TS2所需信号,由R1、R2、T1、T2得到的延时信号即为T/R组件发射关闭至接收打开时间t1、接收关闭至发射打开时间t2的测试值。

2.3 测试过程

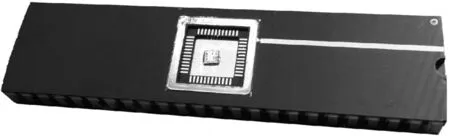

1)延时电路芯片单片测试系统

有封装的芯片(如DIP封装),可以直接采用钩针在芯片管脚处进行芯片的供电及电信号的测量。而在高密度封装的T/R组件中,由于延时电路芯片为裸芯片,为了方便测试,通过金丝键合(见图3)与KD-80177-E管壳相连,形成延时电路芯片单片测试系统,完成键合后对键合点和管壳引脚进行测试,避免引线键合出现遗漏,如图4所示。

图3 延时电路芯片金丝键合图

图4 延时电路芯片单片测试系统

2)测试方法

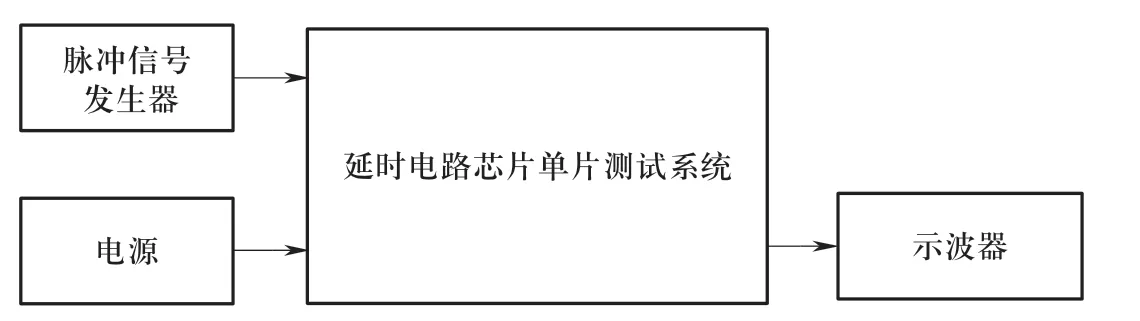

延时电路芯片单片测试系统测试方法如图5所示,由电源提供延时电路芯片工作电压,将延时电路芯片信号输入端IN、RS1、RS2、TS1、TS2用电缆连接至脉冲信号发生器,作为脉冲信号输入;R1、R2、T1、T2信号输出端连接至示波器。

图5 延时电路芯片单片测试原理图

脉冲信号发生器OUT1、OUT2、分别提供延时芯片IN、RS1、TS1脉冲信号发生器通道1和通道2频率、占空比和延时,用于模拟TP信号上升沿超前T/R信号上升沿时间,使用示波器测量R1、T1信号。

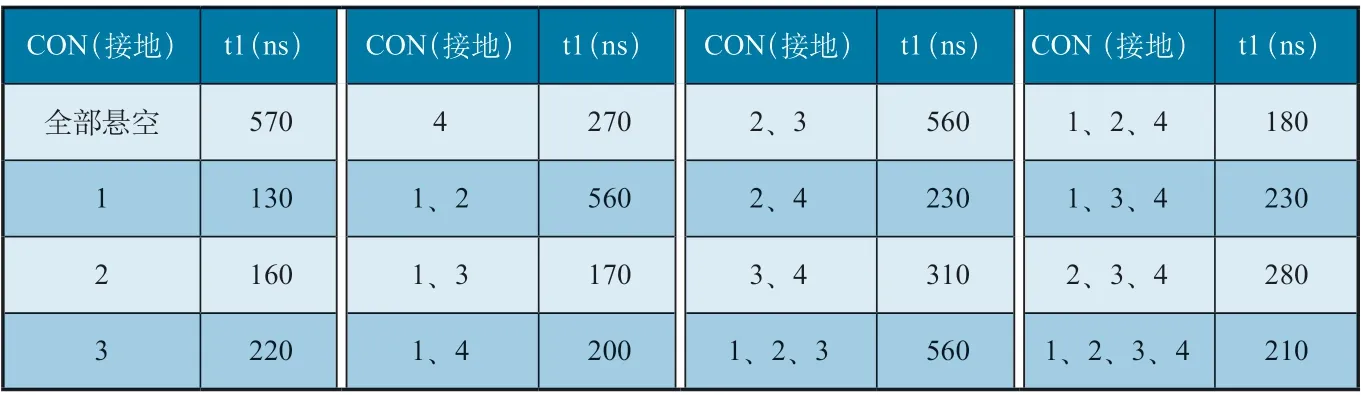

延时电路芯片引脚CON1、CON2、CON3、CON4在片内已悬空作上拉,通过接地实现调整,4个CON端有16种组合,对每种组合分别进行测试,发射关闭至接收打开时间t1的测试结果如表1所示。

表1 16种组合测试结果

根据表1中的测试结果,选择发射关闭至接收打开时间较短即CON1接地。当前状态下对t2进行测试,延时电路芯片测试结果如图6所示。

图6 延时电路芯片测试结果

3 总结

本文以典型的延时电路芯片为例,介绍了在收发分离结构的T/R组件中收发转换时间的测试方法,在裸芯片难以测试的情况下搭建单片测试系统,从而降低了测试难度,同时也可保证测试的准确性,可为T/R组件的设计和修理提供指导。