基于FPGA和ARM的音圈电机式振镜驱动器设计

梁宇飞,石上瑶,张 栋,武 涛

(中北大学 机械工程学院,太原 030051)

0 引 言

音圈电机式振镜具有高频响、高加速、快响应等优势,相较于扫描电机式振镜可以提供更高的速度及响应[1-3],因此,音圈电机式振镜在驱动控制方面具有更高的要求。

传统的音圈电机大部分采用数字控制方法,其缺点是无法直接实现音圈电机的高精度要求,要达到高精度要求,需配备对应精度的ADC模块及数字处理器等。模拟控制信号优势体现在信号的高精度及无限分辨率,对于要高精度控制的音圈电机拥有较大的优势,并且实际使用时音圈电机所需电流较小,音圈电机式振镜采用模拟电路在保持不失真条件下,可以满足高精度及高速控制。

现在工业用音圈电机驱动控制器大都采用单一处理器,再配合外围相关电路以达到驱动目的。这种驱动方法存在诸多不足。单一使用DSP定点型处理器作为处理核心,无法保证复杂算法保持高速高精度,而且DSP外设模块的固定化,无法满足设计的灵活性;单一使用FPGA作为处理核心,虽然拥有并行计算及灵活性的优点,但无法完成浮点运算[4]。近几年FPGA快速发展,将其与ARM芯片结合,可以更好地利用FPGA高速并行运算的特点,ARM芯片拥有的优良兼容性既提供更好的可行性,也弥补了FPGA无法完成浮点运算的缺点。但是现有的结合方式未充分发挥FPGA的并行计算等优势,只是一些单纯的时序处理,其性能没有得到充分的发挥。

本文提出一种基于ARM和FPGA的异构处理器驱动控制方法,并设计软硬件,以实现对音圈电机式振镜的驱动控制。再依照ARM和FPGA的各自功能特点进行功能划分和软件设计[5]。

1 驱动器硬件结构及功能划分

1.1 硬件结构

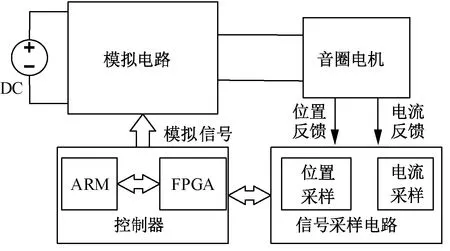

驱动控制器采用基于ARM和FPGA的结构,搭配上位机和外围电路完成音圈电机式振镜的驱动控制。驱动器硬件结构如图1所示。其中ARM使用基于Cortex-M7内核的STM32H750芯片;FPGA使用Altera公司的10 M02SCU169芯片。ARM通过SPI通讯协议传输电压信号到DAC芯片;音圈电机动子实时位置使用光栅尺传感器采集并计算得到;电路电流由STM32内部传感器采集并计算得到。

图1 系统硬件设计

1.2 功能划分

ARM属于可编程软件,拥有通用性、灵活性等特点。FPGA是硬件可编程类型,拥有高速并行计算能力,但在一些复杂运算的场合中会占用大量的逻辑单元,不适合高速且复杂的场合。综合上述ARM和FPGA优缺点后,依照实际需求情况进行功能分配,其中ARM主要负责系统初始化、信号采样、模拟信号输出、闭环控制算法等功能,FPGA主要负责激光打标图象点数据集处理、上位机通讯功能、与ARM之间数据交换等功能。驱动控制器中各部分功能划分如图2所示。

图2 控制器功能划分

2 FPGA功能设计

2.1 上位机通讯模块设计

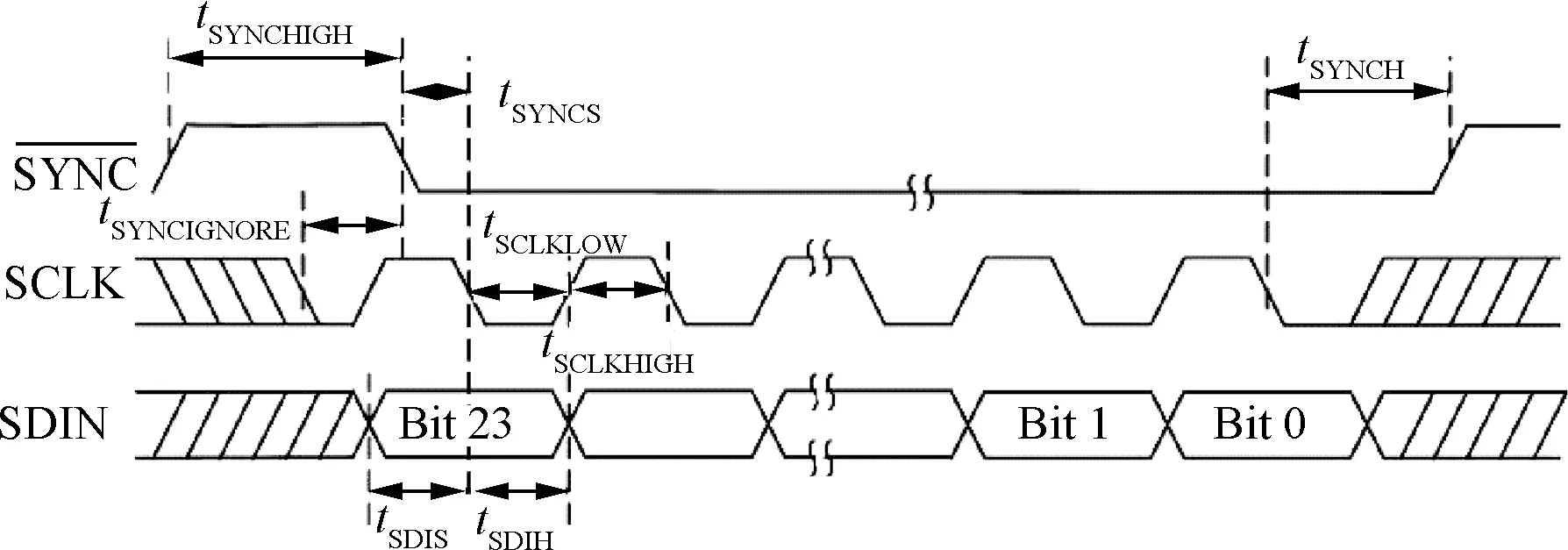

振镜控制器与上位机通讯普遍采用XY2-100协议。此协议由时钟信号、同步信号、X/Y坐标数据四路差分信号组成。XY2-100协议时序图如图3所示。

图3 XY2-100 协议时序图

数据通道共有20位数据位,其中第1~3位数据位为控制头,在上升沿发送;第4~19位数据位为振镜数据,在上升沿发送;第20位数据位为奇偶校验位,在下降沿发送完毕[6]。

2.2 驱动器通信模块

ARM和FPGA之间协同处理必须保持高速通信。它们的通信主要包括异步串行接口方式、DMA方式、总线方式和将FPGA作为存储设备4种[6]。选用将FPGA作为存储器的方式可以在简化结构的同时保持高速通讯,ARM通过FMC接口访问SDRAM存储的信息,可以保持超高的读写速度,继而满足驱动控制所需的高速数据交换。ARM和FPGA通信原理图如图4所示。其中D0~D15是双向数据总线,A0~A23是地址总线,SDCLK是SDRAM的时钟线,SDNWE是写入使能,SDCKE是存储区域时钟使能,SDNE是存储区域芯片使能,NBL是写访问的输出字节屏蔽。

图4 ARM和FPGA通信原理图

2.3 数据点集处理模块

振镜工作时,高密集数据传输引起上位机发送速率和振镜速率不匹配而在某点停留时间过长,可导致激光烧蚀,但若数据点过少也会导致精度降低、质量下降[7]。使用FPGA对上位机下发图象进行数据点提取操作,将原始数据点集经过稀疏化、曲线点集分段、最小二乘法非均匀有理B样条曲线(以下简称NURBS)拟合数据处理,转换成由少量直线和曲线构成的实体,这样可以避免因为数据点密集或稀疏而出现问题。

NURBS曲线由控制点、权重、节点矢量和阶数组成,数学定义如下:

(1)

其中Ni,k(u)满足De-Boor递推关系式:

式中:fi为控制点;ωi为权因子;u为节点矢量[8]。

在FPGA中对上位机下发数据点集进行再处理。对于包含节点矢量和数据坐标的值,使用最小二乘法拟合NURBS曲线,最终可以得到通过最小二乘法全局逼近的NURBS表达式。

3 ARM功能设计

3.1 ARM主程序

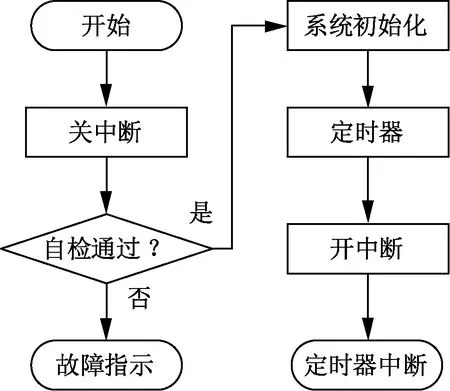

ARM主程序主要用于全局阶段性控制,把握每一个阶段,例如开关中断、系统初始化以及系统定时器的驶入驶出等过程。其主程序流程图如图5所示。

图5 ARM主程序流程图

3.2 信号输出模块

驱动器采用模拟电路控制,通过STM32生成连续模拟信号,16位DAC80501使用SPI接口以DMA方式发送到驱动电路中。STM32H750使用SPI协议以DMA方式驱动DAC外设能够得到比肩FPGA的速度。DAC的SPI接口通信协议如图6所示。

图6 DAC的SPI接口通信协议

3.3 信号采样模块

信号采样包括电流采样和位置采样两部分。电流采样使用STM32H750内部的16位ADC1采样,并且内部ADC采样需在STM32上外接3.3 V的基准电压。位置采样使用1 μm增量式光栅尺,通过高速差分线路接收器将采集的A-,A+,B-,B+,Z-,Z+转化为A,B,Z三相信号。其中A、B表示光栅尺的位置信号,Z表示光栅尺的原点信号。

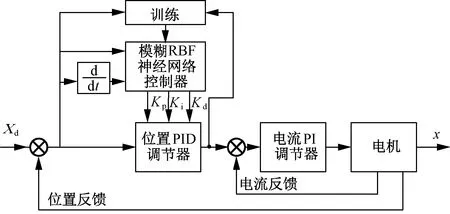

3.4 闭环控制算法模块

电机控制算法采用模糊RBF神经网络的位置控制和PI电流控制。位置环由模糊RBF神经网络控制器实现PID参数的实时控制,根据位置输出误差及误差率作为控制器的输入,通过模糊RBF神经网络控制器的模糊化及模糊推理,并且进行不间断训练,最终可动态修正PID控制参数Kp,Ki,Kd,使系统拥有更好的抗干扰能力和动态响应[9-13]。电流环采用传统的PI控制即可达到目标稳定效果。

闭环控制算法示意图如图7所示。

图7 闭环控制算法示意图

4 模拟电路设计仿真及实验

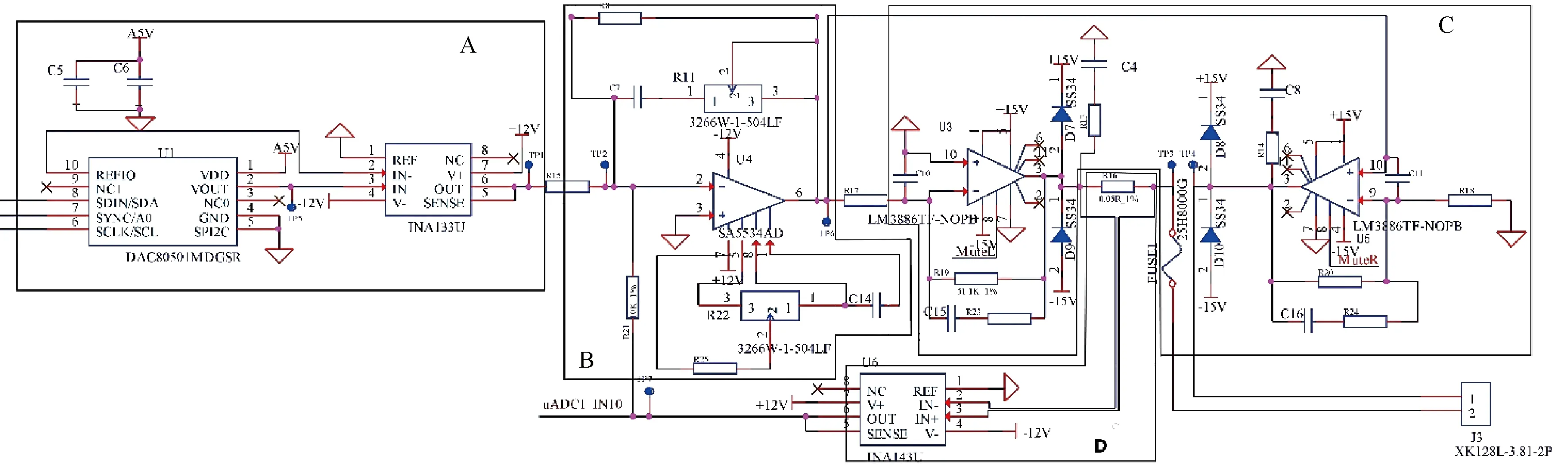

根据需求设计的全模拟驱动电路,如图8、图9所示。再使用NI multisim进行电路仿真,探究是否符合设计要求[14]。

图8 驱动电路图

图9 位置采样信号电路图

4.1 驱动电路设计

4.1.1 差分转单端电路

DA信号的输出需要转化为单端信号进行后续的计算,本电路差分转单端芯片选用TI公司的INA133U,可以实现准确的增益和高共模抑制。电路如图8中A所示。

4.1.2 运算放大电路

运算放大器采用TI公司的SA5534AD,具备高输出驱动能力等特点。通过在COMP和COMP/BAL上连接外部补偿电容器来优化各种应用的频率响应。电路如图8中B所示。

4.1.3 功率驱动电路

功率驱动芯片采用TI公司的LM3886TF,可以利用自身自峰值瞬时温度保护电路,提供动态受保护的安全工作区,使输出端得到完全的保护,防止欠压、过压等。电路如图8中C所示。

4.1.4 电流采样电路

电流采样采用精密采样电阻采样,方便接入模拟电路,且不会影响电路输出终值。使用INA143U处理采样电阻两端信号,输出单端信号计算得到实时电流值。电路如图8中D所示。

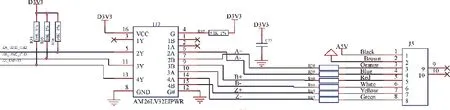

4.1.5 位置采样电路

位置采样电路将光栅尺传感器输出的差分信号输入到AM26LV32ETPWR中转化为单端信号。位置采样电路如图9所示。

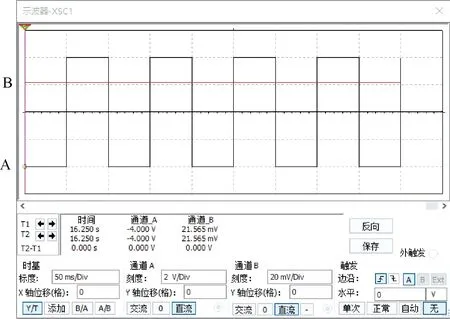

4.2 驱动电路仿真测试

根据图8电路在NI multisim中进行电路绘制并仿真测试,NI multisim中绘制的仿真电路图如图10所示。

图10 NImultisim软件仿真电路图

使用软件自带的信号发生器在电路输出端输入30 Hz方波信号,测试得到电路最终的稳定输出信号。仿真结果如图11所示,通道A表示输入方波信号,通道B表示稳定情况下精密采样电阻实测电压值,满足设计要求[15]。

图11 仿真结果图

4.3 实验测试

本文设计的驱动器开发板如图12所示。

图12 硬件驱动板实物图

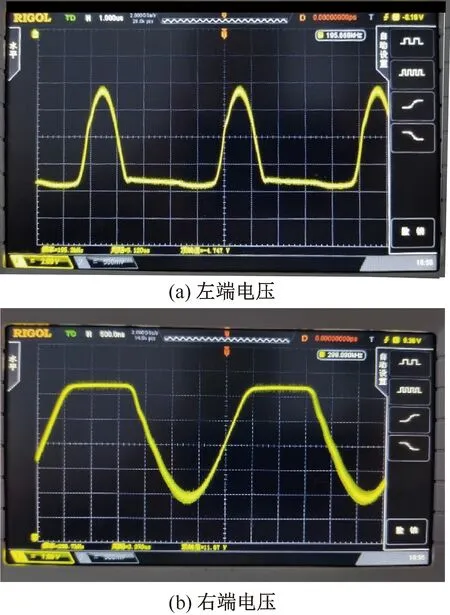

本文基于FPGA和ARM设计的驱动器开发板,输出驱动电机两端电压信号,如图13所示。所测两端电压信号可以满足设计音圈电机的驱动控制,说明本文设计的驱动器有效。

图13 电机两端电压图

5 结 语

本文提出一种基于ARM和FPGA的音圈电机驱动控制系统,完成了音圈电机式振镜驱动电机控制板的设计和验证,根据芯片各自的功能特点进行功能划分。仿真实验表明,设计的驱动电路板可以实现所需功能,并且功能划分也实现了系统硬件的资源合理配置,保证控制系统实时性要求。