应用SpaceWire网络的智能处理通用平台设计

苏斌嫔,吴志华,尹增山,王 宁

(1.中国科学院 微小卫星创新研究院,上海 201203; 2.上海微小卫星工程中心,上海 201203;3.山东航天电子技术研究所,山东 烟台 264003)

0 引言

随着航天技术的发展及复杂实时任务的需求牵引,卫星系统设计向着更精细、更智能方向突破。智能处理通用平台,是应用于大规模星座系统,旨在实现卫星节点在轨高速载荷数据实时处理、多源信息跨时空融合、图像信息智能深度分析、在轨自主任务规划、海量数据存储功能的综合电子平台。

智能处理通用平台连接的载荷设备种类各异,信息量越来越多,有必要采用统一标准高速接口,使得新载荷设备能够快速集成到新型号任务中;此外,智能处理通用平台中各单机、模块间随着应用场景的变化也存在多种组合的数据交互,如果采用传统的CPU三总线的控制方式,势必增加设备各电路板间的依赖性,不利于功能扩展,因此内部电路板间也采用串行总线互联的方式。

为解决上述问题,本文提出应用SpaceWire网络的智能处理通用平台设计,实现外部接口设备、内部各电路板间的互联互通。SpaceWire总线网络是欧空局ESA提出、多个空间科学机构共同制定并不断迭代的新型通信标准,已成功应用于ESA、NASA多项国际航天任务中[1-3]。国内在气象卫星、科学卫星中也成功部署应用[4-21]。该总线具有高速(最高传输速率为400 Mbps)、可靠、低功耗、接口简单、路由式通信的特点,对实现星载智能处理通用平台高速数据交互、易扩展、可重构、标准接口具有重要基础支撑作用。

1 智能处理通用平台系统设计

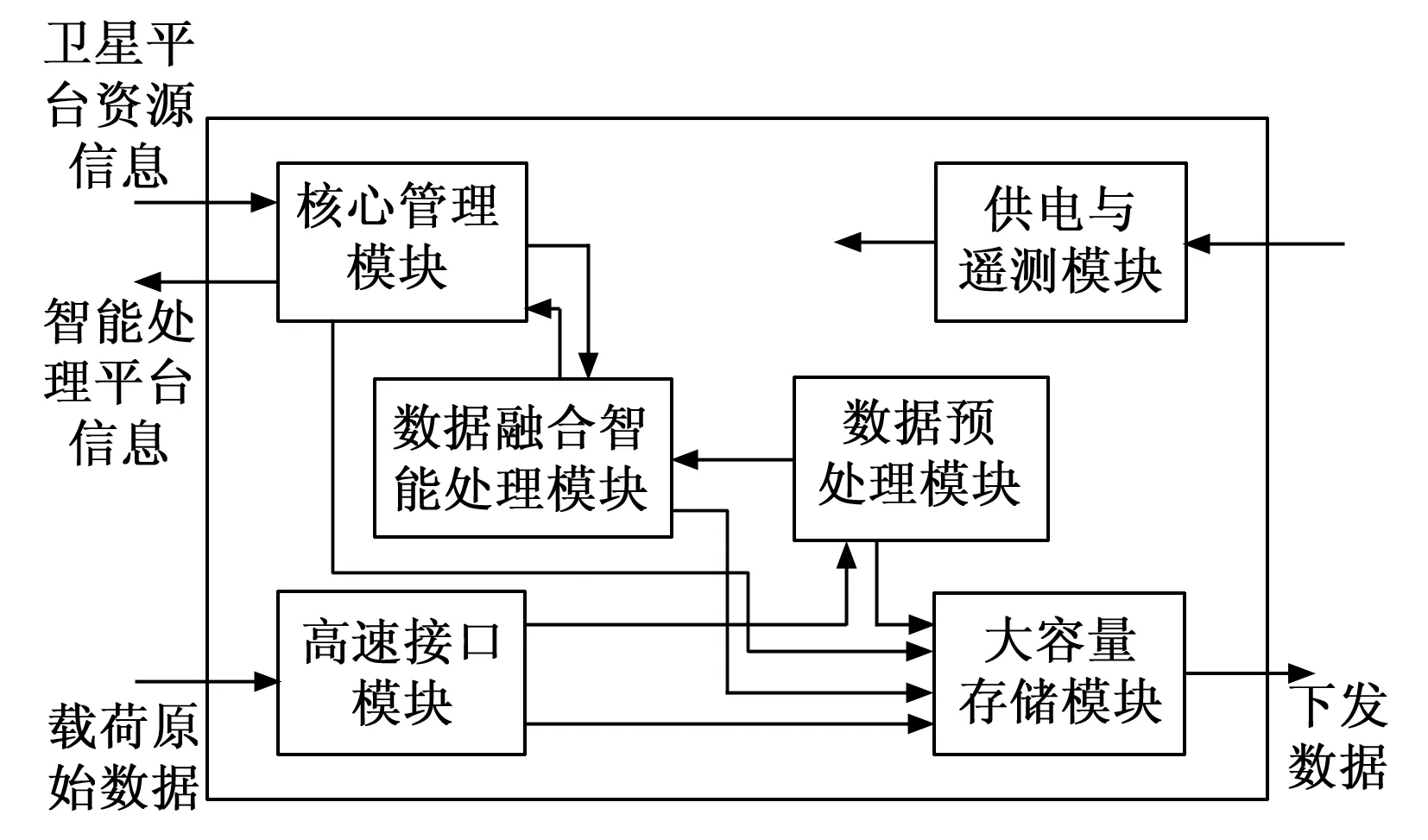

智能处理通用平台是卫星载荷管理、数据处理、存储分发、信息交互的核心,旨在实现卫星载荷数据实时处理、多源信息融合、信息智能深度分析、在轨自主任务规划和大容量存储下发功能,划分为供电与遥测模块、高速接口模块、数据预处理模块、数据融合智能处理模块、核心管理模块、路由模块(隐含模块)、大容量存储模块共七部分,其内部信息流图如图1所示。高速接口模块负责接收载荷原始高速数据,载荷数据经预处理后进行多源融合、目标检测、识别,核心管理模块实现资源管理、任务调度和故障容错等,载荷原始数据、数据处理过程中高价值信息以及卫星平台信息均存入大容量存储模块,等待下发。路由模块旨在实现智能处理平台与外部以及内部各模块间的数据交互。

图1 智能处理通用平台内部信息流图

1.1 总线选择

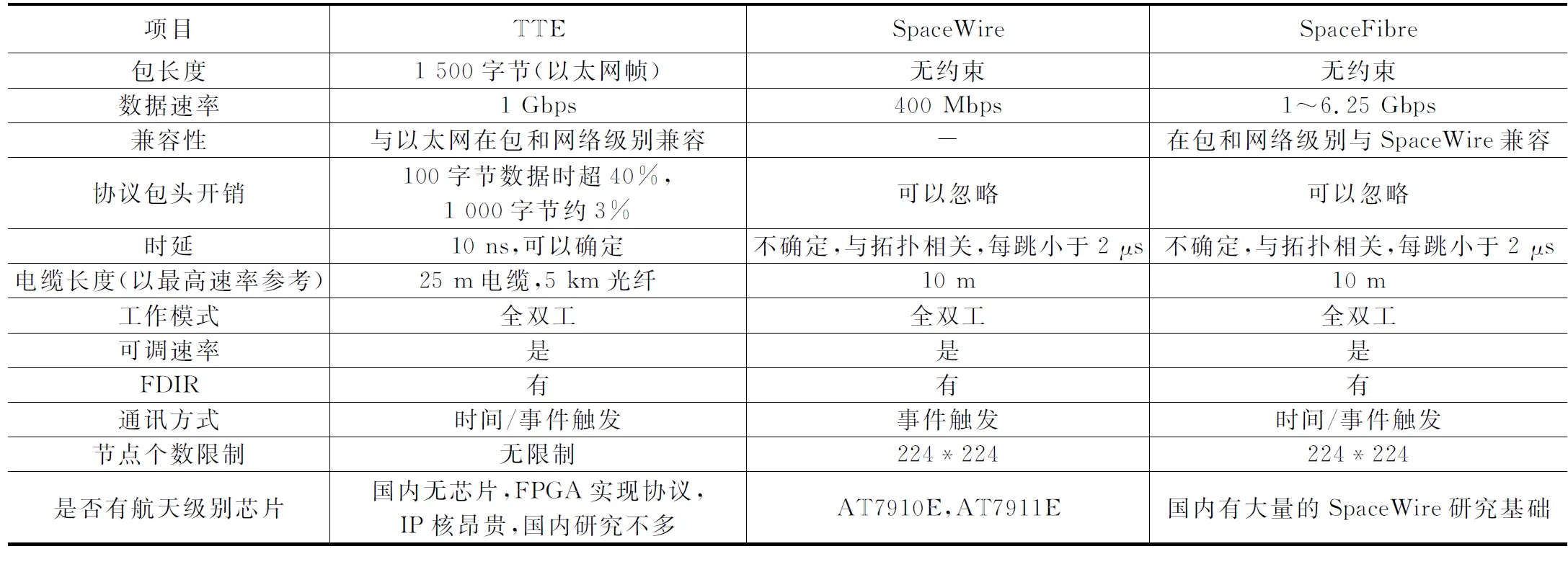

智能处理通用平台、载荷以及平台各模块间存在大量数据交互,传输的大多是对带宽有较高要求、对时间不太敏感的载荷数据或切片数据。传统的高速载荷数据传输通常采用LVDS点对点传输,不能形成高速数据网络适应各类数据交互组合的应用场景。时间触发以太网(TTE)是一种时间确定性网络,美国宇航局猎户座飞船(新一代航天飞机)使用时间触发以太网(TTE)作为主干网,其高速、可靠特性在轨道交通、机器人等领域也有广泛应用。SpaceWire是一种高速低耗的网络连接方式,以IEEE 1355-1955协议和LVDS标准为基础,由ESA联合邓迪大学共同研发。此外,在SpaceWire空间网络标准基础上升级研发的SpaceFibre总线,能够实现超高速串行链路与组网互联。下面对几类应用于航天的高速总线特性进行比较说明。

综上,从航天应用需求满足、系统未来可扩展以及现有技术可达的角度,选用SpaceWire总线作为智能处理通用平台高速数据传输途径。

1.2 总线网络拓扑

智能处理通用平台总线网络构成如图2所示。载荷设备、智能处理平台模块、数传发射机均连入SpaceWire网络,实现数据交互、处理、下发全流程。每类模块根据应用需求配置1-N块,SpaceWire网络通过路由器进行级联,形成网状结构,实现各模块、单机间互联互通。

图2 SpaceWire网络拓扑图

在实际应用中,光学载荷数据量极大(Gbps带宽),此类载荷通常不直接接入SpaceWire网络,经载荷数据预处理后生成百兆级有效数据后,接入网络进行深度处理、融合分析以及存储。

本文中拟采用统一的硬件接口和标准通信协议,屏蔽网络内部连接细节,使得用户可实现SpaceWire接口即插即用,任意两者之间实现动态链接,建立一对一、一对多、多对一的传输通道。

1.3 寻址方式

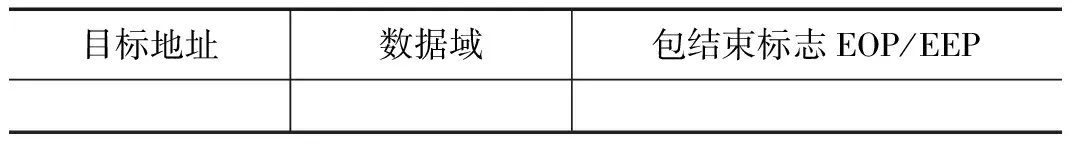

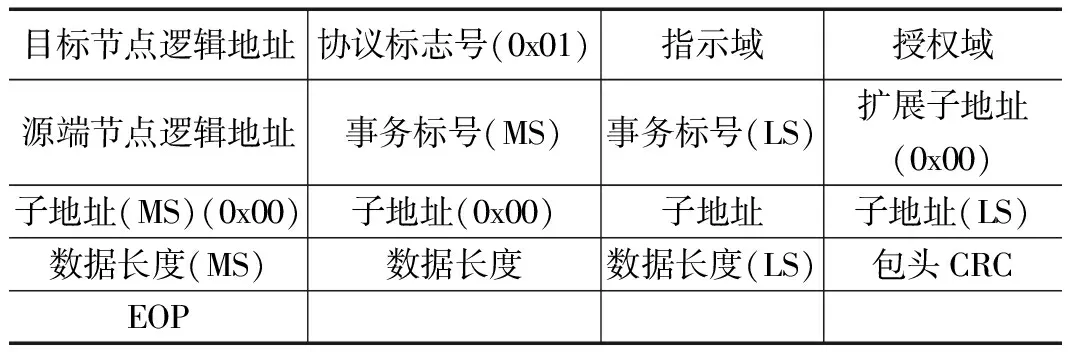

SpaceWire总线数据包层协议继承了IEEE1355-1995定义的数据包装协议,规定了总线源端到宿端的数据包装格式。数据包格式定义如表2所示。

表1 高速数据总线传输特性

表2 SpaceWire总线数据包格式

其中,目标地址根据SpaceWire网络结构及传输路径情况来确定;包结束标志EOP/EEP,表示传输的数据包正确或错误。EOP/EEP末尾就默认传输新的数据包。

SpaceWire网络有2种寻址方式:

1)路径寻址。通过物理端口指定数据传输目的地,各级路由节点具有包头删除功能,将通过的数据包首字节删除,把第2个字节作为数据包的新包头首字节地址送出。

2)逻辑寻址。将SpaceWire路由器的物理端口通过路由表映射到某一个逻辑地址上,通过查找路由表确定逻辑地址对应的输出端口,目标地址只需要由一个数据字符长度的逻辑地址来表示。利用逻辑寻址方式不需要关注具体网络结构,因此可屏蔽网络连接细节。

本文设计中,应用数据交互采用逻辑寻址方式,基于路由表查找目的地。各个载荷设备、模块将各自的应用数据按照表2组包,数据包通过各级路由时,在路由器控制下逐级传输至指定逻辑地址对应的某路由某端口直连的目的单机或模块。

1.4 协议定义

智能处理通用平台中应用SpaceWire总线传输的数据包括两类,应用数据和路由配置数据。

传输的应用数据,包括载荷设备业务数据、载荷观测数据、预处理数据、切片数据、融合处理数据、任务请求以及载荷设备控制信息等。数据域格式采用CCSDS标准数据包格式,设计为定长格式,如表3所示。包主导头定义中应用过程标识符(APID)区分各类应用数据。

表3 数据域格式定义

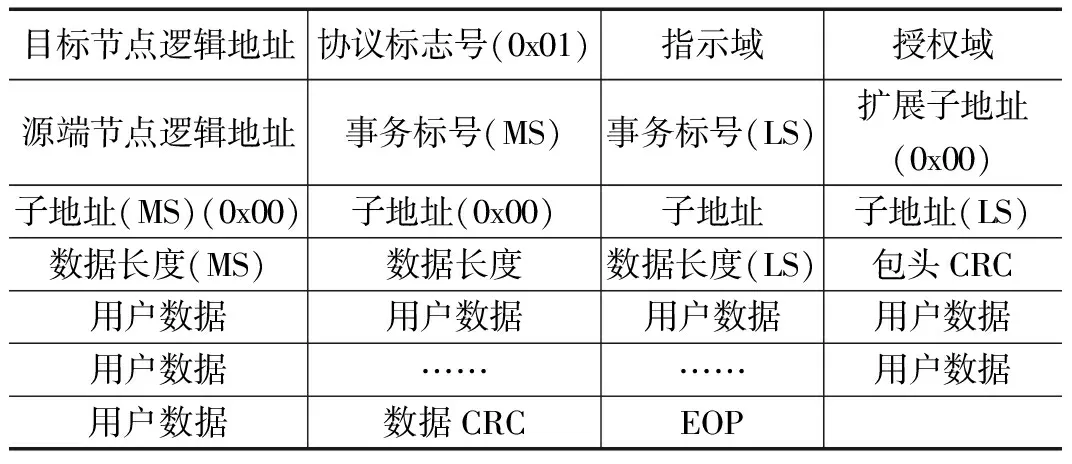

配置数据包括各个节点的端口状态、通信速率、路由表等,配置成功即可为各载荷设备提供数据传输服务。对路由器的管理采用远程存储器访问协议(RMAP)进行配置,并读出内容以确认配置正确。依据ECSS-E-ST-50-12C标准,RMAP写入操作和读出操作命令如表4和表5所示。

表4 RMAP写操作命令包

表5 RMAP读操作命令包

1.5 系统重构及冗余设计

为提高系统可靠性,载荷设备电子学、数传发射机以及智能处理通用平台中预处理模块、智能处理模块、核心管理模块、路由模块和大容量存储模块等均采用冷备份设计,当部分模块故障时可以通过切机操作对系统重构,保障系统能力的迁移,提高容错能力。系统重构,会对应用数据在SpaceWire网络的传输路径重新组织,抵达到新的物理端口。

应用SpaceWire网络的智能处理通用平台,适用于不同卫星应用场景,在不改变智能处理通用平台硬件设计的情况下,可以通过配置路由表和更新软件,即能将载荷设备快速接入新的型号中。

2 实例设计

某卫星中配置2个载荷设备(电子学冷备份),智能处理通用平台中配置2块预处理板(含主备)、1块智能处理板(含主备)、1块核心管理板(含主备)、1块存储控制板(含主备,后端连接多块Flash存储器)、X波段发射机(含主备),以此为例,介绍SpaceWire网络的软硬件设计。

2.1 硬件设计

SpaceWire网络核心是协议芯片,协议芯片代表有两款,AT7911E和AT7910E。AT7911E提供3组高速SpaceWire链接;AT7910E是一款SpaceWire路由器芯片,它包含8路SpaceWire接口、2路外部并行端口和1个内部配置端口。它支持存储器DMA功能和虫洞路由功能,可以用作独立路由器,也可以作为外部设备接入SpaceWire网络的连接节点。本文构建基于AT7910E芯片的SpaceWire网络,具体实现如图3所示。

图3 智能处理通用平台SpaceWire网络连接图

使用3片AT7910E芯片,各路由芯片通过链路1和8端口串联在一起,形成一个环形,对外共提供18路标准SpaceWire端口。本设计中,载荷设备电子学、X数传发射机、智能处理各模块均采用冷备份设计,外部使用15路端口(含测试节点);各路由芯片两路双向并行端口9、10端口连接FPGA,FPGA实现对各路由芯片控制、配置以及数据复接、大容量存储读写、坏块管理等功能;选用FPGA芯片为XILINX公司的Virtex-2系列,型号为XQ2V3000;3片路由芯片均与FPGA有直连通道,保障了存入大容量存储的数据可以及时存入,无需多跳流转。常态工作时仅有3个串联路由芯片以及8台载荷/设备/单板工作。

2.1.1 防静电接口电路设计

实际应用中发现,AT7910E的SpaceWire LVDS接口对电压较为敏感,静电、热插拔等可能造成LVDS接口的损坏,导致部分SpaceWire通道无法使用。为解决该问题,使用LVDS接口芯片进行转换保护,将AT7910E输出的SpaceWire LVDS信号,经SNJ55LVDS32W转为单端,该单端信号再由SNJ55LVDS31W重新转为差分信号输出;同理,外部输入的SpaceWire LVDS信号,先经SNJ55LVDS32W转为单端,该单端信号再经由SNJ55LVDS31W重新转为差分信号输送给AT7910E的LVDS输入端。电路设计如图4所示。

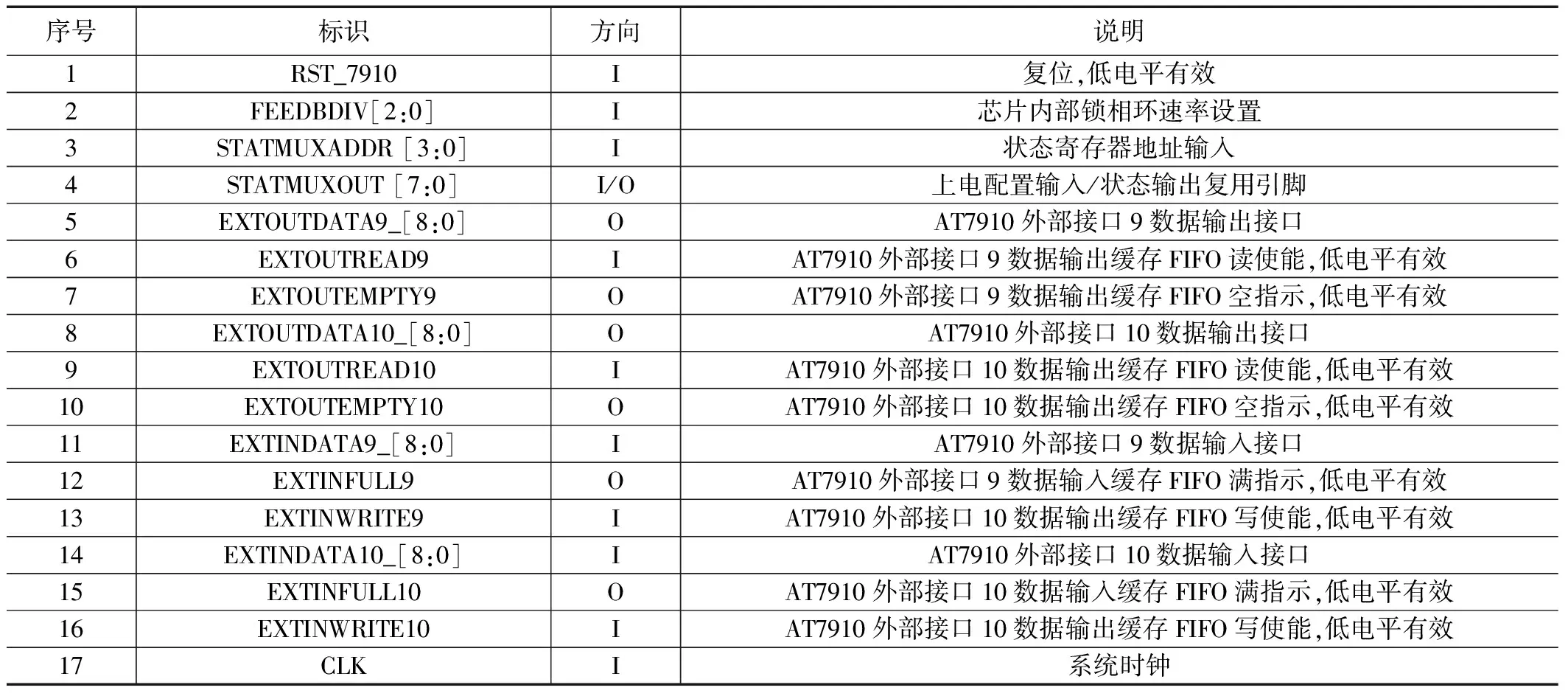

2.1.2 路由芯片与FPGA连接引脚

FPGA对AT7910E实现控制、配置以及并行端口的读写功能。FPGA与AT7910E间连接信号如表6所示。FPGA提供系统时钟和复位信号;上电配置输入和状态输出引脚复用;每个FIFO的读写都与系统时钟同步,每个端口提供了一个8bit的数据口和1bit控制口用于标识包的结束。

表6 AT7910E与FPGA连接信号

2.2 软件设计

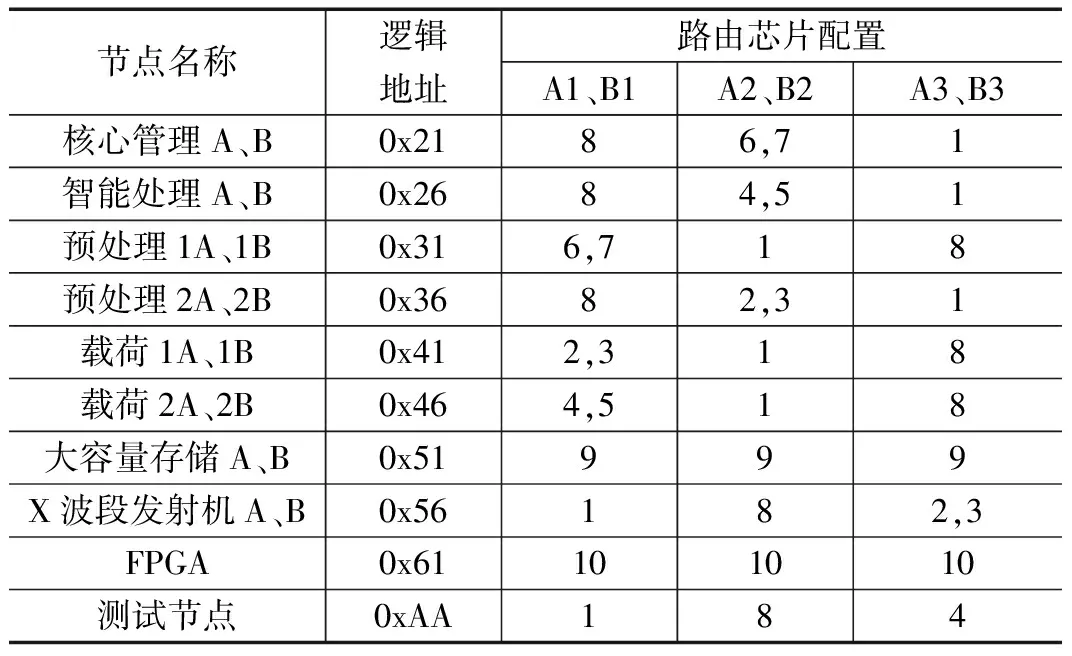

2.2.1 地址分配及组路由

本设计中,所有节点均为冷备份,采用逻辑寻址方式,逻辑地址分配范围是32~255。主备单机设计使用相同的逻辑地址,同一逻辑地址,其目的地对应主备设备直连的两个物理端口,为简化设计,主备机均与同一路由芯片存在直接物理链接。具体发送到哪个物理端口,自主寻址逻辑为:1)选择链接正常的链路,如果端口未加电、电缆断开或链接异常,则端口不可用;2)有唯一可用端口,则直接通过该端口发送;3)有多个端口可用时,编号小的端口具有高优先级。通过构造总线组路由实现多设备、模块之间的信息传输。逻辑地址分配及6片路由芯片的路由表配置如表7所示。

表7 地址分配和路由表配置

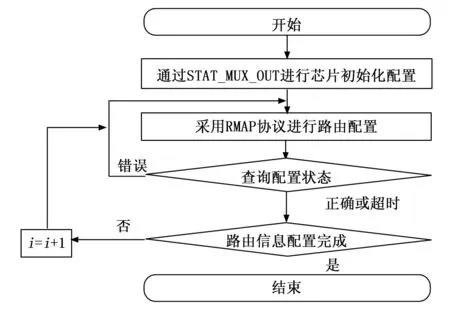

2.2.2 AT7910E初始化设置

AT7910E初始化流程如图5所示。

图5 AT7910E初始化流程

芯片上电或复位后,通过复位配置信号STAT_MUX_OUT对芯片进行初始化配置,配置空间的读写操作采用RMAP协议;为保证可靠性,配置完成后查询配置状态,如果配置失败,则重新配置,有限次数失败后转而执行下一个配置。配置状态信息遥测下发。

路由单元初始设置为AutoStart模式,主动监听各端口信号;而各载荷、设备、单模块节点初始设置为LinkStart模式,主动发送信号。两者握手成功,则建链成功。

2.2.3 AT7910E状态监测

在AT7910E工作期间,正常操作期间,通过配置输入/状态输出复用接口轮询地读取当前活跃链路的链路错误/状态寄存器,以获取当前链路状态(错误复位、错误等待、就绪、发起链接、链接中、运行中)和错误情况(包地址错误、输出端口超时错误、链接断开错误、奇偶校验错误、转义字符错误)。状态信息遥测下发供地面查看。

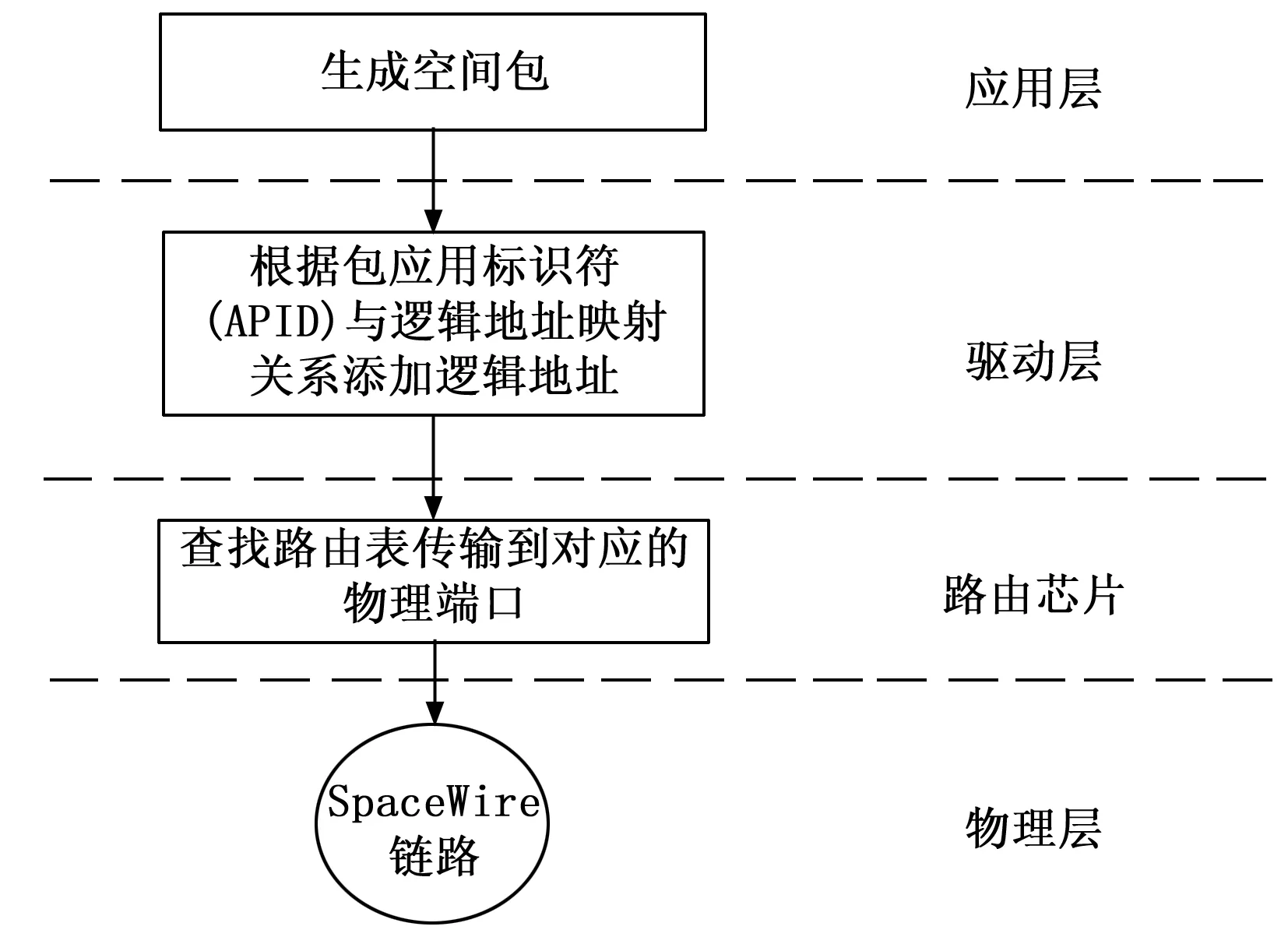

2.2.4 分层协议实现

SpaceWire网络中以标准空间包为单位实现星内数据交互,采用分层设计思想,实现应用层与数据链路协议的分离。分层协议如图6所示。

图6 协议分层实现示意图

2.3 应用效果分析

将应用SpaceWire总线的智能处理平台与无网络连接的智能处理平台进行多维度比较,结果如表8所示,可见,本文设计优势明显,接口种类少,协议标准,支持应用重构且支持系统扩展。

表8 应用效果对比

3 测试验证

3.1 测试环境

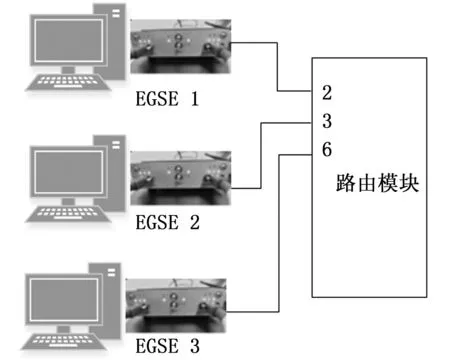

搭建测试环境如图7所示。

图7 测试环境

用3块邓迪公司的SpaceWire EGSE模块分别接入到图8路由模块端口2、3、6,进行载荷模拟。EGSE通过usb接口接入PC上位机,通过脚本语言实现数据发送与接收。路由表配置如表7所示。

3.2 测试步骤和结果

3.2.1 数据传输速率测试

路由2端口连接的EGSE 1作为载荷源节点,发送载荷图像数据(对应逻辑地址0x31)经路由达到EGSE 3模拟的载荷数据预处理板,设置传输速率为200 Mbps,分别比对源节点发送和目标节点接收的二进制文件和光学灰度图(图8),数据完全一致,测试通过。

图8 源端和接收端数据比对

3.2.2 切机后自主寻址测试

EGSE 1和EGSE 2分别模拟载荷1的主备机,路由模块内部FPGA以1 s周期性发送100字节数据包(对应逻辑地址0x41)给载荷,当EGSE 1加电时,EGSE 1连接的上位机软件接收到源端数据;当EGSE 2加电时,EGSE 2连接的上位机软件接收到源端数据。测试通过。

3.2.3 应用重构测试

EGSE 3模拟指令发送端发送新的路由配置表(路由表对应逻辑地址0x61),与测试1的路由配置表不一致,给到路由模块直连的FPGA;重启路由模块后,EGSE 1发送与测试1相同的载荷数据(对应逻辑地址0x31),EGSE 3连接的上位机不再接收到载荷数据,此处与测试1测试结果不一致,EGSE 2连接的上位机接收到数据,与新的路由配置表设置一致,测试通过。

4 结束语

通过以上设计、分析以及基于SpaceWire路由单板和模拟设备的测试,实现了SpaceWire总线在智能处理通用平台中的应用。SpaceWire总线有助于提高数据传输速率、简化星载设备连接,同时增强设备的重用能力、可维修性和可扩展性,从而降低开发成本,提高研制效率。本智能系统目前已经处于整机原理样机联调过程中,将应用于大规模星座中,其支持挂接节点数量大于18个,根据需要可继续扩展;单节点速率在2~400 Mbps之间调节;系统内冗余备份,支持系统重构。此外,随着SpaceWire空间网络标准基础上升级研发的SpaceFibre总线的技术推广应用,本系统可以通过桥接扩展方式能够实现超高速串行链路与组网互联,未来有更大的发展空间。