小尺寸应变SOI SiGe异质结双极晶体管

苗乃丹,王冠宇,文剑豪,于明道,周春宇,王 巍

(1.重庆邮电大学 光电工程学院,重庆 400065;2.燕山大学 理学院,河北 秦皇岛 066004)

0 引 言

高性能的异质结双极型晶体管(hetero-junction bipolar transistor, HBT)与低功耗的互补金属氧化物半导体(complementary metal oxide semiconductor, CMOS)大规模集成使得BiCMOS技术在电子工业得到了广泛的应用。随着SiGe HBT技术的不断发展,其优异的高频特性和与成熟硅工艺相兼容的优势,广泛应用于高性能微波射频器件与电路之中[1-2]。目前国内外的研究机构和学者都致力于利用各种技术手段优化SiGe HBT的频率性能,充分挖掘其在高频应用中的潜力[3-6]。

随着集成电路的特征尺寸不断减小、集成度不断提高,器件的小尺寸化成为主流趋势。为了与CMOS性能匹配,SiGe HBT的横向和纵向尺寸也相应减小。由文献[7]可知,当SiGe HBT的横向几何尺寸,尤其是发射极宽度向着更小的节点发展,器件的频率特性会大幅度提高。

鉴于此,为了使SiGe HBT能更好满足现代通信系统对高工作频率的要求,在缩小器件尺寸的同时,可以将传统的绝缘体上硅(silicon on insulator, SOI)技术和应变硅技术相结合。SOI技术可以有效抑制闩锁效应,并且具有工作速度快、功耗低、成本低、抗辐照性能好等优点,因此,SOI衬底相比于传统的体硅衬底具有相当明显的优势。印度理工学院团队学者P.K.Misra, S.Qureshi[8-9]对SOI HBT进行了模拟研究,提出了一种利用N+埋层提高薄膜SOI SiGe HBT性能的方法,并可以兼容于130 nm SOI CMOS技术。另外,在先进的半导体器件技术中,通过引入全局应变或者局部应变改变了硅的能带结构,提高了器件载流子迁移率,因此,可以作为附加特性来进一步提高载流子的输运性能。国外学者分别提出了引入堆叠式金属互联线结构和机械应力[10-11],可以提高SiGe HBT的性能,但是可靠性较差,工艺过程不易控制。文献[12]提出了一种虚拟衬底的SiGe HBT器件结构,通过减小载流子在集电区的渡越时间,提高了频率特性以及电流增益,但同时造成器件的自加热效应显著。文献[13]提出了一种在SiGe HBT集电区填充SiO2的单轴应力引入技术,其截止频率和最高振荡频率分别提高了约14%和9%,约翰逊极限(电流增益与击穿电压之积)β×BVCEO提高了约12%,但是器件中淀积SiO2不同于浅沟槽隔离工艺,在和CMOS集成的时候有些困难。

综上,本文所研究的新型SOI SiGe HBT器件结构具有尺寸小、与CMOS技术相兼容的特点,同时将SOI技术与应变硅技术相结合,在具有N+埋层的SOI集电区中引入单轴应力,形成一种新型SOI SiGe HBT器件结构。针对发射区、基区和集电区的设计进行了器件模型仿真,进而分析影响器件性能的关键因素,为器件的设计和优化提供理论基础。

1 器件结构以及工艺仿真流程

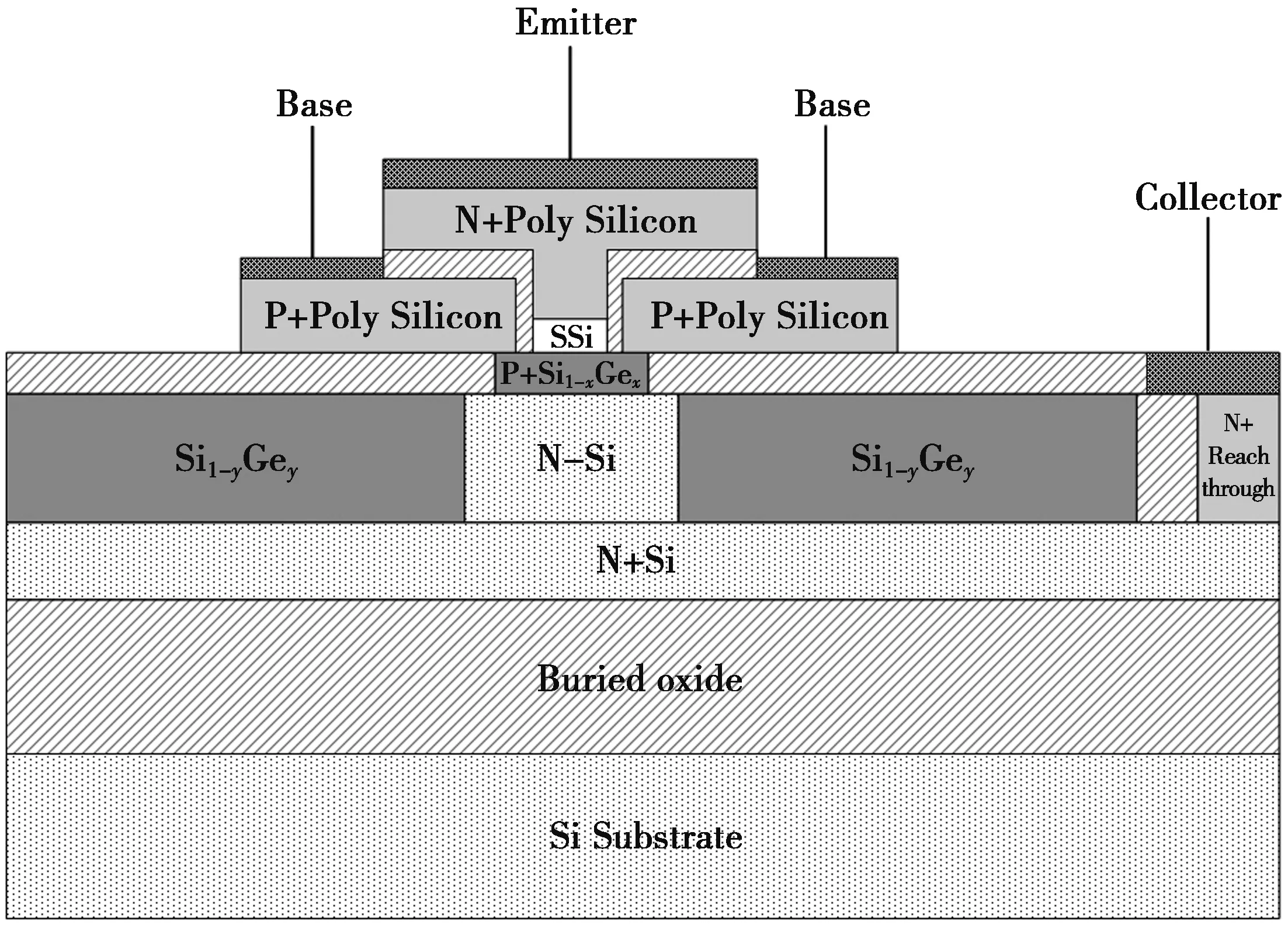

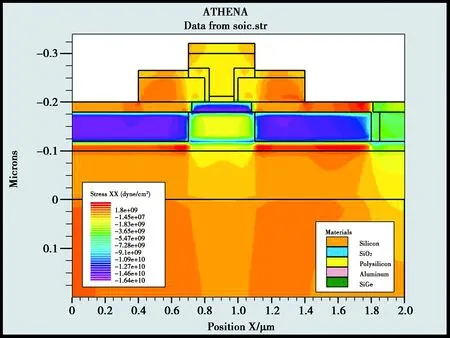

本文主要使用半导体仿真工具SILVACO©TCAD软件,利用ATHENA工艺仿真模块建立了二维器件模型,NPN型SOI SiGe HBT的器件结构如图1。

图1 新型SOI SiGe HBT器件结构仿真图Fig.1 Structure of proposed SOI SiGe HBT device

该SOI SiGe HBT器件发射区窗口为120 nm,集电区窗口为400 nm,符合文献[7]的尺寸缩小路线图。该器件结构的特点主要体现在应力的分布,首先在集电区引入嵌入式Si1-yGey源漏应变技术,使集电区硅材料在水平方向受到单轴压应力,然后在集电区硅层上生长Si1-xGex基区,由于Si和SiGe材料晶格常数的不同,使基区受到双轴压应力[14]。根据弹性力学的原理,受到集电区单轴压应力的影响,基区受到的是单轴应力和双轴应力组合的复合应力。由于发射区存在一层硅帽层(cap layer)受到了单轴压缩应力的作用,从而构成了应变硅(strained silicon, SSi)/多晶硅的双层组合发射极结构[15]。器件结构参数和工艺参数如表1。

需要说明的是,图1中的器件结构并非为对称结构,电极分布方式为C-B-E-B,这种引出4个电极的分布方式可以节约器件的版图面积。另外,该结构也是为了与CMOS集成构成BiCMOS器件,常规的SiGe BiCMOS器件通常为非对称结构。

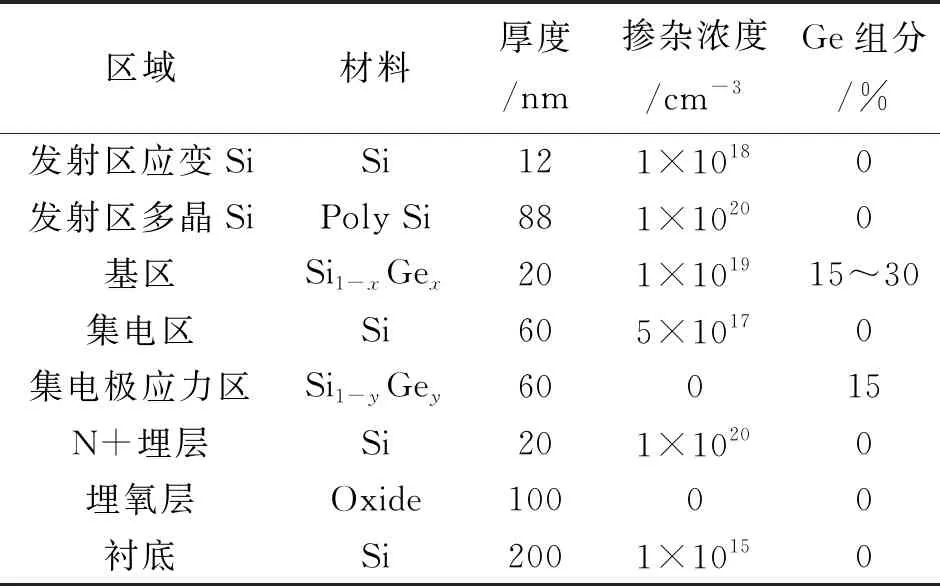

表1 SOI SiGe HBT结构参数

该新型小尺寸SOI SiGe HBT利用ATHENA的工艺仿真流程主要包括以下7个步骤:①初始化(100)晶向P型Si衬底;②该衬底完全耗尽满足ETSOI(extremely thin silicon on insulator)准则[16](Tsi=LG/3)可以选择65 nmCMOS工艺。集电区埋层进行二氟化硼(BF2)离子注入,注入剂量为8×1014cm-2,注入能量为30 KeV;③在埋层上方淀积生长60 nm的掺磷N型外延层,将N-集电区外延层刻蚀出应力区域,通过选择性淀积,对集电区淀积Si1-yGey材料(y=15%);④刻蚀出集电区电极引出穿通区域,淀积重掺杂多晶硅,作为集电极穿通区;⑤在850 ℃的温度下生长绝缘层SiO2,作为隔离层,隔离集电区与外基区;⑥依次淀积P型Si1-xGex基区、重掺杂P型多晶硅外基区和组合发射区,并使用低压化学气相沉积(low pressure chemical vapor deposition,LPCVD)模式淀积SiO2薄膜和多晶硅;⑦对整个表层溅射金属Al作为金属层,光刻去掉发射极、基极、集电极以外的金属层,并形成各区域的引线,作为电极。

2 发射区的能带分析

本文通过在集电区淀积Si1-yGey材料将应力引入到器件中,纵向传导使发射区的帽层也受到了应力。该新型器件结构采用的是组合发射区,由重掺杂的多晶硅和应变硅2部分组成。通过减小发射区的延迟时间可以提高SiGe HBT的频率特性,主要降低串联电阻与结电容。发射区重掺杂多晶硅减小了发射区接触电阻,应变硅提高了电子的迁移率,从而提高发射区注入效率,提高电流增益。

发射区的多晶硅与单晶硅之间存在着一层极薄的类似于氧化层的界面态,称之为“类氧化层”。发射区到基区的纵向能带结构如图2,电子的势垒高度χe远小于空穴的势垒高度,“类氧化层”不会影响从发射区注入基区的电子,对电子而言几乎是“透明”的。而空穴势垒高度χh阻碍了从基区到发射区反向注入的空穴,此时的空穴电流通过量子隧穿渡越界面氧化层。

图2 多晶硅/界面氧化层/应变硅系统的能带结构Fig.2 Polysilicon/interface oxide/strained silicon energy band

此“类氧化层”的形成,使纵向载流子的输运效率得到了提高,从而使发射区渡越时间τe减小,渡越时间与电流增益成反比关系,所以根据理论分析,这种发射区结构可以进一步提高器件的频率特性。

3 基区Ge组分分布对器件电流增益和厄尔利电压的影响

基区的设计主要从2方面考虑:①基区杂质的分布;②基区Ge组分的分布。本文在基区杂质浓度为均匀分布的基础上,主要研究Ge组分分布的不同对器件特性的影响,基区Ge组分的分布分为3种类型:均匀型、三角形、梯形。SiGe HBT基区Ge组分分布的不同会影响基区能带的禁带宽度,靠近发射区的一侧禁带宽度大于靠近发射区一侧的禁带宽度,基区形成了能带差,因此引入了自建电场[17]。Ge组分渐变使得通过基区的电子受到了加速电场作用,减少了基区渡越时间,进而减小基区复合提高了电流的放大倍数。

常见的SiGe HBT基区Ge组分的分布,X0为基区靠近发射区一侧的边界,XWB为基区靠近集电区一侧的边界,ΔEg(X0)为X0处Ge组分引起的禁带宽度变窄量,ΔEg(XWB)为XWB处Ge组分引起的禁带宽度变窄量。

通过(1)式得到基区Ge组分缓变分布与电流增益β的关系[18],可以得出,SiGe HBT的电流增益和Si BJT的电流增益之比βSiGe/βSi与ΔEg(X0)呈指数关系,而与基区Ge组分缓变引起的带隙差ΔEg,grade呈线性关系,如(2)式,因此,可知靠近发射区的Ge组分对电流增益的影响较大。当基区Ge组分含量不变的情况下,梯形分布的电流增益比三角形分布的电流增益要大。

(1)

ΔEg,grade=ΔEg(XWB)-ΔEg(X0)

(2)

(1)—(2)式中:k为系数,T为温度。

厄尔利电压与基区Ge组分的关系由(3)式可知[18],可以看出,厄尔利电压与带隙差ΔEg,grade成正比,随之增大而增大。

(3)

可以得到电流增益与厄尔利电压优值的关系[18]为

(4)

由(4)式可知,在基区Ge组分不变的情况下,Ge组分均匀分布的电流增益与厄尔利电压积小于基区Ge组分渐变时的情况。

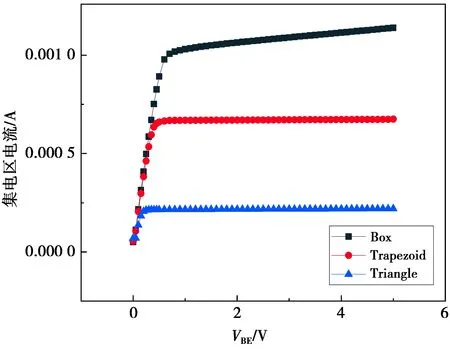

基于上述器件模型,得到3种基区Ge组分分布方式对电流增益的影响。β-VBE曲线如图3,可以看出,基区Ge组分为均匀型和梯形SOI SiGe HBT的增益比较高,高于常规的SiGe HBT。其中,基区Ge组分均匀分布的最大增益βmax为2 415,梯形分布的βmax为1 062,三角形分布的βmax为273。可以看出,均匀型的电流增益最高,符合上述理论分析。

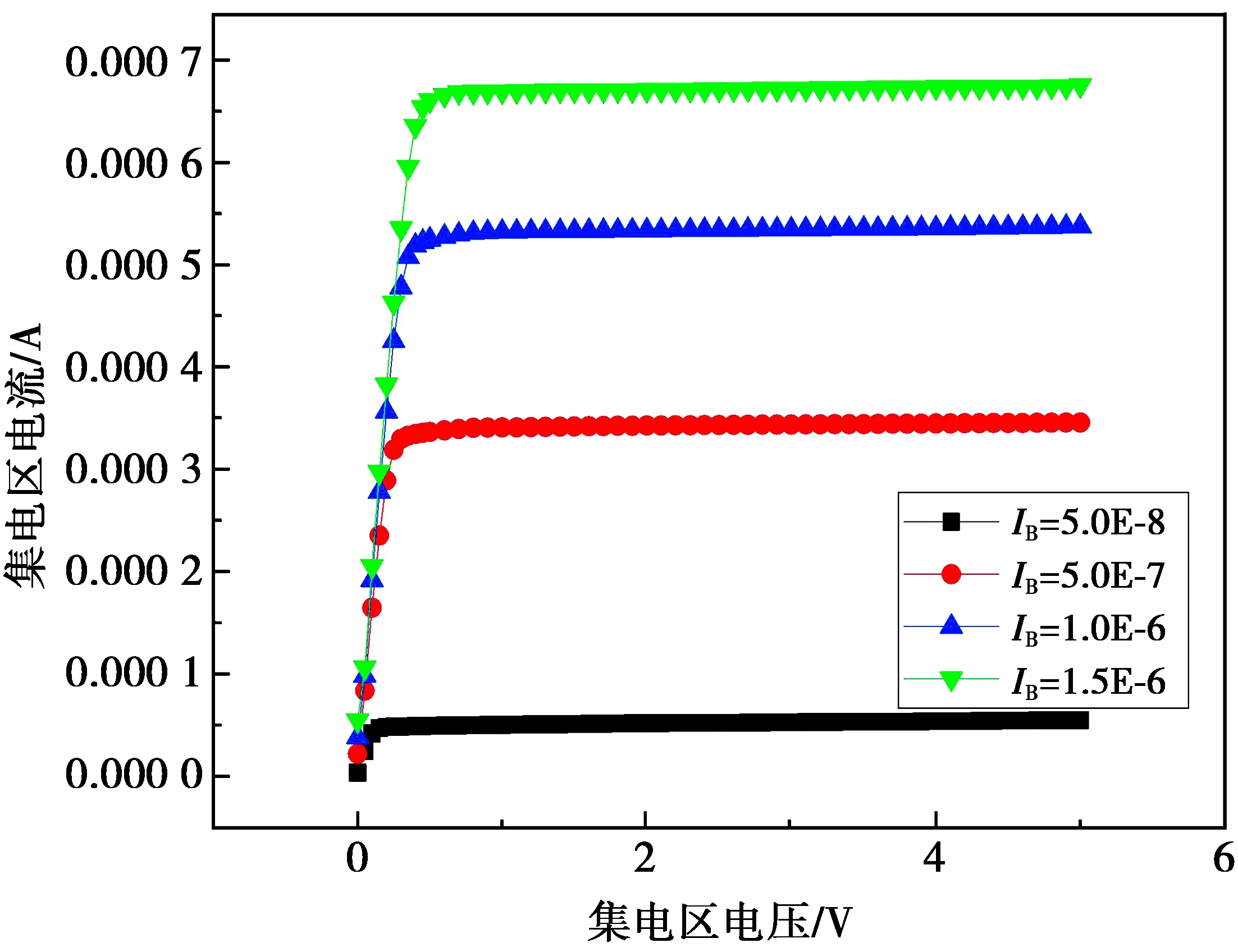

厄尔利电压是表征器件电学特性的重要参数之一,厄尔利电压值越大,基区宽度调变效应越小,使基区少子浓度梯度增加,从而增大了电流增益β。厄尔利电压值的提取是通过确定各条IB为不同常数时的IC-VCE曲线在VCE接近于零时的切线交于横坐标的值,即为VA。所以当IC-VCE曲线越平坦,VA就越大,器件的输出特性就越理想。当SOI SiGe HBT的基区Ge组分分布为梯形时对结构进行器件的输出特性仿真,如图4,分别选取IB为0.05,0.5,1,1.5 μA时的IC-VCE曲线,可以看出曲线趋势较为平坦,通过计算可以得出厄尔利电压VA约为186 V。

图3 3种基区Ge组分分布形式的电流增益与发射结电压(VBE)的关系Fig.3 Relationship between current grain and VBE with three different distributions of Ge components in the base

图4 基区Ge组分为梯形分布时器件的输出特性曲线Fig.4 Output characteristics of the device when the Ge component of the base region is trapezoidal

图5为在基极电流IB为固定值1.5 μA时,将3种不同的基区Ge组分分布的输出曲线合并,可以看出Ge组分分布对器件输出特性曲线的影响。由图5可以看出,三角形分布和梯形分布的曲线较为平坦,而均匀型分布的曲线倾斜度最大,可知厄尔利电压VA最小。通过计算得知,梯形分布的厄尔利电压VA约为186 V,三角形分布约为224 V,均匀型分布为43 V。

图5 3种基区Ge组分分布形式下的器件输出特性曲线(IB=1.5 μA)Fig.5 I-V characteristics of the three base Ge distributions (IB=1.5 μA)

由仿真数据可得,3种Ge组分分布β×VA的最大值:均匀型1.038×105V,梯形1.975×105V,三角形6.115×104V。可以得到结论,当基区Ge组分为梯形分布时,电流增益和厄尔利电压的优值最高。

4 基区Ge组分分布对频率特性fT的影响

衡量器件电学特性的重要参数之一是截止频率fT,基区Ge组分的改变主要影响了基区渡越时间τB、发射区渡越时间τE,减小这2个时间常量可以有效提高器件频率特性[19]。当SiGe HBT的基区Ge组分为缓变时,基区渡越时间和发射区渡越时间与基区Ge组分的关系为

(5)

(6)

(5)—(6)式中,ΔEg,grade为Ge组分缓变时梯度差引起的能带带隙差。由(5)式可以看出,由于带隙差的存在使得τB,SiGe小于τB,Si。因此,基区Ge组分缓变引起了能带渐变形成了加速电子漂移的自建电场,从而使少子渡越基区的时间变短。由(5)式可以得出,当基区Ge组分梯度增大,截止频率fT会随之增大。由(6)式可知,τE,SiGe/τE,Si的比值与靠近发射区一侧的Ge组分引起的禁带宽度变窄量ΔEg(X0)成反比例指数关系,而与ΔEg,grade呈线性关系。所以,影响发射区渡越时间τE,SiGe的主要变量为ΔEg(X0)。当基区Ge组分为梯形分布式,靠近发射区一侧的Ge组分浓度不为0,使ΔEg(X0)和ΔEg,grade同时增大,可以有效减小发射区渡越时间,从而提高截止频率fT。

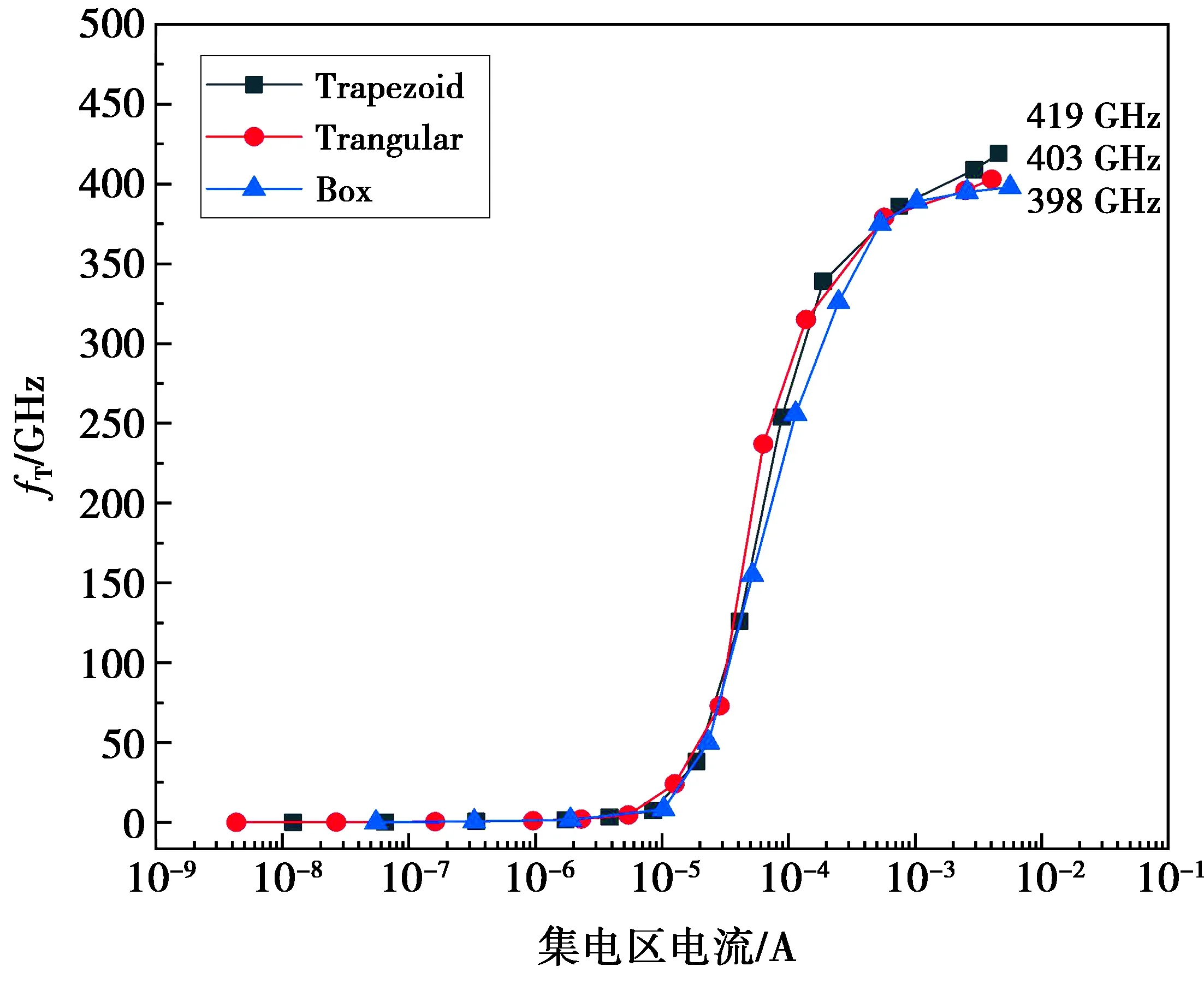

利用ATLAS仿真模块得到不同基区Ge组分分布的小尺寸SOI SiGe HBT的频率特性如图6。在VCE=4 V时,基区Ge组分为梯形分布时截止频率fT最大,为419 GHz;三角形分布时fT为403 GHz;均匀型分布时fT为398 GHz。综上所述,本文设计的新型SOI SiGe HBT器件基区Ge组分选用梯形分布。

图6 不同基区Ge组分SOI SiGe HBT的fT随Ic变化曲线Fig.6 fT versus Ic curve for Ge component SOI SiGe HBT in different base regions

5 集电区施加单轴应力对频率特性fT的影响

小尺寸SOI SiGe HBT电学特性的仿真利用的是ATLAS二维器件仿真模块,主要用到的模型有浓度依赖迁移率模型(conmob)、平行电场依赖模型(fldmob)、俄歇复合模型(Auger)、Shockley-Read-Hall复合模型(SRH)、能带变窄模型(bgn)、应力模型(stress)、能量平衡传输模型(energy balance)和费米狄拉克统计模型(Fermidirac),运用Newton迭代法和Gummel迭代法进行数值计算。

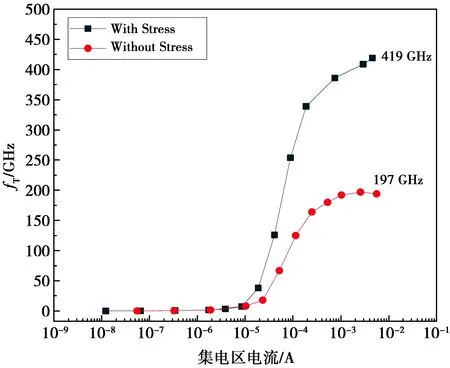

SOISiGe HBT集电区的结构设计同样影响器件的频率特性,集电区延迟时间τC越小,截止频率越大。与单轴应变硅CMOS工艺类似,本文创新性地在集电区中引入嵌入式Si1-yGey源漏应变技术,如图7,对集电区施加应力,由于压应力的存在使电子纵向通过集电区的速度增大,所以集电区的延迟时间会进一步减小。将本文设计的新型SOI SiGe HBT器件集电区加Si1-yGey(y=15%)源漏应变区和传统的不加应力的SOI SiGe HBT器件截止频率进行对比。当VCE=4 V时,在不同的VBE下,fT如图8。由仿真结果可知,传统的集电区未施加应力的SOI SiGe HBT的截止频率fT最大为197 GHz,而改进的集电区施加Si1-yGey应力的新型SOI SiGe HBT器件为419 GHz,截止频率fT提高了1.1倍。

图7 SOI SiGe HBT应力分布图Fig.7 SOI SiGe HBT stress distribution

图8 传统的与新型SOI SiGe HBT的截止频率fT比较Fig.8 Comparison of cutoff frequency fTbetween traditional and proposed SOI SiGe HBT

由此可知,集电区优化后频率的提高大于基区优化后的频率提高,原因在于基区本来就很薄,基区的渡越时间τB提升有限,而集电区的厚度远远大于基区,因此,集电区的渡越时间τC提升空间很大。在集电区引入Si1-yGey应力源的情况下,可以大幅度提升器件的频率特性。

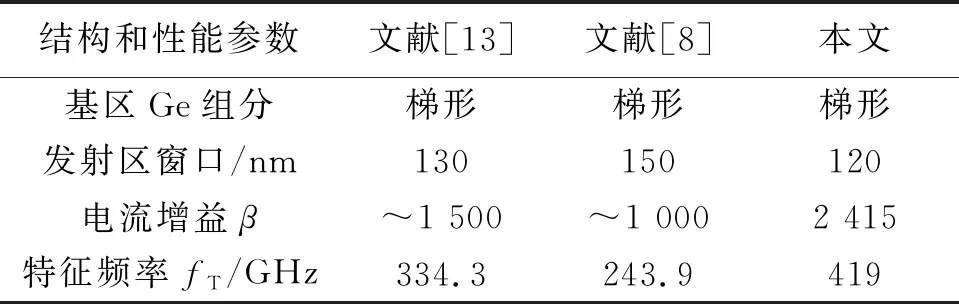

通过对本文引用文献中相似的器件结构性能指标进行整理,为了进一步说明本文所设计的器件性能,将本文的仿真数据与其他参考文献的性能参数进行了对比,如表2。

表2 不同SiGe HBT器件的性能参数对比

6 结束语

由上述不同基区Ge组分分布对SiGe HBT工作特性影响的仿真分析可以得知,当基区Ge组分为均匀型分布时,电流增益最大值βmax为2 415,厄尔利电压VA为43 V,厄尔利电压与电流增益之积为1.038×105V,截止频率fT最大值为398 GHz;梯形分布时,电流增益最大值βmax为1 062,厄尔利电压VA为186 V,厄尔利电压与电流增益之积为1.975×105V,截止频率fT最大值为419 GHz;三角形分布时,电流增益最大值βmax为273,厄尔利电压VA为224 V,厄尔利电压与电流增益之积为6.115×104V,截止频率fT最大值为403 GHz。同时,当集电区添加应力时,相比较于不添加应力的器件结构,截止频率提高了1.1倍。另外,如前所述,本文所设计的器件性能参数与类似结构的SiGe HBT相比,也有了一定程度的提升。

综上所述,在小尺寸SOI SiGe HBT器件中,基区Ge组分改变了能带结构从而影响了器件特性,基区靠近发射区一侧的Ge组分ΔEg(X0)以及基区Ge组分缓变的梯度差ΔEg,grade是影响器件特性的2个重要因素。根据上述仿真结果,折中考虑,小尺寸新型SOI SiGe HBT器件的基区Ge组分梯形分布,且集电区添加应力,具有更好的电学特性和更高的频率特性。

本文所设计的新型小尺寸SOI SiGe HBT器件与主流的CMOS工艺相兼容,并对未来商用太赫兹Si/SiGe BiCMOS的电路设计和工艺集成具有一定的理论意义和参考价值。