基于FPGA的雷达信号采集系统设计

熊 淳,张荣福

(上海理工大学 光电信息与计算机工程学院,上海 200093)

引 言

在国民经济快速增长以及科学技术迅猛发展的大环境下,测控技术与仪器产业不断发展,各个行业如军事、医疗、体育、航天等对于仪器设备的要求越来越高,尤其是在高精度的检测以及监控中,仪器设备起着至关重要的作用,小型化、便携化随之成为普遍追求的目标。在实际应用中,要求信号采集系统具有实时性好、速率快、稳定性高的特点。为了能提取雷达信号中携带的距离、速度等信息,需要有高速的雷达采集系统对前端雷达信号进行精确的采集,方能保证解析出来信息的准确性。

目前有基于单片机ARM[1]的数据采集系统,应用此种方式设计的雷达采集系统,因单片机本身AD转换涉及中断进出需要时间,尽管只需几微秒,但会使整个雷达采集系统的转换速率不高。另外也有基于DSP构建的雷达采集系统[2],虽然其优势是可以实现将前端采集和后端数据处理紧密结合,但是由于在DSP中程序不可并行执行,所以该类采集系统在程序的执行力以及采集速度方面是一个劣势。

目前,随着采集技术越来越先进,总线技术的发展也提高了信号采集的速率和精度,许多对于采集精度要求特别高的雷达采集系统中都搭载了基于总线的数据采集板卡[3],如许多主流的生产商如NI、GAGE等都推出了满足各种场合需求的采集板卡[4]。虽然该系统可大大满足对于采样精度和速率的要求,但是采集板卡造价过于昂贵,且作为单独设备使用不利于携带也不适用于构成小型化的雷达系统。

基于上述问题,本文设计了一种以现场可编程逻辑门阵列(field programmable gate array,FPGA)作为主控制器的雷达采集系统[5]。FPGA作为雷达采集系统核心,控制前端信号产生、信号采集以及信号传输。该系统利用FPGA内部硬件并行的优势可以大大提高程序执行效率,提高采集速率。因FPGA内部具有可定制的电路,能在短时间内完成FPGA设计的迭代,相较大型数据采集板卡,基于FPGA的采集系统成本更低,且体积小更易携带,方便测量。

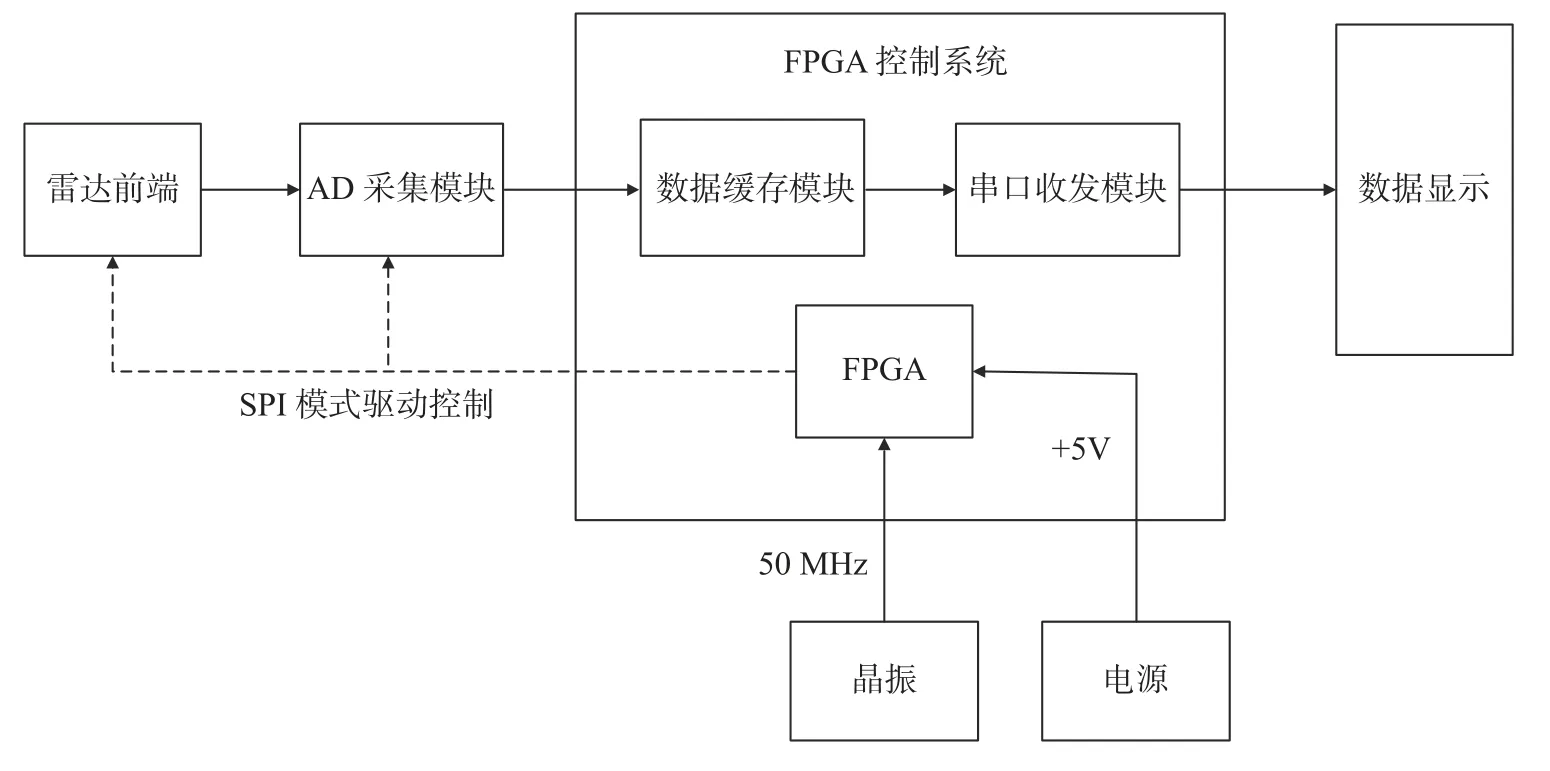

1 雷达采样系统组成

雷达采样系统的总体结构如图1所示,整个系统由雷达前端收发部分、AD采集部分、数据缓存部分、串口收发部分、数据显示部分等组成。雷达前端主要是由实验室雷达信号收发电路板构成,由FPGA生成控制信号驱动雷达前端ADF4158芯片[6]以及Infineon BGT24MTR12芯片[7]。ADF4158产生调制信号,BGT24MTR12产生24 GHz调频连续波雷达信号并对回波信号进行混频降频处理。AD采集部分利用AD7606芯片[8-9](最大采样率200 kHz)对经过混频以及取下变频以后的回波信号进行数据采集,由于中频信号经过降频处理,频率在几千赫兹。故本系统数据采样率定为20 kHz,一次采集1 024个点,以实现信号的完整采集。数据缓存部分利用FPGA内部RAM进行每次1 024个数据的缓存。数据收发部分利用UART串口转USB模式进行FPGA与上位机的通信。整个采集板卡的系统工作频率为50 MHz,供电电压为+5 V。

图1 雷达采样系统总体结构Fig.1 Overall structure of radar sampling system

2 系统硬件实现及主要电路设计

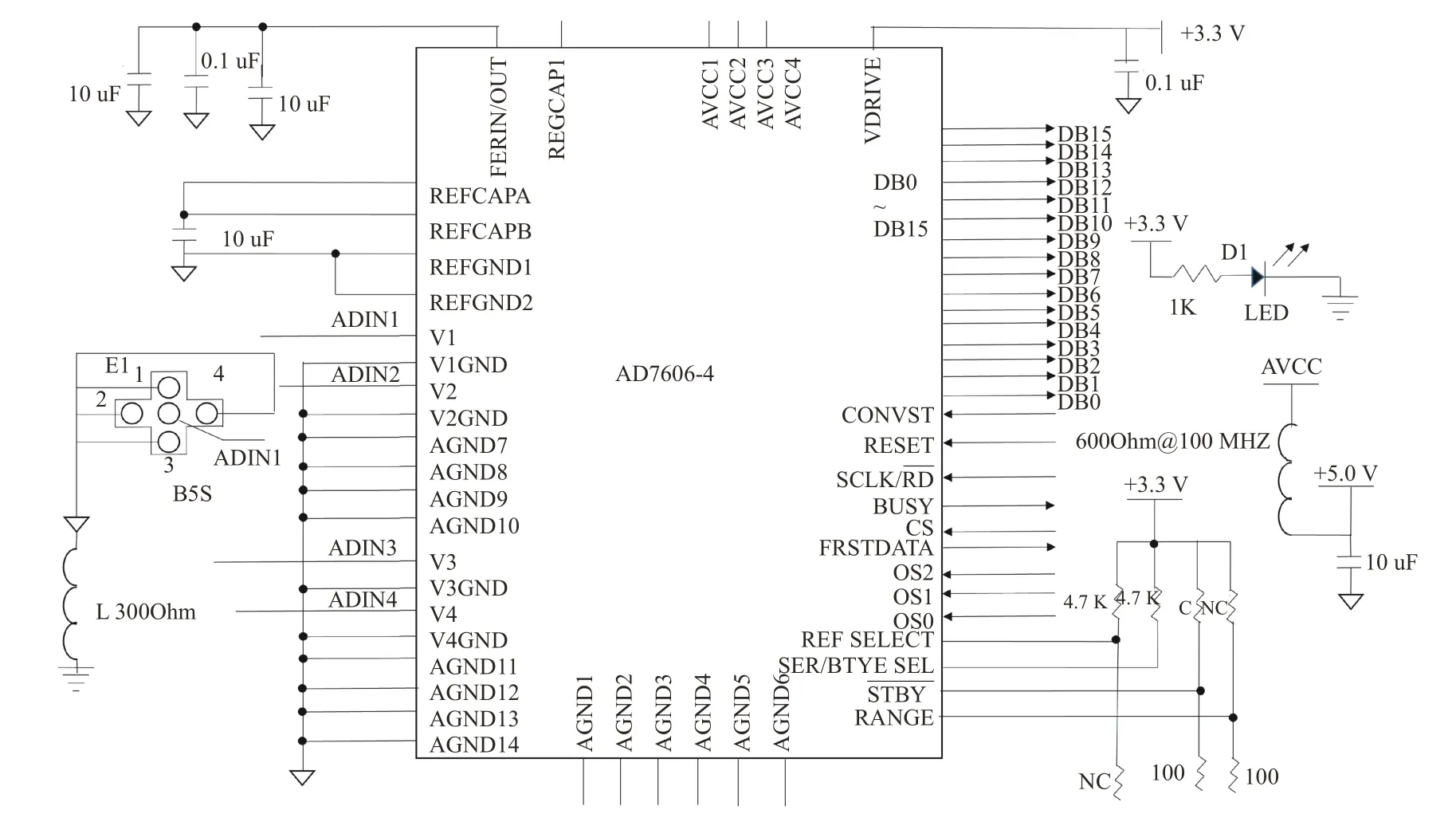

2.1 数据采集电路

AD数模转换器是整个系统的核心器件,它影响着整个系统的采样精度、吞吐率,所以AD转换芯片的选型至关重要。本文选择ADI公司的7606系列芯片AD7606-4[10],其片内集成了输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、数字滤波器、2.5 V基准电压源以及高速串行并行接口。所有通道每秒均以高达200 000样本的吞吐速率采样。输入钳位保护电路可以耐受最高±16.5 V的电压。

AD采样部分电路图如图2所示。

图2 AD采样电路Fig.2 AD sampling circuit

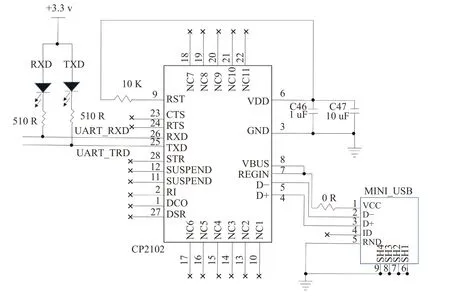

2.2 串口收发电路

数据采集完成之后,需要发送到PC端进行数据显示,本系统选用串口通信的方式,串口收发部分电路如图3所示。

图3 串口收发电路Fig.3 Serial port transceiver circuit

使用USB转串口的方式,优点在于不涉及到电气协议标准,硬件连接简单。FPGA两个可以自由定义的I/O口与发送引脚UART_TXD和UART_RXD相连,两路信号各接一个LED灯可显示此时是否有数据正在传输。CP2102 是一个专用的USB转串口芯片,CP2102与其他USB-UART转接电路的工作原理类似,通过驱动程序将PC的USB口虚拟成COM口以达到扩展的目的。

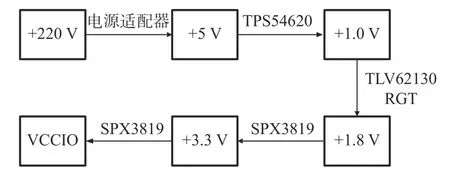

2.3 电源电路

由于系统外设以及FPGA各个Bank工作电压不一致,故需要低压差线性稳压器(LDO)与DC-DC芯片提供不同的工作电压[11-12],对于本系统而言,需要+1.0 V、+1.8 V、+3.3 V电压,系统供电电源为+5 V。图4是电源上电顺序图,LDO要求输入输出的电压不可相差太大,但LDO稳压芯片稳定性相对较好,负载的响应更快,电压输出纹波较小,对于电源的干扰很小,故本系统选用SPX3819M5-3-3芯片实现由+5 V到+3.3 V的电压转换。而从+5 V到+1.0 V、+1.8 V的压降选用直流电压到直流电压(DC-DC)的转换芯片来实现。相对LDO芯片而言,DC-DC芯片的优点是转换效率高,输入电压范围更宽,缺点是响应不如LDO芯片,输出纹波较大。对于压降较大的输出电压而言,有略微的波动不会影响整个模块的工作。

图4 电源上电顺序图Fig.4 Power on sequence

3 系统仿真

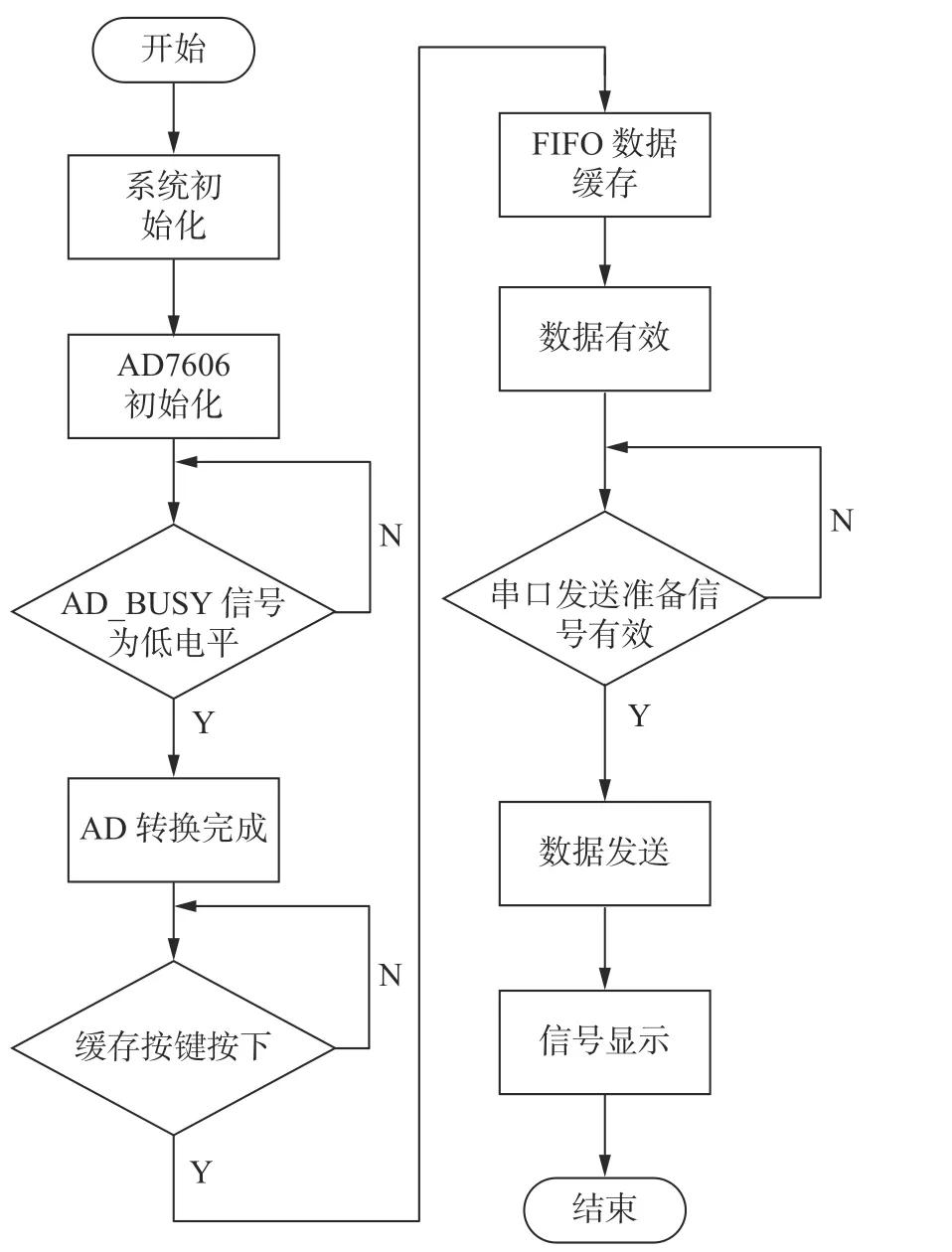

3.1 系统控制软件

系统软件流程如图5所示。

图5 系统软件流程图Fig.5 Flow chart of system software

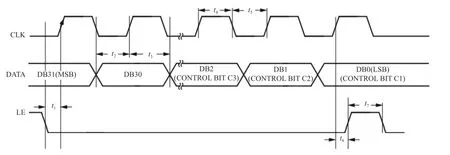

3.2 雷达前端驱动模块

雷达信号的产生主要由ADF4158芯片和BGT24MTR12芯片起着关键的作用。以FPGA作为控制器,选择SPI通信协议模式给ADF4158以及BGT24MTR12内部各个寄存器赋值,使芯片工作。SPI(串行外设接口)是一种高速、全双工同步的通信总线,其在FPGA的芯片引脚上仅占据4根线(由于本系统只有数据的单向传输,故使用三线制SPI模式),使通信变得更简单、高效。

ADF4158时序图如图6所示。

图6 ADF4158时序图Fig.6 ADF4158 sequence

FPGA通过I/O口[13]赋予ADF4158时钟、数据以及使能端信号,在时钟上升沿发送数据,下降沿接受数据。FPGA内部有8个寄存器,分别寄存外部电压控制振荡器(VCO)的输出频率、调制信号波形、调频步长以及调制周期等[14]。按照Datasheet里的寄存器赋值顺序,在每赋值一个32位寄存器之前将使能端设为低电平,赋值结束后将使能端设为高电平,目标调制信号周期为8 ms,调制信号频率带宽为200 MHz。

对于BGT24MTR12,同样采用三线制SPI模式。其时序图与ADF4158相似,为了节约前端雷达板间I/O引脚,并优化前端雷达印制电路板的布局,ADF4158与BGT24MTR12共用一个时钟端以及数据输入端,通过芯片的使能端来控制数据的写入。

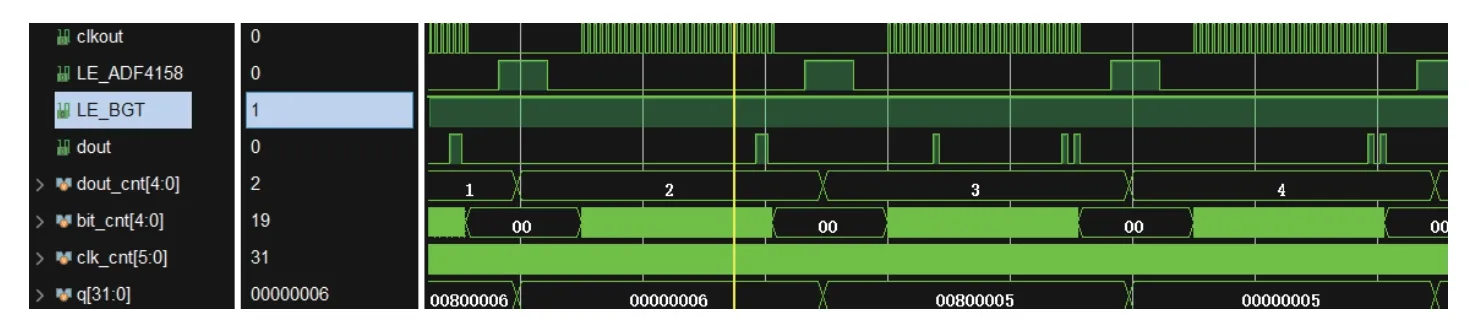

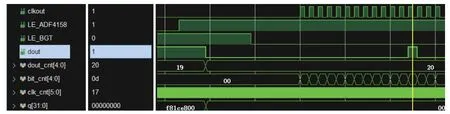

ADF4158芯片数据传输过程仿真如图7所示。

图7 ADF4158数据传输Fig.7 ADF4158 data transmission

图7 仿真结果显示了第2到第4个数据的传输过程,每一个时钟周期传递1 bit数据,待一个完整数据传输完成,拉高使能端。在下次数据传输之前再将使能端置为低电平,并且BGT24MTR12使能端全程置为高电平。从仿真结果可知,软件完全符合流程图设计。

BGT24MTR12芯片数据输出过程仿真如图8所示。

图8 BGT24MTR12数据传输Fig.8 BGT24MTR12 data transmission

从图8仿真图可以看出,前20个ADF4158数据完成传输后,ADF4158使能端置为高电平,BGT24MTR12使能端置为低电平,完成16 bit数据传输,仿真结果符合设计要求。

3.3 AD采样模块

FPGA对AD7606[15-16]的控制主要是通过对转换信号CONVSTAB、片选信号CS、时钟信号SCLK赋值来实现,对于本系统,采样率设置为20 kHz。仿真如图9所示。

图9 AD7606采样Fig.9 AD7606 sampling

当CONVST AB由低电平再变为高电平时,上升沿启动所有模拟输入通道的采样。当Busy信号为低电平时(仿真时默认Busy信号始终为低电平,现实中是来自于AD7606内部的Busy信号反馈)表示模拟信号转换完成且可以读取。此时将CS,RD信号设为低电平,完成数据读入到相应的寄存器中。

3.4 数据发送模块

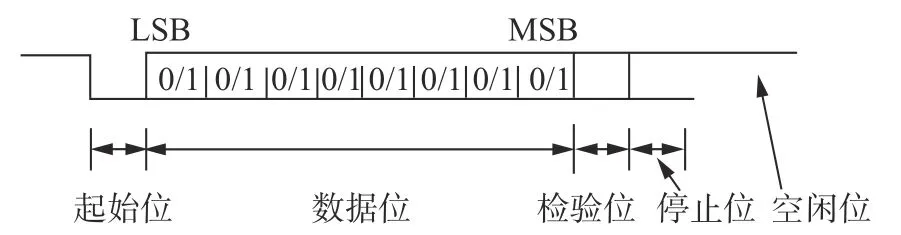

本系统选用UART串口发送模式给PC端发送数据,串口波特率为119 200 bit/s,异步串口通信协议时序[17]如图10所示。

图10 串口数据构成Fig.10 Composition of serial port data

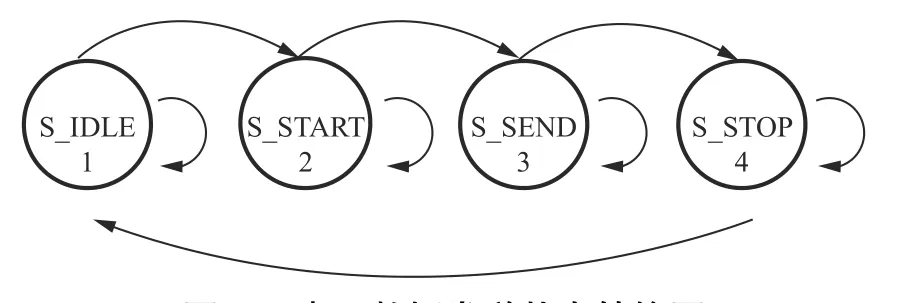

每一次传输从一个低位起始位开始,一次发送8个数据,由于本系统传输不需要使用奇偶位,故当第8 bit传输完成后就设为高电平。从波形可以看出起始位是低电平,停止位、空闲位都是高电平,利用此特点可以认为一个下降沿事件发生时开始一次数据的传输。该部分选用状态机实现,状态机转换图[18]如图11所示。

图11 串口数据发送状态转换图F ig. 11 State transition diagram of serial port data transmission

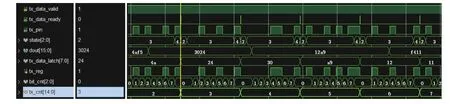

串口数据发送仿真图如图12所示。

图12 串口发送仿真Fig.12 Simulation of serial port sending

由于串口一次性发送8位数据,而前端AD7606读出的数据是16 bit,需要在发送之前做一次数据拆分,待数据传输给PC端后,再做数据的合并,从而满足数据传输的要求。当valid和ready信号同时为高电平时,tx_reg信号设为低电平,开始一次数据传输,8 bit数据传输完毕,将tx_reg信号设为高电平完成一次传输,tx_cnt对数据依次计数。由图12可看出,数据依次发送,无数据丢失现象,满足FPGA与 PC端通信要求。

4 测试结果分析

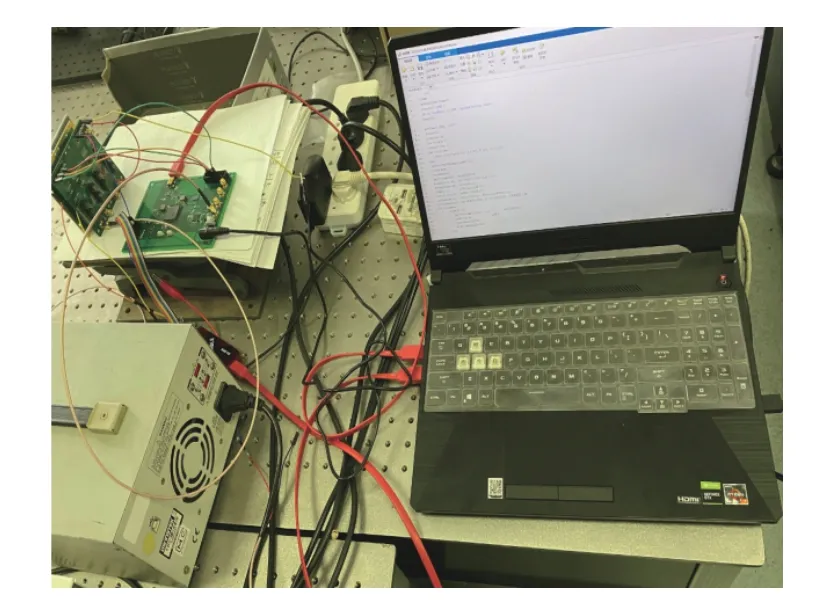

FPGA采集系统实物及测试平台如图13、图14所示。

图13 采集系统实物图Fig.13 Photo of the acquisition system

图14 测试平台Fig.14 Test platform

雷达前端采集系统主要实现数据的正常采集,并将有效信号交与后端系统进行数据处理。本文系统功能验证是通过建立MATLAB GUI界面来完成。

数据采样设置如下:采样频率20 kHz、采样点数1 024、采样周期8 ms。

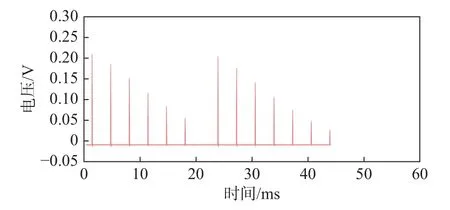

斜坡完成信号用于后端区分调频连续波的上频段和下频段,这样可以保证后端测速测距的精度更高。斜坡完成信号如图15所示。

图15 斜坡完成信号Fig.15 Slope completion signal

可以观察到每4 ms就会有一个脉冲信号产生,前端斜坡使能完成,信号采样正确。

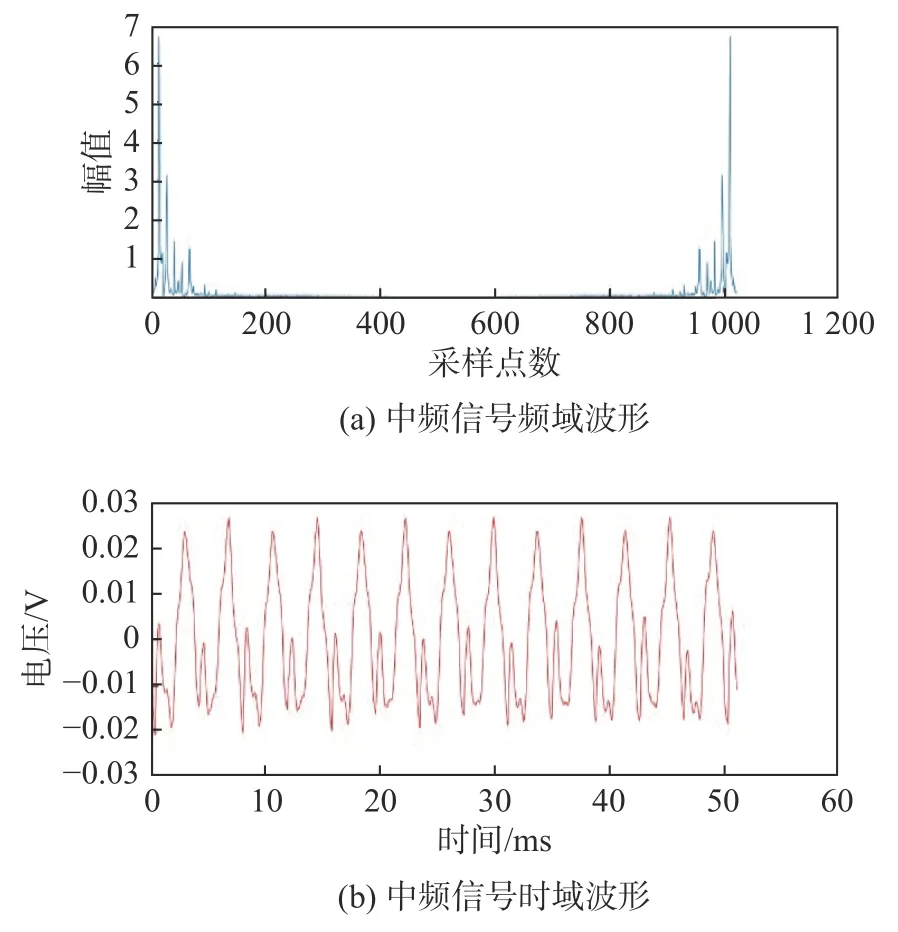

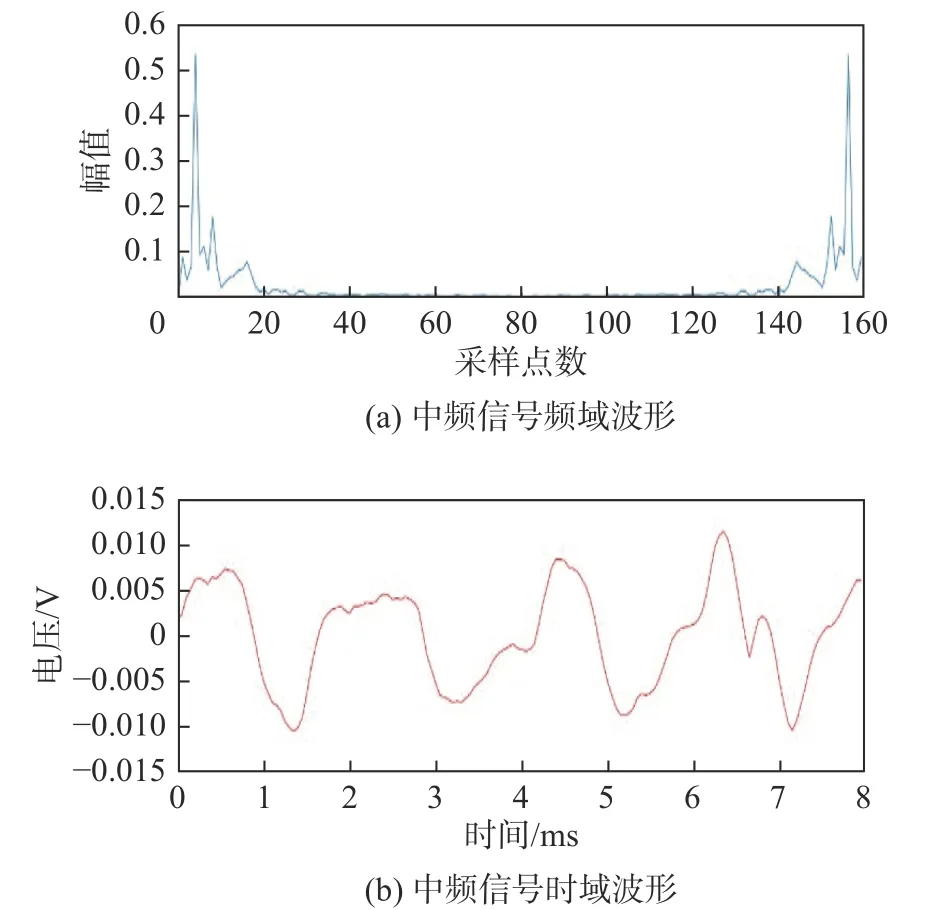

中频信号携带的频率信息用于后端对其进行解析,得到速度、距离等有用信息。多周期中频信号与单周期中频信号分别如图16、图17所示。雷达调制信号如图18所示,用于调制中频信号周期和作为中频信号采集的触发信号。

图16 多周期中频信号Fig.16 Multi-period IF-signal

图17 单周期中频信号Fig.17 Single period IF-signal

图18 调制信号Fig.18 Modulation signal

5 结 论

本文设计了基于FPGA的雷达信号采集系统。主要介绍了系统主要电路,并对系统每一部分做功能仿真,最后搭建实验测试平台,将前端调制信号、中频信号等接入雷达采集系统,上位机显示数据能在指定采样频率下完整采集。分析结果表明,本文设计的雷达系统具有采样精确、采样效率高、体积小、便于携带等特点,具有一定的实际使用价值。