磁选态铯原子钟弱信号直接采样方法研究

高天翔,王骥,赵玉龙,董鹏玲,黄良育,刘志栋

兰州空间技术物理研究所 真空技术与物理重点实验室,兰州 730000

1 引言

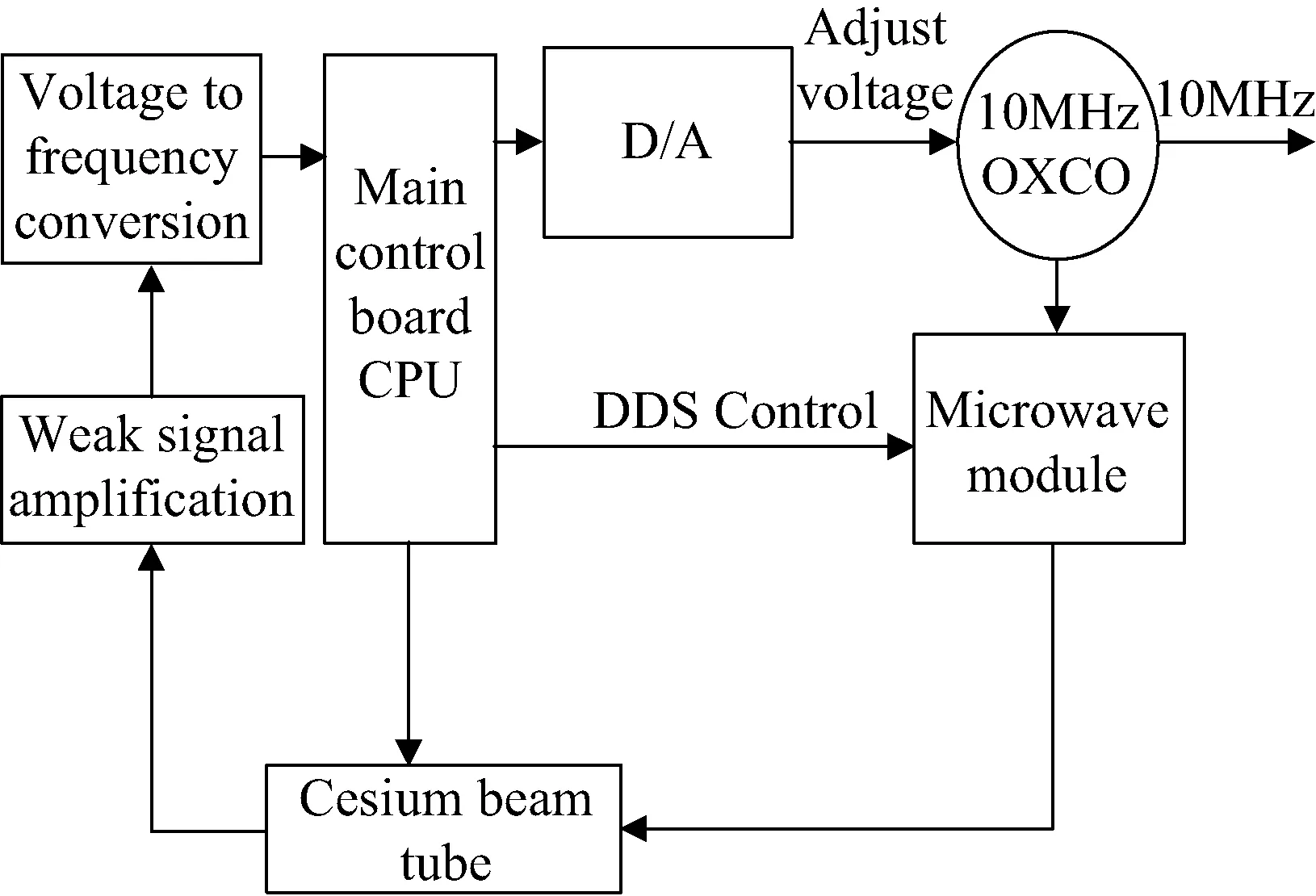

磁选态铯原子钟以其优良的长期稳定性和高可靠性特点,无论在地面导航、守时还是在星载应用领域都发挥着重要作用[1-2]。磁选态铯原子钟主伺服控制电路如图1所示,是一个嵌入式伺服控制系统。该电路控制微波模块产生经过调制的微波信号激励铯原子跃迁,铯束管输出的带有跃迁信息的弱电流信号经过采样,通过CPU计算出压控晶振的调节电压,再通过数据总线控制数模转换器,从而对压控晶振的输出频率进行调整,控制压控晶振输出,完成环路锁定[3-5]。在以5071A铯原子钟为代表的“CSⅡ”技术中,弱信号采样方法为使用AD652芯片作为压频转换器件的压频转换法;2000年以后,以Cs4310B和Cs4000铯原子钟为代表的“CSⅢ”技术采用的是16位A/D直接采样铯束管弱信号[6]。压频转换法是一种间接型模数转换方法,勉强达到12位分辨率时所需采样时间为20 ms,A/D直接采样法理论上不仅能够保证采样精度,还能提高采样速率,实现高稳定度和低相噪指标。因此,比较上述两种方法对磁选态铯原子钟技术指标究竟有何影响就显得十分重要;同时,由于压频转换法所需芯片无法实现全部国产,研究铯束管弱信号A/D直接采样优化主伺服控制电路将对提高铯原子钟性能指标,并实现完全国产化奠定一定基础。针对此问题,本文设计了以DSP28335芯片为CPU,利用CAN总线通信技术和主控CPU板进行通信的A/D直接采样电路,来完成对于弱信号的高精度快速采样、处理,计算压控晶振的调节电压,控制其输出频率以实现目的。

图1 磁选态铯原子钟主伺服控制电路原理框图Fig.1 The main servo control circuit principle diagram of the magnetically selected cesium atomic clock

2 弱信号采样方式对比

2.1 压频转换法

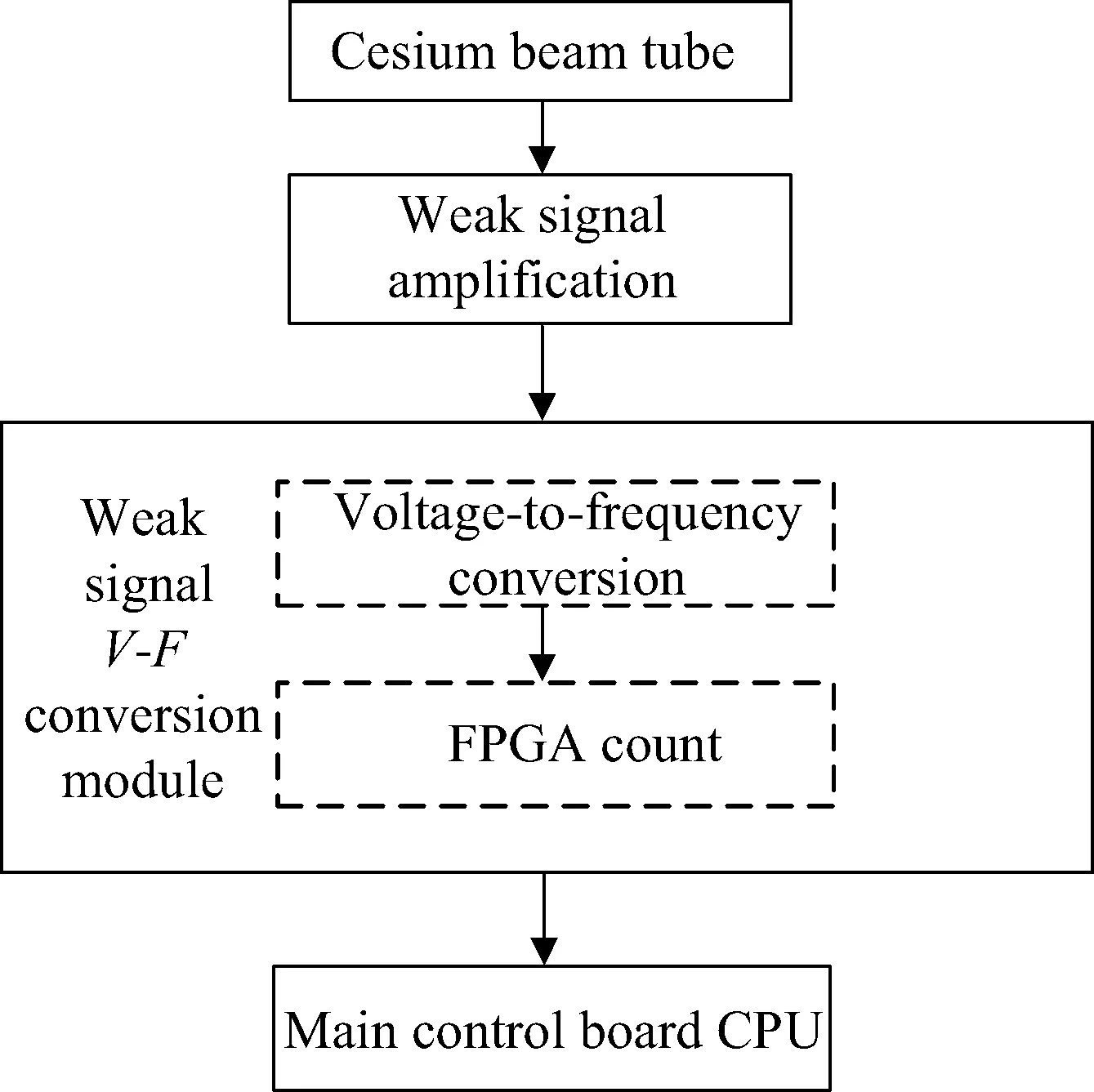

磁选态铯原子钟产品利用AD652转换芯片对铯束管输出弱信号采样的压频转换法,其原理框图如图2所示。弱信号压频转换模块的输入为铯束管输出电流经过电流-电压转换后的弱电压信号,然后通过转换将电压信号转换成脉冲频率信号,再将频率信号输出给FPGA模块,FPGA模块通过对脉冲频率计数,获得铯束管输出电流,FPGA将电流信号上报给主控板CPU进行计算处理。压频转换是一种间接比较型的A/D采样法,即输入模拟量与参考电压不直接进行比较,而是转换成频率这个中间变量进行比较,然后对结果进行数字编码。该方法的A/D分辨率是由时钟频率和转换时间(门控时间)决定的,其转换时间TC为:

图2 压频转换原理框图Fig.2 Block diagram of voltage-frequency conversion principle

式中:FFS为AD652的满度频率;N为给定分辨率的数字量;fCL为时钟频率。在现有磁选态铯原子钟时钟频率500 kHz输出频率250 kHz的情况下,构成12位ADC,所需转换时间为:

另外加之铯束管响应时间3 ms以及放大电路响应时间4 ms,则压频转换总采样时间为它们的和23.4 ms,即23.4 ms内只采集了一个数,采样速度慢。在本文设计的A/D直接采样电路中,调制点信号采样时间为20 ms,因此实际转换时达不到12位分辨率,这会导致铯原子钟的调制点信号误差无法控制到1 mV以下,影响铯原子钟短期稳定度。

2.2 A/D直接采样法

铯束管输出信号为100 nA左右,经过电流-电压转换后达到1 V,再经前量放大达到2.5 V以上,因此可以采用模数转换芯片直接采集。本文采用了A/D直接采样法,即利用DSP28335做为CPU和A/D采样模块,铯束管输出的弱信号经放大后,DSP28335对该信号进行采样并处理,然后利用CAN通信技术和主控CPU板进行通信,进而对压控晶振模块输出频率进行调整完成闭环锁定,其原理框图如图3所示。集成在DSP28335中的A/D模块的核心资源是具有12位分辨率的模数转换器,同时具有2个采样保持器,通过多路复用后有16个模拟转换输入通道,这16个模拟转换输入通道复用2个采样保持器保证了ADC模块能够同时采样2个输入通道[7]。其最高时钟频率可配置为25 MHz,可由多个触发源启动ADC,又允许每个或者每隔一个序列转换结束产生中断请求[8-9],因此该方法较压频转换法大大提升了采集速率。通过CPU

图3 A/D直接采样原理框图Fig.3 Block diagram of A/D direct sampling principle

内的软件设计,可以实现20 ms完成1 200次数据采样,由于采样点数多,可以通过求平均值的方法获得调制点信号值,还可以数字滤波排除掉异常干扰。

3 弱信号A/D直接采样方案硬件设计

系统硬件整体设计原理如图4所示。该系统基于DSP芯片TMS320F28335为控制核心,由数据采集模块、CAN总线通信模块和供电电源模块组成。铯束管输出的含有频率偏差信息的信号经滤波、放大转化为电压信号送入DSP的A/D引脚,DSP接收该信号后经过处理运算通过CAN总线通信模块上报到主控板CPU的I/O端口,再进行频率调整量计算,完成环路锁定。电源模块为采样CPU及CAN总线通信模块提供所需的供电。

图4 系统整体硬件设计原理框图Fig.4 Block diagram of the overall hardware design of the system

3.1 处理器选型

磁选态铯原子钟弱信号采样系统需要对数据进行精准采集和计算,这要求处理器拥有较高的数据运算精度和速度;同时采样系统需要外接数据采集、通信模块等外设,这对处理器的接口也有较高要求。

采样电路采用的系统CPU是DSP28335芯片,这是一款主频150 MHz的32位数字信号处理器,具有浮点处理能力外兼功耗小、成本低、外设集成度高等优点。该芯片拥有16通道的12位模数转换模块以及2个eCAN通信模块,能够完成复杂的数据处理[10-11],A/D模块在3 V内分辨率为12位,优于1 mv,同时带浮点处理器实现平均和滤波功能时间小于1 ms,满足系统的采样需求。

3.2 通信模块

为了保证弱信号采样系统数据来源的实时性与准确性,在磁选态铯原子钟采样系统DSP与主控板CPU间采用CAN总线通信方式传输监测数据。DSP28335芯片内部集成了完整的CAN总线通信控制器。该控制器可以完成数据传送时的自动回复、自动重发、错误诊断,并具有可编程的中断配置、总线唤醒等功能。其支持CAN2.0B协议,提供29位标志符、几个控制位和32个具有8字节数据的消息邮箱,是一个32位的外设模块[12]。虽然DSP的内部具有CAN总线通信控制器,但生成的数据不符合标准的CAN总线通信协议,必须要通过驱动芯片驱动CAN总线转发器才能正常通信。CAN总线通信接口连接设计如图5所示。CAN总线通信驱动器采用了SN65HVD230芯片,为消除信号反射必需要在总线高低两端添加120 Ω的电阻。

图5 CAN总线通信连接Fig.5 CAN communication connection diagram

4 弱信号A/D直接采样方案软件设计

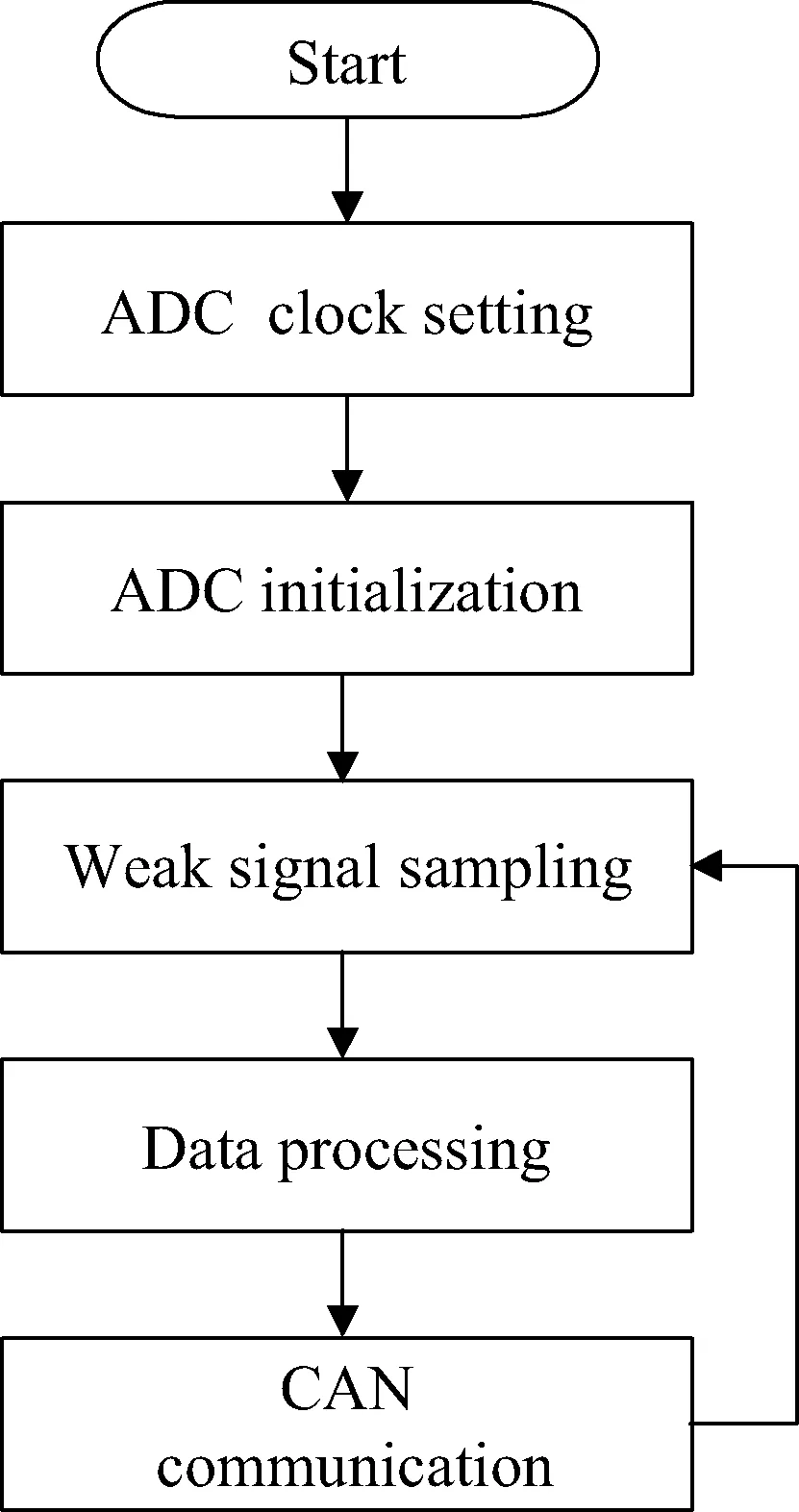

磁选态铯原子钟弱信号采样系统软件以CCS7.4软件作为开发环境。软件部分主要由数据采样及处理、CAN总线通信组成。图6为弱信号采样程序流程。

图6 弱信号采样程序流程Fig.6 Flow chart of weak signal sampling program

A/D转换模块将模拟量转换为数字量通常要经过4个步骤:采样、保持、量化和编码[9-11]。铯束管产生弱信号,然后将这些信号送入A/D采集模块进行模数转换。ADC采样软件设计主要有3部分:ADC工作时钟设置、ADC初始化设置,ADC工作方式设置。ADC工作前必须要进行时钟即工作频率的设置,再对ADC进行初始化,然后设置其工作方式、采样顺序、采样模式等。采样一个周期后通过求平均值的方法获得调制点信号,并加入数字滤波。

由于伺服系统是双DSP的控制模式,需要对传输数据的CAN总线通信模块进行软件配置,主要分为3个部分:初始化模块、邮箱配置模块和发送模块。CAN总线模块初始化过程是为了设置位时间寄存器,以确定调制点信号通信波特率、状态寄存器以及复位邮箱控制寄存器,在使用CAN总线通信模块之前必须进行初始化操作。邮箱配置模块主要是设定邮箱标志,邮箱发送或者接收以及是否产生中断等。CAN总线发送模块的设置只需要将经过采样处理后的弱信号数据写入邮箱,然后置位相对应的CANTRS位,如果采样数据成功发送,邮箱的CANTA相应位就会置为1[12]。

5 试验结果与分析

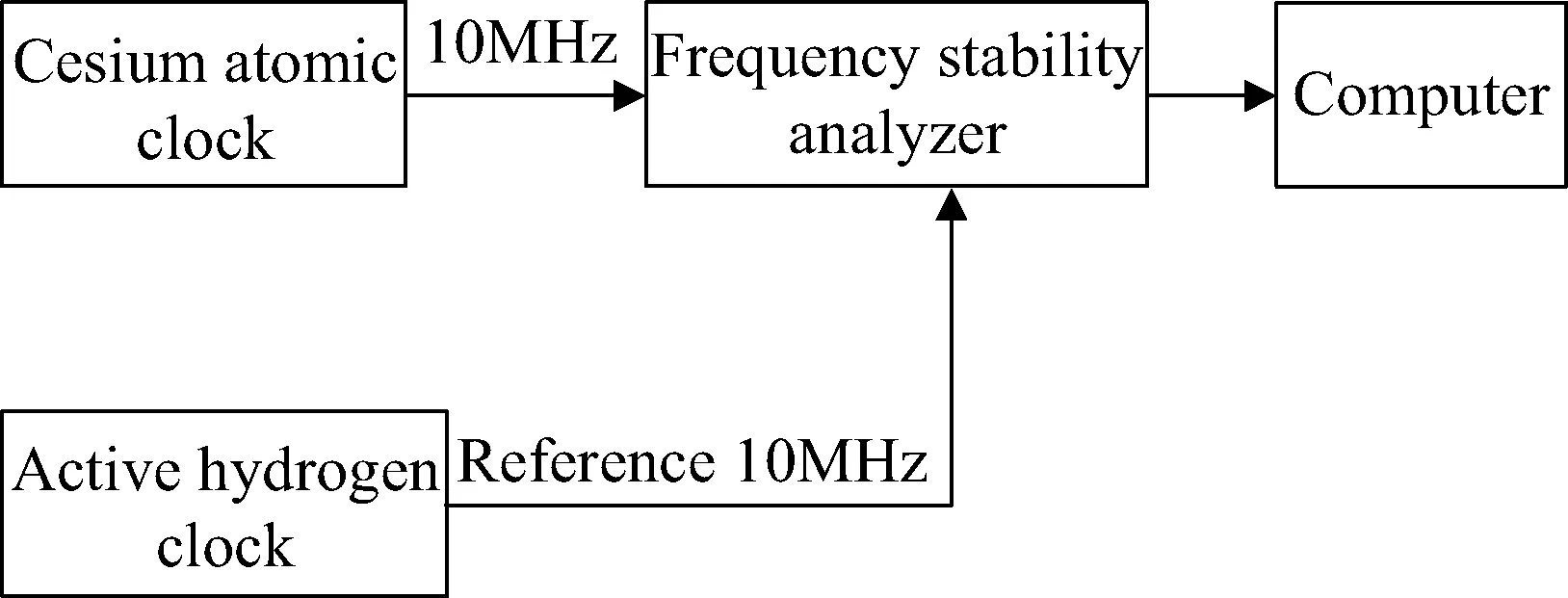

5.1 测试方案系统

测试系统原理如图7所示。磁选态铯原子钟输出10 MHz频率信号进入频稳分析仪,通过和参考钟(主动氢钟)输出的10 MHz参考频率信号进行对比,对磁选态铯原子钟的频率准确度、频率稳定度等进行测试。频率稳定度测试采用了VCH-314频率稳定度测试仪,参考钟采用了iMaser3000氢钟[13-15]。

图7 测试系统原理框图Fig.7 Block diagram of the test system

5.2 相对频率偏差对比

相对频率偏差是磁选态铯原子钟的重要指标,它是指在实际系统中,磁选态铯原子钟输出频率与参考(氢原子钟)输出频率相对差值。图8是压频转换法测得1 s采样相对频率偏差结果,可以看出偏差在-2.0×10-11~2.0×10-11,图9是采用基于DSP28335的A/D直接采样测得相对频率偏差结果,可以看出偏差在-0.7×10-11~0.7×10-11。由图9和图10结果对比可以得出,采用弱信号A/D直接采样电路可以明显降低磁选态铯原子钟相对频率偏差的偏差范围,意味着磁选态铯原子钟频率波动性小,1 s稳定度会有所改善。

图8 采用压频转换法的相对频率偏差Fig.8 Relative frequency deviation using voltage-frequency conversion method

图9 采用A/D直接采样法的相对频率偏差Fig.9 Relative frequency deviation using A/D direct sampling method

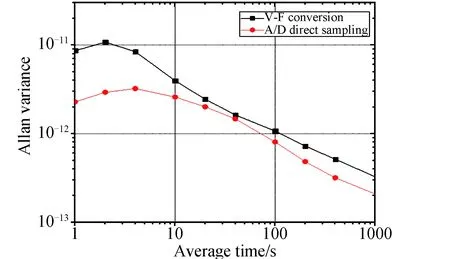

5.3 频率稳定度对比

两种采样方法获得的磁选态铯原子钟频率稳定度测试曲线如图10所示。采用A/D直接采样测得的1 s的频率稳定度为2.29×10-12,10 s的频率稳定度为2.59×10-12。采用压频转换测得的秒稳为8.64×10-12,10 s稳为3.96×10-12。试验结果表明,在磁选态铯原子钟长期频率稳定度主要由其物理部分决定的情况下[16],采用的基于DSP28335的A/D直接采样法对磁选态铯原子钟1~1 000 s内的短期频率稳定度较压频转换法有所改善,尤其是秒稳有着显著提升。

图10 两种采样法的频率稳定度结果对比Fig.10 Comparison of frequency stability results of the two sampling methods

6 结论

本文利用DSP28335芯片设计了一种对于磁选态铯原子钟弱信号的A/D直接采样电路,通过试验对比了该方法和现有压频转换法对于被测磁选态铯原子钟相对频率偏差和频率稳定度的影响。试验结果表明,本文所设计的基于DSP28335芯片的A/D直接采样电路对弱信号进行采样、上报、处理的速度更快,准确度更高;同时由于铯束管输出的弱信号波动幅值较大,采用A/D直接采样多次平均后取得了良好的效果,最终有效减小了磁选态铯原子钟的相对频率偏差范围,提升了短期频率稳定度指标,并为实现磁选态铯原子钟完全国产化奠定了一定基础。