微波基板表面可焊性镀层的制备及性能评估*

张 眯,王从香,王越飞,侯清健

(南京电子技术研究所,江苏南京210039)

引 言

随着电子信息技术的迅猛发展及军用电子装备技战术指标的不断提高,电子整机系统正逐渐朝着小型化、轻量化、多功能、高密度与高性能化的趋势不断发展,对封装基板的布线密度、散热能力、电传输性能、元器件集成密度及长期可靠性等提出了迫切的需求。低温共烧陶瓷(Low Temperature Co-fired Ceramic,LTCC)技术通过陶瓷生料与导体浆料多层共烧的方式实现了高密度三维电路网络无源组件的制备,利用腔内埋置或表面贴装的方法集成多种元器件,形成多功能化的无源/有源集成的功能模块或电路,有效提高封装密度并缩短芯片导体的互联长度[1],极大地降低了工艺复杂性与成本,提高了组件的电性能及可靠性,广泛应用于高密度集成模块、大功率模块和微波/毫米波电子模块和整机中[1–3]。

为了进一步降低共烧陶瓷微波基板的制作成本,提高基板散热能力及布线密度,全银浆料体系LTCC基板和高散热氮化铝高温共烧陶瓷(High Temperature Co-fired Ceramic, HTCC)基板得到了越来越广泛的关注与研究[3–4]。HTCC烧结所用的钨和钼属于难熔金属浆料,在低成本LTCC全银导体浆料表面无法直接键合和钎焊,为了实现基板表面高密度元器件及模块的有效装配并提升导体导电能力及可靠性,已烧结基板需要进一步采用化学镀或电镀工艺在金属浆料表面增加镍、金等导体膜层[4–6]。采用电镀工艺在基板表面沉积膜层时,基板表面待镀区域必须具有电导通性,但对于表面布线复杂和孤岛较多的微波基板,若采用电镀的方法进行表面膜层沉积,则必须在布线时增加电导通工艺线,这将具有很大的局限性。与电镀相比,化学镀对待镀样件的电导通性无要求,待镀区域无需电互联,有效提高了布线空间的利用率,有利于获得高密度和小型化的封装基板。特别是对于包含高密度孤立焊盘和高密度布线的基板,在表面的可焊性镀层制备过程中,化学镀具有独特的优势。

本文介绍了采用化学镀工艺在LTCC微波多层基板表面制备可焊性镀层的工艺过程,讨论了镀层制备的要点和影响化学镀的主要因素及其作用机理,采取了适当的措施,解决了镀层漏镀和渗镀的难题。文中在LTCC微波多层基板表面完成Ni(镍)/Pd(钯)/Au(金)可焊性镀层的制备,并对可焊性镀层的形貌、附着力、键合强度等进行测试评价,结果均满足基板组装应用要求,为全银体系微波多层基板在微波功率组件中的工程化应用奠定了基础。

1 化学镀过程及原理

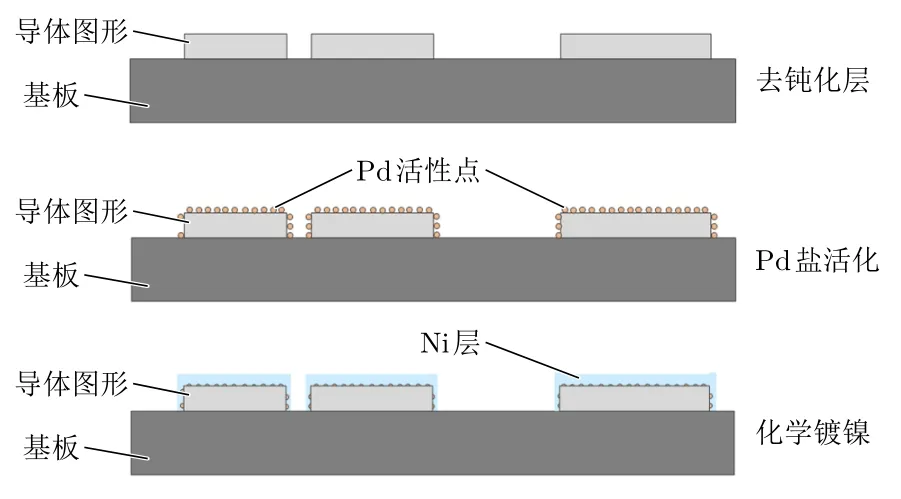

化学镀是指在溶液中利用化学反应或电化学反应在基体材料表面沉积成膜的一种技术。化学镀过程中,金属离子在溶液中通过自催化过程(或被还原剂还原)向固/液两相界面上析出,在基底材料表面沉积形成镀层。化学镀镍只能在表面负电位的镍、铁、钴、钯和铝上直接沉积,在铜及其他金属上化学镀镍时,必须与比镍更活泼的金属或钯接触[7]。通常情况下,采用钯盐活化的方法在金属表面沉积一层胶体钯,形成自催化活性中心,在后期化学镀覆过程中,溶液中的金属离子在自催化活性中心位置不断沉积,化学镀过程示意图见图1。

图1 化学镀过程示意图

2 微波多层基板化学镀工艺难点

微波多层陶瓷基板表面布线密度很高,表面图形线宽/间距窄,孤立焊盘尺寸小,深腔多且结构复杂。与铝硅碳等需要整体镀覆的电子封装材料相比,微波多层陶瓷基板表面更易出现局部图形漏镀、渗镀、表面粗糙长瘤等现象[8],因此化学镀工艺难度更大。通常情况下,漏镀、渗镀等失效问题主要集中在窄间距图形处、小尺寸孤立焊盘处或深腔底部,如图2所示。

LTCC微波多层陶瓷基板通常包含多个深腔结构。深腔底部溶液扩散交换能力弱,易造成:1)钯活化后,腔底的残留溶液难以彻底冲洗干净,主盐离子易在此处还原沉积,造成渗镀问题;2)钯活化过程中,活化液在腔底的扩散能力弱,腔底图形钯活化不足,进而出现漏镀现象。除窄线宽/间距图形和深腔底部外,许多孤立线、点等小尺寸焊盘也容易在化学镀镍过程中发生漏镀。当焊盘尺寸变小后,钯离子在焊盘上的置换速率降低,相同时间内钯在小尺寸焊盘上的覆盖率减小,达不到引发化学镀镍所需要的覆盖率(约12%)[8]。综上所述,如何获得附着力良好,无漏镀、渗镀等质量缺陷的可焊性镀层是微波多层基板化学镀的关键。

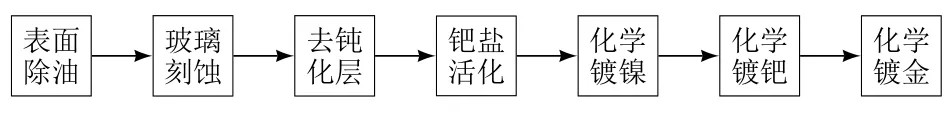

LTCC微波多层基板表面化学镀镍钯金的工艺流程如图3所示。

图3 LTCC基板上化学镀镍钯金的工艺流程图

制备Ni/Pd/Au镀层后,采用光学显微镜、扫描电子显微镜(Scanning Electron Microscope, SEM)及能谱仪(Energy Dispersive Spectrometer, EDS)观测分析镀层的微观形貌和表面元素分布情况,利用X射线测厚仪测试镀层厚度,采用3M胶带进行镀层附着力测试,并结合实际生产情况,分析了导致LTCC微波多层基板漏镀和渗镀问题的原因及其作用机理。

2.1 非图形区域渗镀

在某产品的生产过程中发现,经过钯活化后,化学镀镍过程中出现了非图形区域沉积镍的现象即渗镀现象。

一般情况下,渗镀的主要原因是钯盐活化的过程中,催化剂在非图形区域沉积,即非图形区域被活化。此外,非图形区域表面粗糙度过大、镀液活性过强等因素也易导致渗镀。非图形区域渗镀主要与以下几个因素相关:

1)钯盐活化时间偏长、活化液浓度偏高、活化温度偏高,导致非图形区域有较多催化剂沉积。

2)钯盐活化后水洗时间过短、水洗不充分,导致非图形区域上有残留的催化剂[9]。

3)非图形区域处表面粗糙度大、表面能量高且比表面积大,金属离子在此处沉积所需的能量较低且有较多的形核位置。

4)非图形区域表面有其他活性物质,如具有催化活性的C膜、表面Al纳米簇、低价态金属氧化物等,形成“电子富集”环境。后续化学镀的过程中,正价金属离子易在电子富集处得到电子并沉积还原[10]。

5)化学镀镍溶液工作温度过高、主盐离子和还原剂含量偏高、溶液活性过强或溶液搅拌和过滤不足时,也易出现渗镀。

结合实际生产的特点,定位分析可知,基板Ni层渗镀由活化后水洗不足导致。为解决此类问题,在钯盐活化与化学镀镍之间增加一道酸漂洗工序,目的是去除吸附在LTCC陶瓷基板上过量的催化剂。由于LTCC基板瓷体为共价键,瓷体对Pd的亲和力弱于导体银浆料与Pd的亲和力,因此可以借助酸漂洗除去吸附在LTCC瓷体表面的催化中心,同时保证导体银浆料表面有足够的钯自催化中心。增加酸漂洗工序后,该产品化学镀镍后基板表面渗镀问题得到解决。

2.2 图形漏镀

LTCC微波多层基板化学镀时发现,某种基板表面经常出现漏镀问题。引起漏镀问题的主要原因有:1)钯活化不足,图形表面特别是小尺寸图形表面未形成足量的自催化活性中心;2)银层表面被污染或被覆盖,钯催化剂无法在此处沉积;3)活化过程中的“电子传输”效应[9]使得基板电性能连续区域的表面图形出现镍层漏镀。

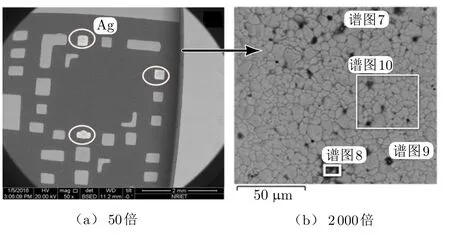

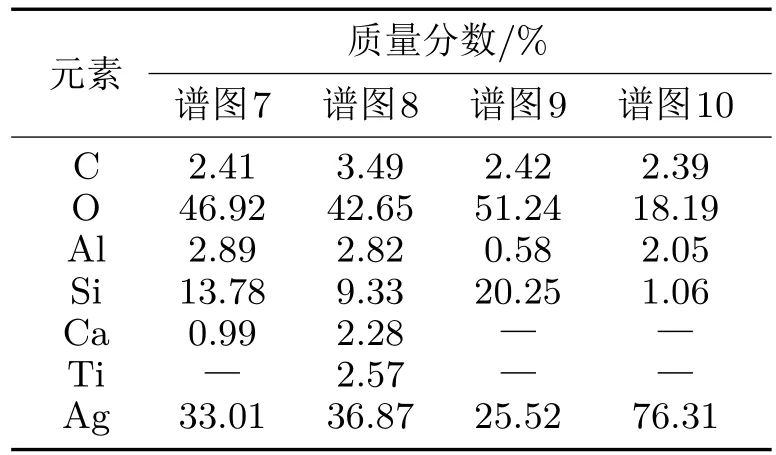

为明确实际生产中某种基板的漏镀原因,对该基板的漏镀区域进行EDS能谱分析,结果见图4。不同位置的元素含量分布见表1。EDS结果表明:除银元素谱峰外,图4(b)中的漏镀区域均探测到含量较高的氧元素及硅元素的谱峰,特别是谱图9位置氧元素的质量分数高达50%、硅元素的质量分数高达20%,还存在少量的钛、钙等元素的谱峰。实验中所用的LTCC瓷体材料为玻璃加陶瓷的复合材料,氧化铝颗粒散布在玻璃基体中,形成玻璃微晶相。玻璃体系主要包括硅硼酸盐、钙硼硅体系等。综上分析,漏镀区域较高比例的硅、氧谱峰为银浆料表面的玻璃相残留。

图4 Ni层漏镀区域样品的表面能谱分析

表1 Ni层漏镀区域图形表面EDS分析结果

此外,漏镀区域的导体图形表面均未探测到Pd元素谱峰。这表明银浆料表面被残留的玻璃相覆盖,导致钯自催化活性点无法在此处正常沉积,因此在后续化学镀过程中出现漏镀缺陷。通过增加玻璃刻蚀时间,可显著改善LTCC图形表面镀层漏镀的现象。化学镀镍后样品的表面形貌如图5所示。镀层表面光滑平整,颗粒大小一致,膜层晶粒细致均匀,无基体裸露,无结瘤,无色差,覆盖完全。利用3M胶带测试复合镀层的附着力,未发现膜层脱落现象,镀层附着强度满足要求。

图5 化学镀镍样品表面形貌

3 镀层性能评估

3.1 锡铅焊盘拉力测试

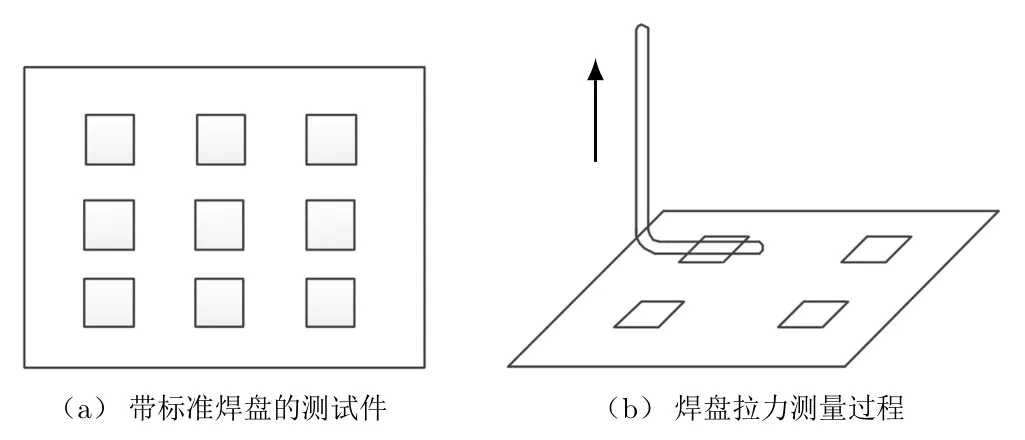

按照GB/T 17473.4—1998 厚膜微电子技术用贵金属浆料测试方法——附着力测定的要求,制备带有2 mm×2 mm标准焊盘的全银LTCC测试件,利用化学镀工艺沉积镍钯金,之后将直径为0.8 mm的镀锡铜丝用烙铁垂直焊接到镀覆后的焊盘上,采用多功能拉力剪切力测试仪测试破坏性拉力,评价镀层及浆料的附着力。测量示意图如图6所示。

图6 焊盘拉力测量示意图

每个样品测量了3个位置的焊盘拉力值,测量数据如表2所示。

表2 镀覆后LTCC基板焊盘拉力强度 N

由表2数据可见,焊盘锡铅焊拉力值均≥39.20 N,金属膜层与基材附着力可靠,满足基板的使用要求。

3.2 键合性能评价

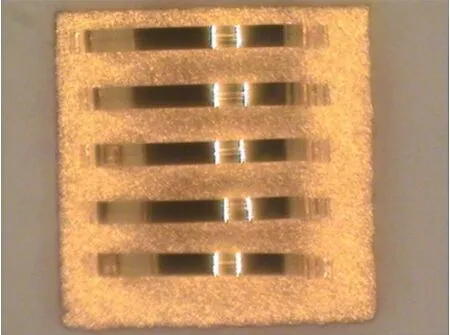

对镀覆完成的LTCC微波多层基板进行打线性能评价。实验中所用的金丝直径为25 µm,实验样品如图7所示。同时开展了金带键合性能评价,所用金带宽度为150µm,金带键合后的样品形貌如图8所示。

图7 金丝键合样品表面形貌

图8 金带键合样品表面形貌

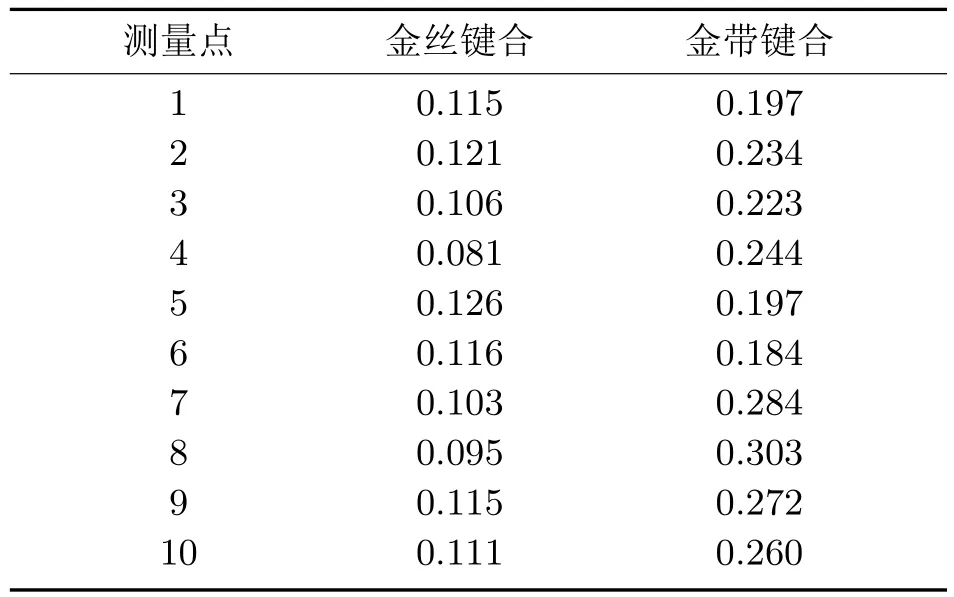

由于金带的尺寸大于金丝的尺寸,键合所需参数以及破坏性拉力值远高于金丝,因此更能反映焊盘的膜层质量。从图8可以看出,金带键合后未发现金属膜层脱膜、鼓起等问题,膜层附着力可靠。键合完成后,按照GJB 548B—2005 微电子器件试验方法和程序,采用多功能拉力剪切力测试仪测试破坏性拉力,评价键合强度。样品金丝、金带键合破坏拉力各测量10个点,测试结果如表3所示。

表3 镀覆后LTCC基板金丝、金带键合强度 N

从表3中数据可以看出,样品金丝键合强度最小值为0.081 N,金带键合强度最小值为0.184 N,镀层的可键合性能良好,键合点可靠,能够很好地满足金丝、金带键合的要求。

4 结束语

本文介绍了采用化学镀工艺在LTCC微波多层基板表面制备可焊性镀层的工艺过程,讨论了镀层制备的要点、影响漏镀和渗镀的主要因素及其作用机理,完成了LTCC微波多层基板表面Ni/Pd/Au镀层的制备,分析了某产品Ni层漏镀的原因,确定银表面的残留玻璃是引起Ni层漏镀的主要原因之一。在Pd活化过程中,自催化活性中心无法在残留玻璃相表面附着,造成了化学镀过程中的漏镀,通过增强玻璃刻蚀条件可有效改善此类问题。制备的Ni/Pd/Au镀层表面光滑平整,晶粒细致均匀,覆盖完全,无结瘤、色差等缺陷。焊盘附着力拉力测试及键合性能评价结果表明:金属浆料及可焊性镀层均附着良好,键合强度较高,键合点可靠,能很好地满足微波组件的应用要求。