基于STM32F107的LTE 小基站从时钟同步系统的实现

姜亚民,贾卫卫,曾 洁,刘立群

(1.大连交通大学电气信息工程学院,辽宁大连 116028;2.大连市共进科技有限公司,辽宁大连 116028)

在4G 时代,小基站主要被应用在宏基站信号覆盖不到的地方,以弥补宏基站的盲区,其应用范围小。然而在如今高频率高宽带的5G 时代,移动数据业务每年呈倍数增长,蜂窝网、无线局域网和移动网络不堪重负。对于蜂窝网而言,小区分裂技术难以满足居民需求,家用小基站成为居民的首选。对于局域网而言,网络的好坏直接影响到员工的工作效率,企业选择安装企业级基站。对于移动网络而言,在一些偏僻地区网络信号差,直接影响到用户上网需求,移动网络运营商选择在公共场所安装室外小基站。小基站的投入使用不仅解决了网络覆盖问题,而且提升了用户上网速率,减少了客户流失量,为运营商赢得了市场份额[1-3]。如果两个通信基站间的时钟同步不能达到要求,就很有可能会出现通信伪连接或者通信中断问题,也会导致通信系统之间在协调、管理和控制方面出现问题,从而严重影响到通信系统的正常运行和服务质量。

目前,国内外技术分别从软硬件方面对时钟系统进行同步,也分别达到了不同程度的精度。硬件方面,卫星定位系统授时同步精度达到纳秒级别;软件方面,NTP 网络时间协议对时可以达到毫秒级,而IEEE 1588v2 协议,又称PTP(Precision Time Protocol,精确时间协议)对软件与硬件方面同时进行完善,同步精度可以达到纳秒级别。该协议采用短帧传输,通信过程简易,计算难度和带宽需求较低,适用于小基站时钟同步[4-6]。

1 IEEE 1588v2协议时间同步原理

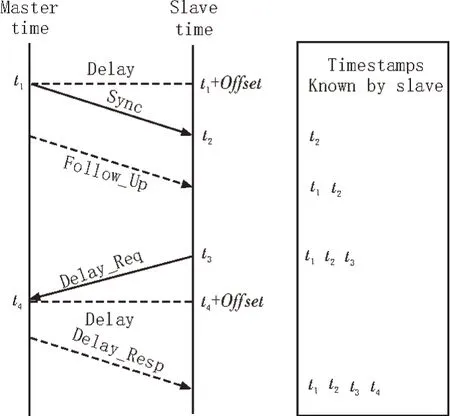

在IEEE 1588v2 协议中,有两种时钟类型,分别为Master time 和Slave time。为确保Master time 和Slave time 同步,分布式系统中的两种类型时钟一直维持通信。主、从时钟通过Sync、Follow_up、Delay_Req 和Delay_Resp 4 种报文来完成时钟的同步[7]。主从时钟之间的通信过程如图1 所示。

图1 IEEE 1588协议同步原理

图1 中Delay 是两时钟之间报文的传输延时,Offset是两时钟之间的时间偏差。系统时钟同步的过程如下[8-9]:

step1:Master Clock 向Slave Clock 周期性地发送Sync 同步报文,此时Master Clock 会记下发送报文的时间t1,随后将t1以时间戳的形式加盖到Follow_Up跟随报文上,并发送给Slave Clock;

step2:当Slave Clock 收 到Master Clock 发 送的Sync 同步报文时,Slave Clock 会记录下此时的时间t2;

step3:当Slave Clock 收 到Master Clock 发 送的Follow_Up 跟随报文时,Slave Clock 会得到t1这个时间戳,隔一定时间Slave Clock 会发送Delay_Req 延时请求报文,并记下此时的时间t3;

step4:当Master Clock 收 到Slave Clock 发送来的Delay_Req 延时请求报文时,Master Clock 记录下此时的时间t4,随后将t4以时间戳的形式加盖到Delay_ Resp 延时请求应答报文,上并发送给Slave Clock;

step5:当Slave Clock 收到Master Clock 发送来的Delay_Resp 延时请求应答报文时,得到t4时间戳,这样Slave Clock 就得到了t1、t2、t3、t44 个时间戳。

根据Master Clock 和Slave Clock 之间报文收发的一个完整过程,可以得到方程:

由以上方程可以计算出两时钟之间的Delay和Offset:

2 从时钟硬件系统

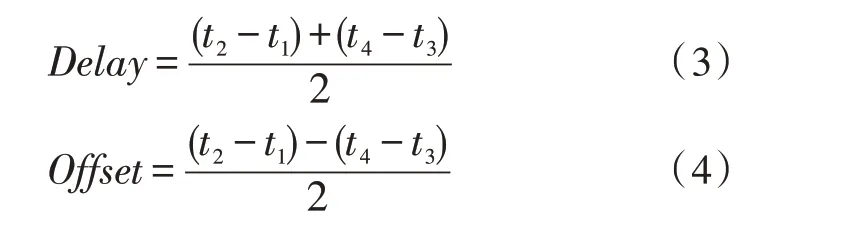

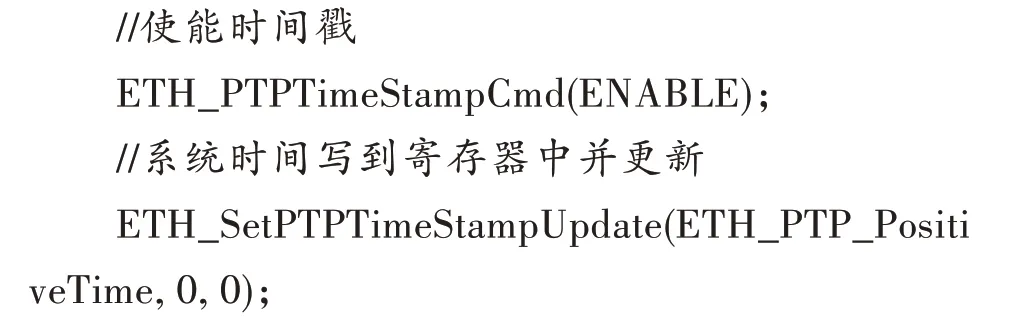

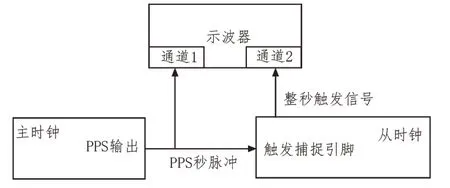

从时钟硬件系统以处理器STM32F107VCT6[10-12]为核心,外接以太网芯片DM9161A,组成了IEEE 1588时钟的硬件平台。STM32F107VCT6 硬件支持PTP时钟同步功能。从时钟系统硬件设计框图如图2所示。

图2 从时钟系统硬件设计框图

硬件系统各模块的功能如下:

媒体选择原则有高效率、低成本原则;教学手段、能力补偿性原则;发挥幼儿主动性、积极性原则。[3]从活动目标、内容、幼儿认知和媒体特点出发,确定媒体最佳作用点。从幼儿不同教学阶段的注意状态出发,确定媒体的最佳作用时机是有意注意与无意注意的相互转换时机。

1)电源模块采用外部直流5 V 供电,但是为了满足开发板外围电路芯片的工作电压为3.3 V,电路通过稳压芯片LM1117-33 降压,该芯片满足3~5 V 之间的供电需求。

2)复位模块采用触摸按钮的方式对系统进行复位操作,当MCU 出现故障时按此按钮为系统提供复位信号。

3)时钟模块包含两种频率(32.768 kHz和25 MHz)的晶体振荡器,其中时钟频率为32.768 kHz的晶振用于驱动独立看门狗或者通过程序选择驱动RTC 实时时钟,时钟频率为25 MHz的石英晶体振荡器为MCU 系统提供可靠的工作时序基准。

4)JTAG 接口与JLINK V8 仿真器配合使用,向开发板中烧录和调试程序。

5)USART 串口电路连接PC 机打印和时间相关的信息。

3 从时钟软件系统

3.1 系统时钟初始化

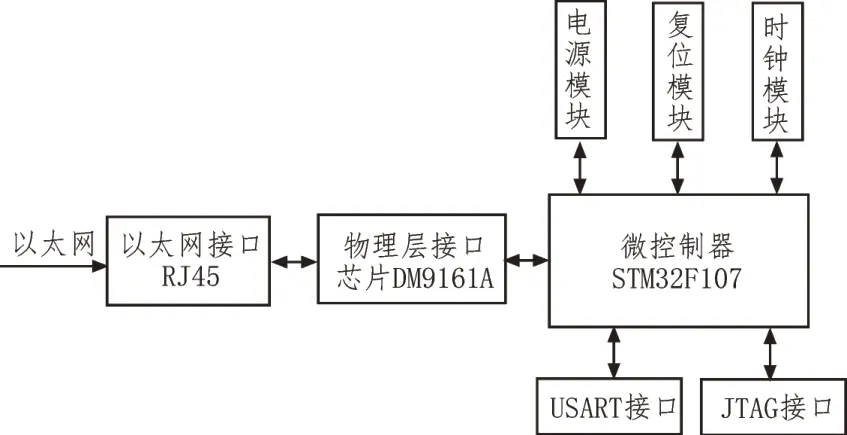

IEEE 1588 协议规定,系统需要64 位的基准时间记录当前时间,分为两个32 位通道,在STM32F107中,ETH_PTPTSHR 和ETH_PTPTSLR 两个寄存器分别保存时间的高32 位和低32 位[13-15]。要在STM32 从时钟系统上运行IEEE 1588 协议,首先需要对系统时钟进行初始化,代码如下:

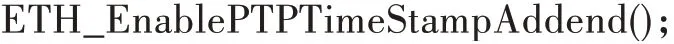

3.2 本地时钟频率调节

本地时钟要想与主时钟实现相对意义上的同步,单靠时间实现特别相近的一个值还远远不够,这时首先就需要进行频率同步。要靠临时速率纠正和固定速率纠正寄存器来调整系统的时钟频率。通过临时速率纠正实现对时钟临时速率的调整,固定速率是在临时速率调整没有实现时才会起作用。本地时钟频率调节程序如下:

3.3 时钟偏差调节

4 时钟同步测试

4.1 同步精度测试方案

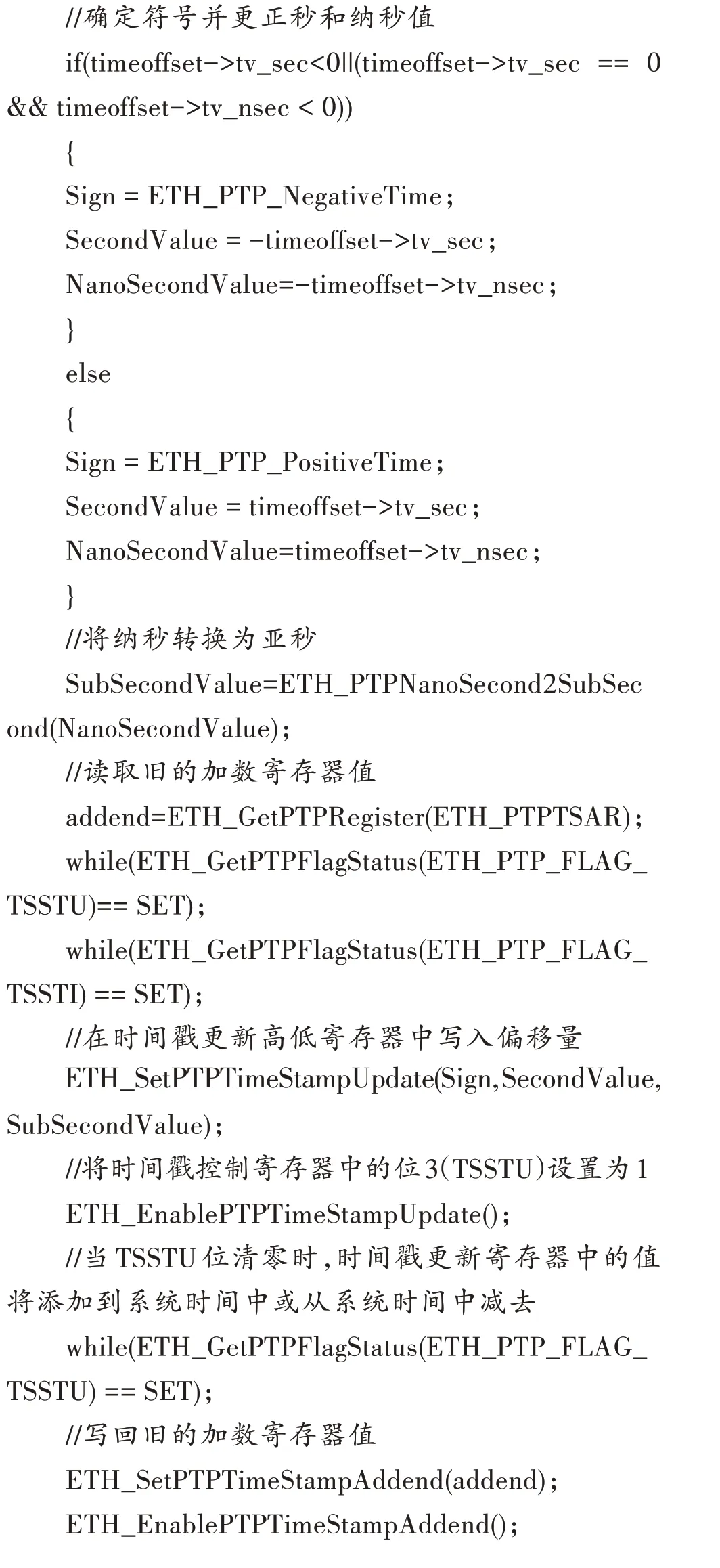

主时钟选用曼博格Meinberg LANTIME M500 时间服务器,外接一条GPS 天线用来接收外部的一个精准时钟源。嵌入式STM32 系统作为从时钟,两者构成主从关系,实现从时钟的同步。系统测试示意图如图3 所示。

图3 系统测试示意图

4.2 测试环境的搭建

系统测试硬件包括PC 机、基于STM32 从时钟系统、曼博格Meinberg LANTIME M500 时间服务器、安捷伦示波器、用于从时钟系统的12 V 转5 V 电源,数量均为一个。

系统测试软件包括Wireshark 封包分析软件、LogViewer 日志查看工具、Matlab 软件。

如图4 为搭建好的IEEE 1588v2 协议的测试环境场景图,左侧为基于STM32的从时钟系统,中间位置为曼博格Meinberg LANTIME M500 时间服务器和PC 机,右侧为安捷伦示波器。从时钟与PC 机通过串口连接,通过串口打印与时间相关的信息。PC 端通过抓包工具Wireshark 软件负责记录报文的收发,LogViewer 日志工具负责记录时钟频率和时间误差延时,Matlab 软件进行数据的仿真。主时钟曼博格Meinberg LANTIME M500 时间服务器外接GPS 天线,从外部接收一个精准的时钟源。安捷伦示波器通过主从时钟PPS 输出接口,输出主从时钟PPS的波形。

图4 系统测试环境场景图

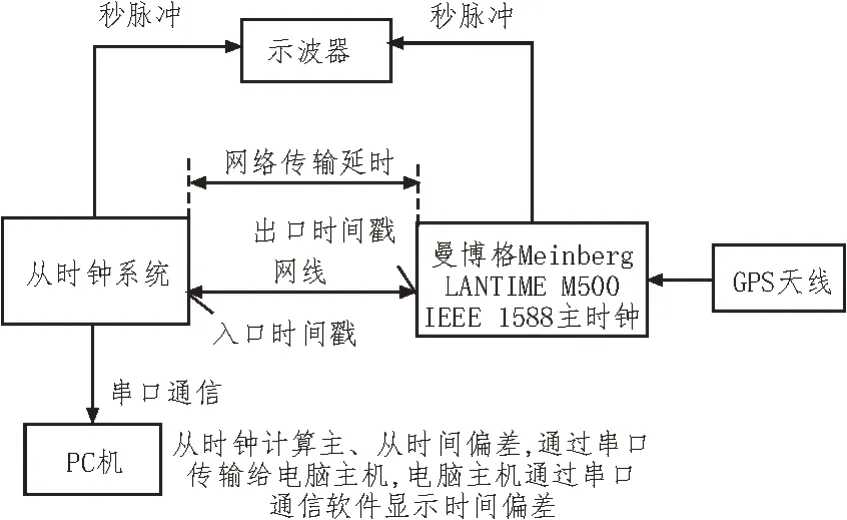

4.3 主从时钟PPS测试

主时钟通过PPS 输出引脚输出PPS 秒脉冲信号,用PPS的上升沿作为UTC的整秒时刻。纳秒级的同步精度,没有误差的积累。从时钟的DM9161A芯片被主时钟触发捕捉引脚[16-18],利用1 s的相位差进行时钟调节。通道1 连接主时钟的PPS 输出,通道2 连接从时钟的PPS 信号,两个上升沿即为时间偏差。系统精度测试方案如图5 所示。

图5 PPS秒脉冲测试方案

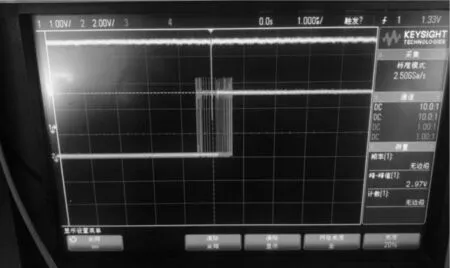

示波器采集到的波形图如图6 所示。上边实线为主时钟的PPS 信号,下边实线为从时钟的PPS 信号。示波器中每一个方格横坐标是1 μs,中间那条线作为参考基准,从时钟信号在参考基准的左右跳动,误差基本不超过1 μs。该测试结果符合LTE 小基站时钟同步精度±1.5 μs的要求。

图6 示波器PPS波形图

5 结束语

文中在基于主时钟曼博格Meinberg LANTIME M500 时间服务器的前提下,设计了一套基于IEEE 1588v2 协议的从时钟软硬件系统。选用支持IEEE 1588的微控制器执行时钟同步功能,实现低成本的网络化和精确的时钟同步。经测试,其精度满足LTE 小基站时钟同步精度±1.5 μs的要求。