基于计数时钟的两步式TDC 设计

岳 壮,刘 军,孙向明,杨 苹,裴 骅

(华中师范大学物理科学与技术学院硅像素实验室,湖北武汉 430079)

上世纪80 年代,时间数字转换器(TDC)就应用在高能物理、激光探测及核医学等领域,早期的模拟TDC 先将时间信号转换成电压信号,然后再经ADC 量化输出,其动态范围、最小精度都受ADC性能的限制,转换器的速度、功耗都受模拟电路的影响[1]。随着全数字TDC[2-3]的出现与发展,全数字电路将时间信号直接转换为数字码输出,解决了因模拟电路带来的一系列问题。当前主流TDC的实现方式有两种,一种是基于FPGA 实现的TDC[4-5],另一种是基于ASIC 实现的TDC[6-7]。基于FPGA 实现的TDC 具有较高的灵活性、较低的成本、周期短,适用于小批量多种类的应用;2020 年戴庆达等人设计的基于FPGA的高精度时间数字转换电路实现了分辨率约为11.7 ps[8]。采用ASIC 实现全定制型TDC 能实现更高分辨率、更低功耗及较小的占用面积,这些优势也使其被广泛应用;2017 年孙迪等人设计的流水线型TDC 时间分辨率为2.4 ps、动态范围为4.9 ns[9];2016 年Cheng Zeng等人设计的基于游标型TDC 分辨率为7.3 ps、功耗为1.2 mW[10];在此基础上发展形成的新型时间数字转换器,比如两步式时间数字转换器[11]、局部无源插值型TDC[12-13]、门控环形TDC[14-15]、时间放大器TDC[16]等在精度、动态范围、面积以及功耗等某些性能上都有着各自的优势,但也存在电路复杂、对工艺、温度和电压变化比较敏感等问题,这些问题都对设计提出了更加严格的要求。

文中介绍的TDC 是高能物理实验的量能器上应用的,该实验是为了研究CSR 外靶上产生的高压缩重子物质的状态,物理学家需要知道粒子碰撞之后产生的次粒子的能量、时间和位置信息,实验前端采用SiPM(Silicon photomultiplier)探测信号,经过加速对撞之后的粒子在零度角量能器内击中SiPM,输出不同的电流脉冲信号,不同脉冲信号经过固定阈值的甄别器后会得到不同脉冲宽度的数字信号,再利用TDC 对该数字信号进行边沿测量,从而得到信号的时间信息和能量信息,进而通过物理分析进行粒子鉴别。该实验中粒子对撞频率为1 MHz,SiPM的响应时间约为200 ps,因此要求TDC的精度小于200 ps,量程大于500 ns。该设计由PLL 提供精确的高频时钟,使用8 bit 计数器,实现了时间精度在70~200 ps可调,同时具有640 ns的动态范围。其中,高精度延时单元在外部可调电压的控制下,可以抵消因工艺、温度等外界因素带来延迟单元的变化,有效提高了TDC的测量精度和稳定性,在保证测量精度的同时满足大动态范围的需求。

1 系统结构

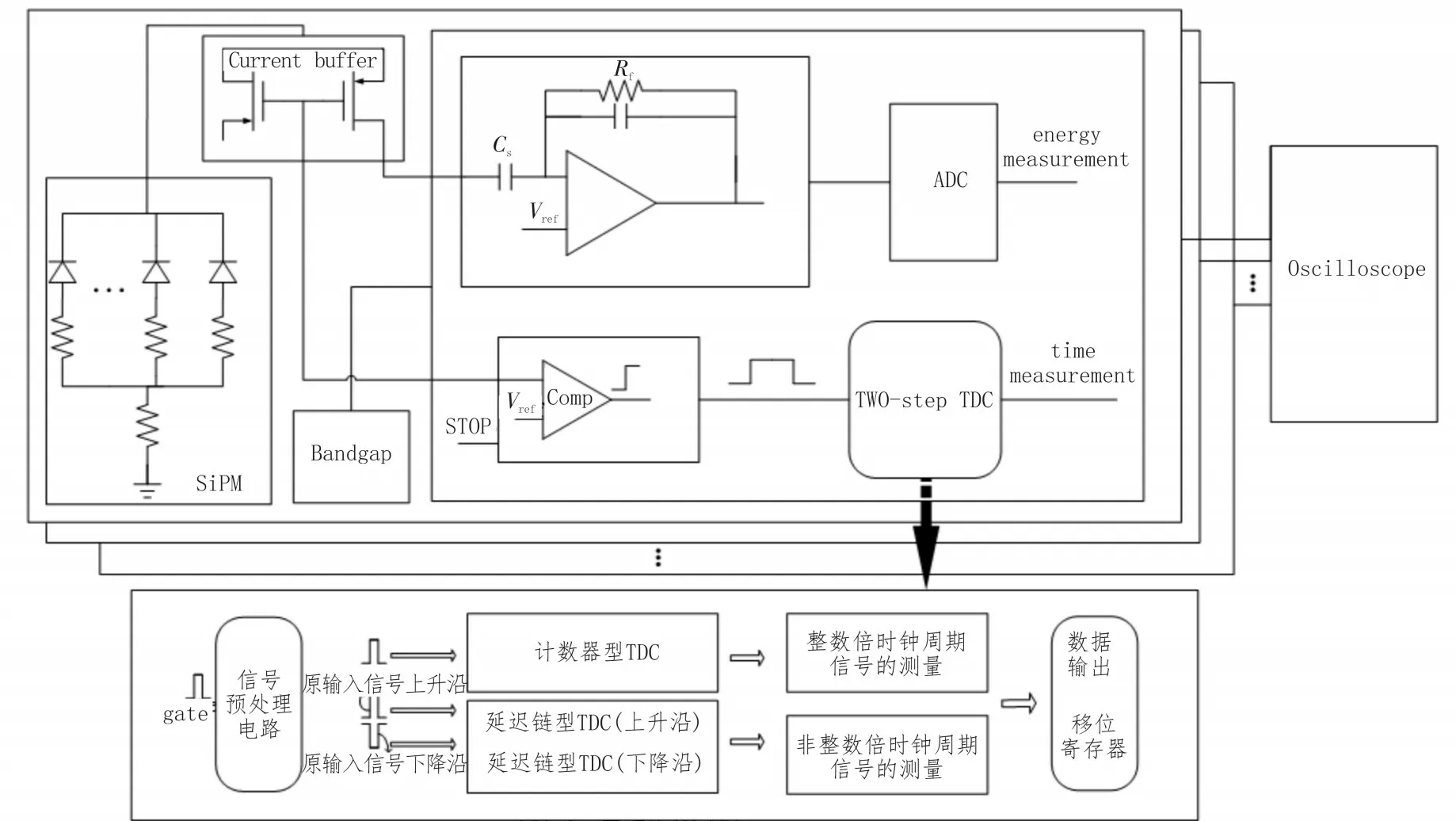

量能器中用于SiPM 探测器的读电路,当粒子击中SiPM 之后,SiPM 输出电流脉冲信号经Current buffer 电路分别送入时间测量通路和能量测量通路。在时间通路中,信号送入比较器之后与外部控制信号STOP 一起形成gate 信号,然后该gate 信号再通过TDC 电路进行脉宽测量。两步式TDC 电路主要包括信号预处理电路、计数器型TDC 电路及延迟链型TDC 电路。该TDC 电路对gate 信号同时进行粗计数和细计数,计数器型TDC 电路用来测量输入信号中时钟周期的整数倍部分,为粗计数;延迟链型TDC用来测量输入信号中不足一个时钟周期的部分,为细计数。在细计数中,因为D 触发器上升沿有效,所以原gate 信号的下降沿需取反之后再和原gate 信号分别送入延迟链型TDC 电路,为了进一步减小误差,信号预处理电路对原gate 信号增加一部分延时,保证其和取反之后的信号能同步送入计数器型TDC 电路和延迟链型TDC 电路,移位寄存器输出并行数据串行。系统框图如图1 所示。

图1 系统框图

2 电路设计

2.1 计数器型TDC电路的设计

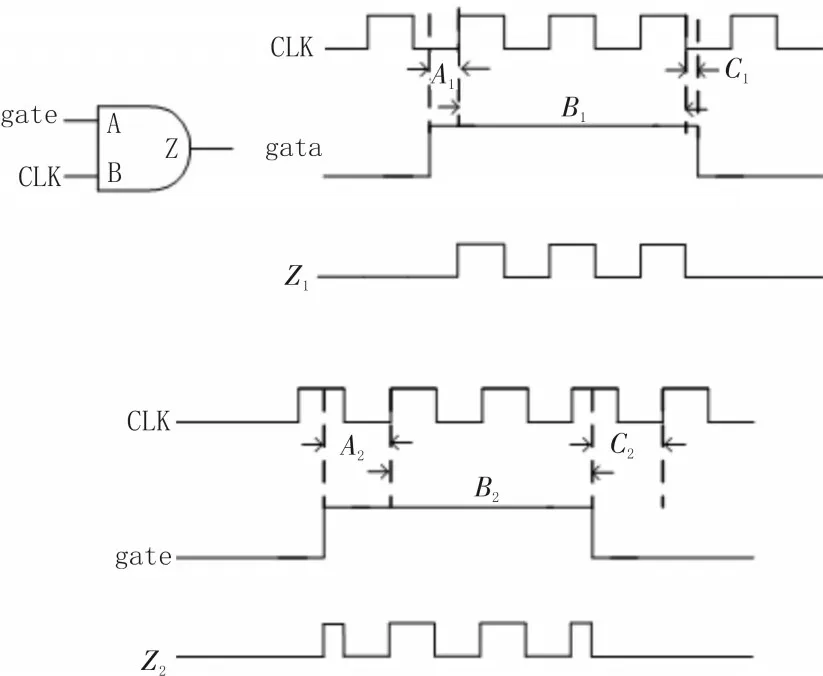

计数器型TDC 电路的目的是测量出gate 信号中整数时钟周期的部分,传统的取整数时钟周期方法如图2 所示,CLK 信号与gate 信号直接相与,输出信号Z1中的上升沿个数与B1中相同,然后将该部分信号送入计数器Clock 输入端,A1和C1为测量误差,该方法虽然简单但输出结果会出现错误情况Z2,因为无法保证gate 信号的上升沿会遇到CLK的高电平还是低电平,如果当gate 上升沿首先遇到CLK的高电平,相与之后输出结果中多出一个上升沿,则测量误差不仅包括A2、C2,同时会使计数器结果比实际值多1,因此需要对其进行改进。

图2 取整数时钟周期电路

改进后的电路结构如图3(a)所示,首先将gate 信号和CLK 送入D 触发器,输出结果再与CLK 相与,因为经过D触发器之后的信号A会有一个短暂的延时dt(大约几十皮秒),所以A的上升沿始终遇到CLK的高电平,解决了gate信号上升沿遇到CLK高、低电平的随机性问题,两者相与之后的信号Z作为计数器Clock的输入,进行粗计数。由于送入A端的信号比送入B的端的信号多经过一个D 触发器,导致A 与CLK 相与时会多出一个上升沿,如图3(b)中P点所示,而实际的gate信号中整数时钟周期并不包含该上升沿,因此计数器的结果减1后为实际粗计数结果。D触发器上升沿有效,当CLK的上升沿到来时A 才会翻转,所以dt1这部分时间并没有计算在内,为少计时部分,而dt2为多计时部分,这两部分需要延迟链型TDC电路进行细计数。

图3 计数器型TDC电路

2.2 延迟链型TDC电路的设计

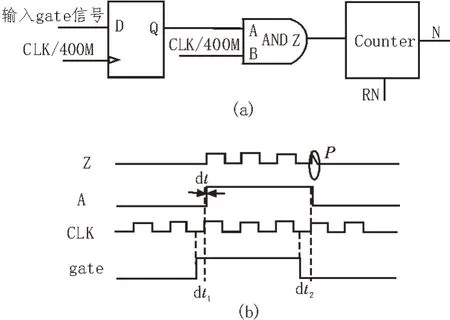

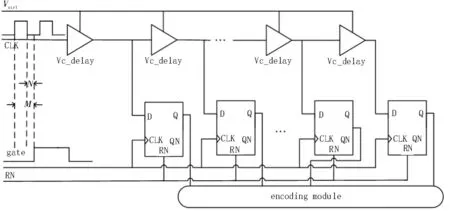

延迟链型TDC 电路的结构如图4 所示,电路主要由相位检测电路和高精度延时单元组成。CLK 信号作为延时链的输入,每经过一个延时单元后同时输入D 触发器输入端和下一个延时单元,gate 信号并行输入每一个相位检测D 触发器的时钟端,D 触发器上升沿有效,电路工作时,D 触发器会输出当前检测到的CLK 信号的高、低电平;因为gate 信号的上升沿遇到CLK 信号的高低电平是随机的,所以D 触发器的输出结果可能由1 至0 跳变,也可能由0 至1 跳变,L段时间为粗计数少计时部分,如果先遇到的是低电平时,当第N1个D 触发器由0 至1 跳变时,K段计时结果为TK=N1·Tdelay,则少计时部分L段的计时结果为,但是在实际情况中,输入的CLK 信号在多个延迟单元之后的占空比会发生变化,上述计算过程中不再是理论值,就会引入一定的误差;但是当用整个时钟周期进行计算时,占空比就不会再带来误差,当第N2个D 触发器由1 至0 跳变时,M段计时结果为TM=N2·Tdelay,则少计时部分L段的计时结果为TL=TCLK-TM,其中,Tdelay为延迟单元的延时,TCLK为CLK 信号的一个时钟周期,如果D 触发器输出为1至0的跳变,则标志着该延迟链计时结束。

图4 延迟链型TDC电路

2.3 相位检测电路的设计

在细计数测时电路中,相位检测是很重要的一部分,将gate 信号输入相位检测电路用来鉴别CLK信号由1 至0的跳变,所以电路延时小和低抖动都能减小测量误差。相位检测一般采用触发器锁存来实现,而各种触发器结构中D 触发器具有面积小、功耗低等优点。该相位检测器中D 触发器的结构主要由传输门、反相器和与非门构成,上升沿有效且具有复位功能。在该延迟链型TDC 中,D 触发器在每一级延迟单元拥有相同的负载,所以不会产生较大的偏移时间,同时通过每个MOS 管尺寸的合理设计,使其在传输1 G 信号时延时仅有几十皮秒,抖动约为0.3 ps,频率为1 GHz 时功耗为78 μW。

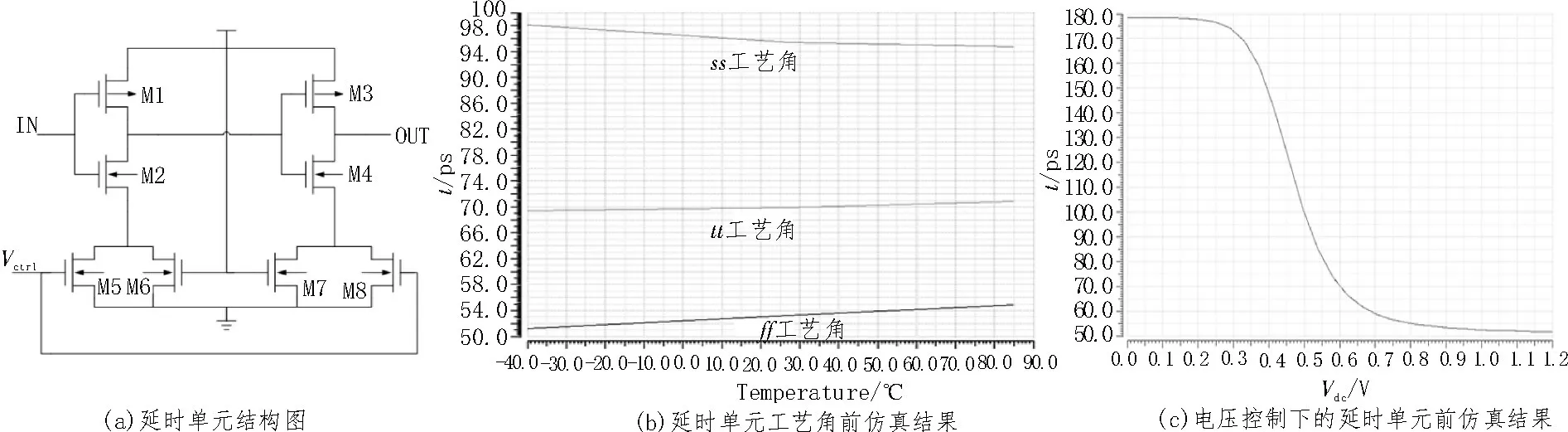

2.4 高精度延时单元电路的设计

延迟链型TDC的精度取决于单个延迟单元的延时,延时越小,测得的时间越精确,但对于同一个时钟周期,延迟单元的延时越小,一个时钟周期时长的延迟单元个数会急剧增加。因此延迟单元的时长要根据需求选取合适的值,该设计根据项目需求实现精度优于200 ps,动态范围大于500 ns的脉宽测量,选取延迟单元时长为100 ps 左右。传统的延迟单元由两个反相器构成,电路简单、功耗小、占用资源少,但延时受温度、工艺角影响很大。要保证延迟链型TDC 测量的准确性,则延迟单元的延时在外部环境影响下能保持稳定值至关重要。为了解决传统延迟单元延时不稳定的问题,将流过延迟单元的电流进行外部控制来改变其延时大小,如图5(a)所示为延迟单元结构图,Vctrl作为NMOS 管M5~M8的控制电压,通过改变Vctrl的值来改变流过延时单元的电流,从而达到调节延时单元延时的目的。

压控延迟单元在3 种极限工艺角slow(ss)、nominal(tt)和fast(ff)的仿真结果如图5(b)所示,温度变化范围为-40~85 ℃,横坐标代表温度的变化,纵坐标代表延迟单元延时的变化,单个工艺角下延时随温度的变化较小,但在不同工艺角下延时相差很大;理论设计延迟单元的延时70 ps,但在温度、工艺角的变化下延迟单元的延时在52~98 ps 范围内变化,很大程度上改变了延迟单元的延时,对结果的测量引入了较大的误差。电压控制下的延时单元前仿真结果如图5(c)所示,外部可调电压在0~1.2 V 变化时,压控延迟单元的延时变化范围为50~180 ps。因此,可通过外部电压调节来满足该项目对精度一致性的要求。

图5 高精度延时单元

3 仿真与版图

3.1 基于计数时钟的两步式TDC前仿真

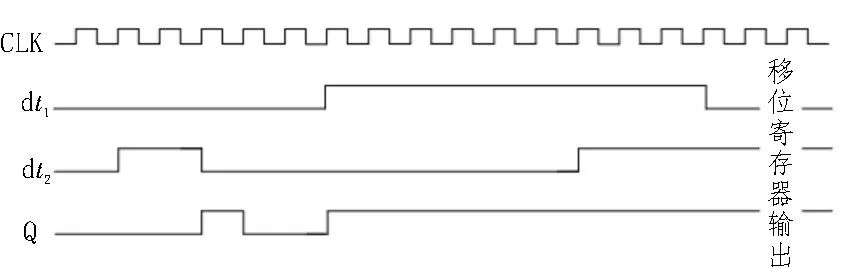

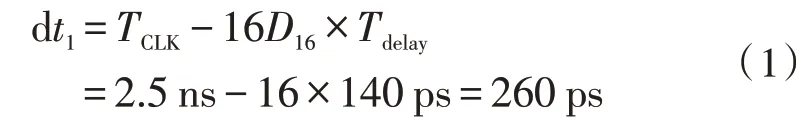

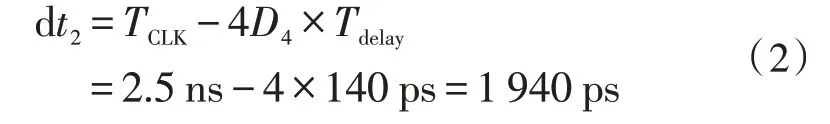

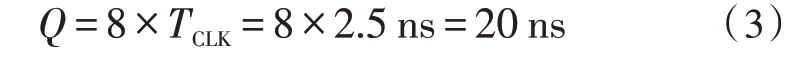

在时钟频率固定的情况下,延迟单元的延时和延迟单元的个数是相互矛盾的,考虑项目需求,TDC的分辨率小于200 ps、时钟频率为400 MHz,所以需对延迟单元的延时和个数进行处理,选择延迟单元的延时为140 ps、个数为20,保证延迟链的总时长大于一个时钟周期。在tt工艺角下,温度为27 ℃时的仿真结果如图6 所示。dt1为粗计数少计时部分,经移位寄存器串行输出后可知D 触发器在D16处由1 变为0,则有:

图6 两步式TDC仿真结果

dt2为粗计数多计时部分,由结果可知D 触发器在D4处由1 变为0,则有:

计数器测量结果为00001001,需要减去计数器自身带来的误差,则计数器结果为8,计时为:

即总计时为:

输入信号脉冲宽度为18.28 ns,与测量结果相差40 ps。其中Dn为第n个D 触发器,TCLK是CLK 信号的一个时钟周期,Tdelay为一个延时单元的延时。

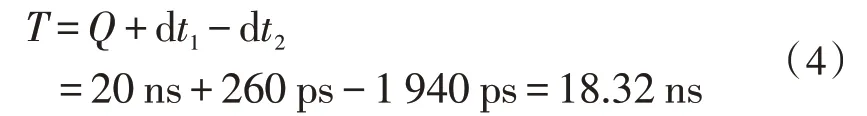

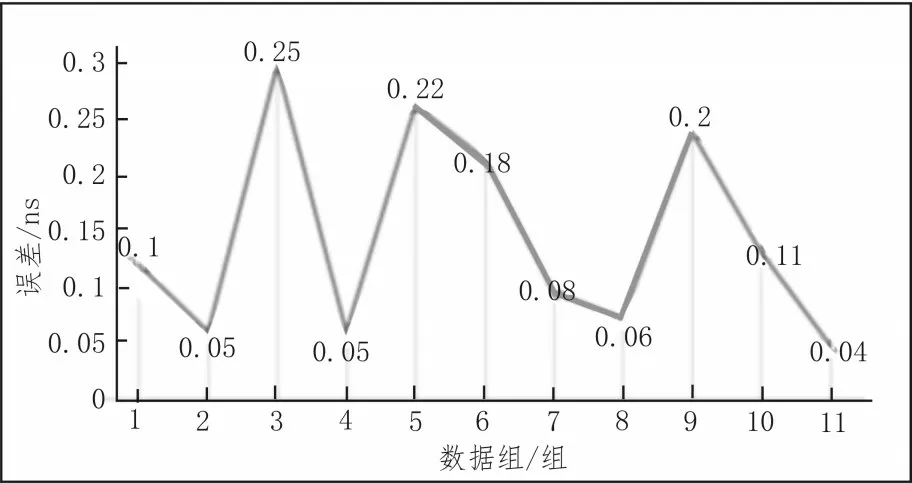

经仿真测试,前仿真整个电路的RMS 约为3 ps,多次测量结果如图7 所示,输入gate的宽度,从23 ns增加到630 ns,覆盖整个量程范围,测量结果误差均在1 LSB 范围内,如果将延时单元的延时减小,即降低1 LSB的大小,则能够得到更加精确的结果。

图7 前仿真结果

3.2 版图与后仿真

3.2.1 版 图

单通道核心电路版图中TDC 核心电路版图面积为300 μm×40 μm。版图中走线带来的RC 寄生参数会增加延迟单元的延时,为了保证延时一致性,延迟单元要具有相同的负载,所以延迟链型TDC 中的所有延迟单元等间距摆放并具有相同的走线方式,为了防止因走线过长而引入天线效应,可在长走线中插入缓冲器,数字电路用guard ring 隔离,减小模拟电路与数字电路之间的相互影响,电源电压在长走线中会存在衰减,所以在版图中进行电源环布局,使电压可以多通道输入电路,减小模块之间的电源误差。

3.2.2 基于计数时钟的两步式TDC后仿真

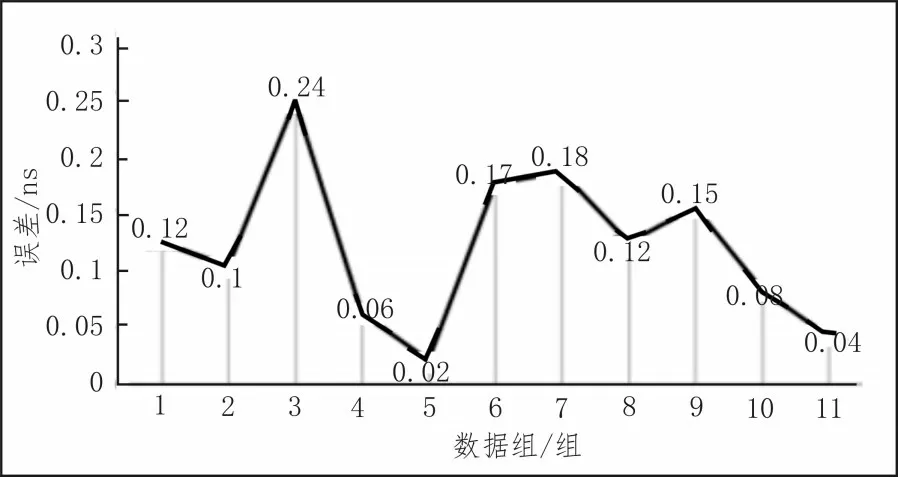

压控延迟单元工艺角后仿真如图8(a)所示,单个工艺角在温度变化的情况下延迟单元的延时变化较小,但不同工艺角在温度的变化下延迟单元的延时变化较大,在3 种温度、极限工艺角下,后仿真延迟单元延时变化范围为105~201 ps,图8(b)所示为电压控制下的延时单元后仿真结果,在外部可调电压控制下,延迟单元的延时范围是102~238 ps,该压控延迟单元在外部环境影响下仍有良好的表现,能通过电压调节使延迟单元的延时稳定在设计值。

图8 延迟单元后仿真结果

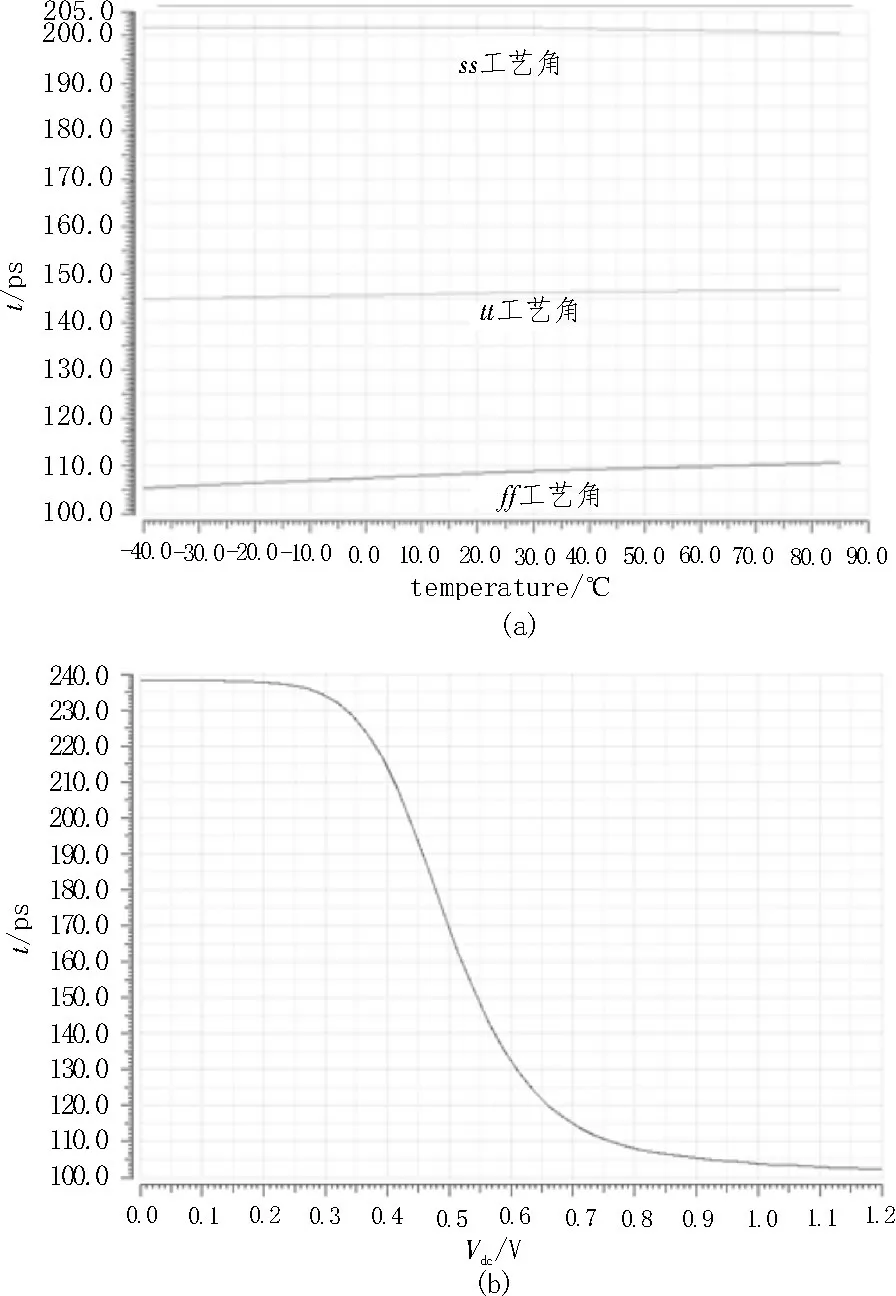

经仿真测试,后仿真整个电路的RMS约为3.4 ps,多次仿真结果如图9 所示,提取电路中所有的寄生RC 参数,输入数据覆盖设计中的整个量程范围,在版图布局、走线等影响下,输出测量结果误差均在1 LSB 范围内,满足设计指标的要求。

图9 后仿真结果

4 结束语

文中设计采用计数器型TDC 对输入信号进行粗计数,延迟链型TDC 对输入信号进行细计数,在保证分辨率的同时提供较高的量程。高精度延迟单元的设计能够有效提高延迟单元的稳定性,使在外部因素的影响下,延迟单元仍能调节到一个稳定值;该TDC的分辨率主要受外部时钟和延迟链长度的限制,提高时钟和增加延迟链长度可以提高分辨率,但同时也会给电路设计增加难度。TDC的分辨率由高精度延迟单元的延时决定,时钟频率和计数器的位数决定了TDC的动态范围。仿真结果表明,基于计数时钟的两步式TDC分辨率为140 ps、量程为640 ns、RMS约为3 ps、功耗为1.36 mW、面积为300 μm×40 μm,符合该项目的设计指标。以后将对设计电路进一步优化,减小延时单元的延时,同时延时单元内部可采用自动调节替代外部电压调节,进一步提高TDC的分辨率和精度。