基于VHDL语言的电子系统设计研究

张 甜,张 帆

(陕西邮电职业技术学院,陕西 咸阳 712000)

数字系统的整机设计正逐渐呈高速、小体积、大容量和轻重量的技术标准化发展,而以往自上至下的现存集成芯片所组成的大规模组合电路设计模式,已无法满足当前技术应用标准[1]。在PAL、GAL、CPLD等可编程器件基础上提出的ASIC(专用集成电路)和FPGA(可编程门阵列),被广泛应用于专用集成电路(ASIC)领域。面向特定用户的服务和批量种类需求较多时,能在较短时间内完成生产设计[2]。在ASIC及FPGA设计中,能够以电路系统行为及具体功能为依据,通过自上至下的设计描述,综合优化与验证模拟生成元器件[3]。VHDL作为一种高级工业标准综合描述类语言,可以将VHDL语言应用于电子系统设计中,实现电子系统处理器及外界信号接收设备之间的信号独立发送及接收,从而实现不同方向的数据传送操作[4]。安全监测平台设计要保证高效率,且在节约能源的基础上保护网络通信,这样能够充分降低不必要的技术损失。

1 TOP-DOWN技术

TOP-DOWN技术在系统设计过程中,能够基于概念、规则类驱动,在系统高层次设计的基础上,完成设计验证,包括电路及印刷版设计和底层ASIC版图等内容,这些都需要采用CAD技术手段实现系统电路的工艺、设计、测试一体化[5]。随着EDA技术及VHDL语言的飞速发展,各类新型技术也在发展中不断创新,基于TOP-DOWN的虚拟类原型技术设计,提供了有效的软硬件系统协同开发技术手段[6],常用功能模型设计有VME总线、DSPC40全功能、中断控制模型等。元件存放于EDA库内,在对系统设计过程中还需要运用差异化方案实现差异化EDA配置,用于筛选并优化方案。

2 VHDL语言技术

VHDL作为能够实现VHSIC加速研发的一种语言标准,主要包括VHDL及EDIF两大标准[7]。VHDL作为描述性硬件语言,通常运用于大规模数字类硬件电路系统设计中,如今也逐渐发展成为电子系统设计中普遍应用的工具型数字语言。VHDL语言拥有较丰富的语言描述功能,设计电路时能够获得非常抽象的描述,如PCB板级、芯片级、门级等,可以支持不同层次语言设计,所以TOP-DOWN全过程设计均需要运用同类型语言完成综合模拟论证。

VHDL语言包括五部分,分别是实体号说明、构造体、集合包、配置、库,前面四类均为可编译的源设计单元,库单元设计包括功能单元设计、用户设计和ASIC厂家元件设计[8]。

VHDL语言设计特点如下:1)语言功能强大,设计方式多样;2)具有强大的硬件描述能力;3)具有很强的移植能力;4)设计描述与器件无关;5)易于共享和复用。

3 电子系统设计

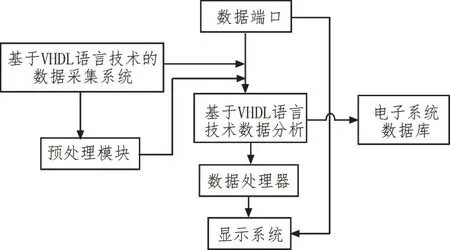

电子程序信息化对于国家及社会经济发展及人民生活水平至关重要[9]。经VHDL语言理论研究,在电子系统中应用VHDL语言理论原理,能够设计电子信息化系统[10]。运用VHDL语言设计电子系统流程如图1所示。

图1 电子系统VHDL语言计数流程图

3.1 电子系统可编程逻辑芯片

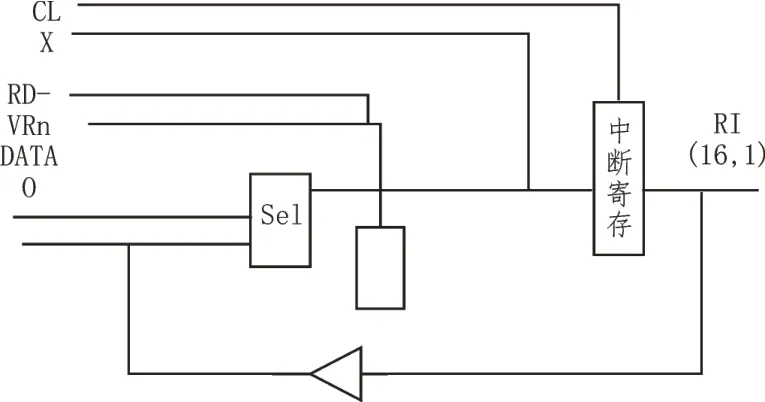

对于日常生活中所运用的电子产品,确保芯片的正常运行至关重要,关键在于保证软件芯片能够即时解读数据且实时存储。相关芯片具有中断功能,其中断接口功能图2所示。

图2 中断接口功能图

3.2 电子系统配置时序设计

对于电子系统建设,计算机VHDL语言技术的易用性十分关键,其电子系统配置技术水平决定了能否帮助用户高效率处理程序编辑。经过对操作人员的可编程芯片数据库进行实时更新,还可以自定义模块,多数电子系统的开关配置,均能很大程度满足相关工作人员的电子程序处理需求。在日常应用中,其简单易操作性可以更好地满足电子信息技术的需求[11]。如今的普通文件传输存储多数情况都选择绝对加密,对电子信息安全性形成有力保证,从而快速推进电子信息系统的发展进程。

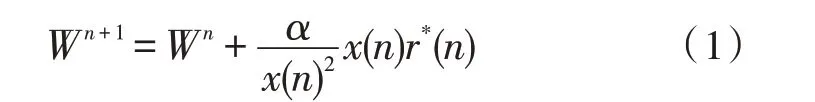

在电子系统信号来往过程中,拟定W表示模拟通信序列,r表示接收信号,静态传播信号的具体传播可以通过以下计算公式表示:

式中,α表示步长;x(n)表示电子系统的信号;r*(n)表示r(n)误差信号的共轭。结合以上能够发现,r电子信号越长,产生的信道干扰越大,因此想要提高电子系统的运作效率,就应当降低对信号的干扰,并获得最优化的电子系统性能。

4 中断控制器功能模块实现

数字系统设计始终基于CPU为核心技术,与其他子系统相结合,涵盖了部分组合类逻辑,能够有效控制不同的接口[12-13]。通常一个大系统又能够划分为多个功能子系统,可以逐层分解这些子系统直至元件层。其控制器可以划分为DMA控制器、总线、处理器与终端控制器、接口等组件,还能够进一步拆分为功能系统模块,且这些功能模块还可以进一步细化,直至最终成功细化至元件层,并且在这个细化过程中还可以选用VHDL语言,对不同阶段“实体号”与相应的结构定义进行说明,这样就完成了功能模块的全部设计。

以TOP-DOWN设计为例,设计中断控制器主要具备以下功能:

1)可以记录中断线,并有效消除线上存在的不稳定错误事件;

2)可以排定中断优先级;

3)能够屏蔽具体的中断能力,输出不同的中断编码;

4)设置相应的处理器接口、屏蔽位置接口等;

5)具备RESET信号接线,能够应用于控制器初始状态的有效控制。

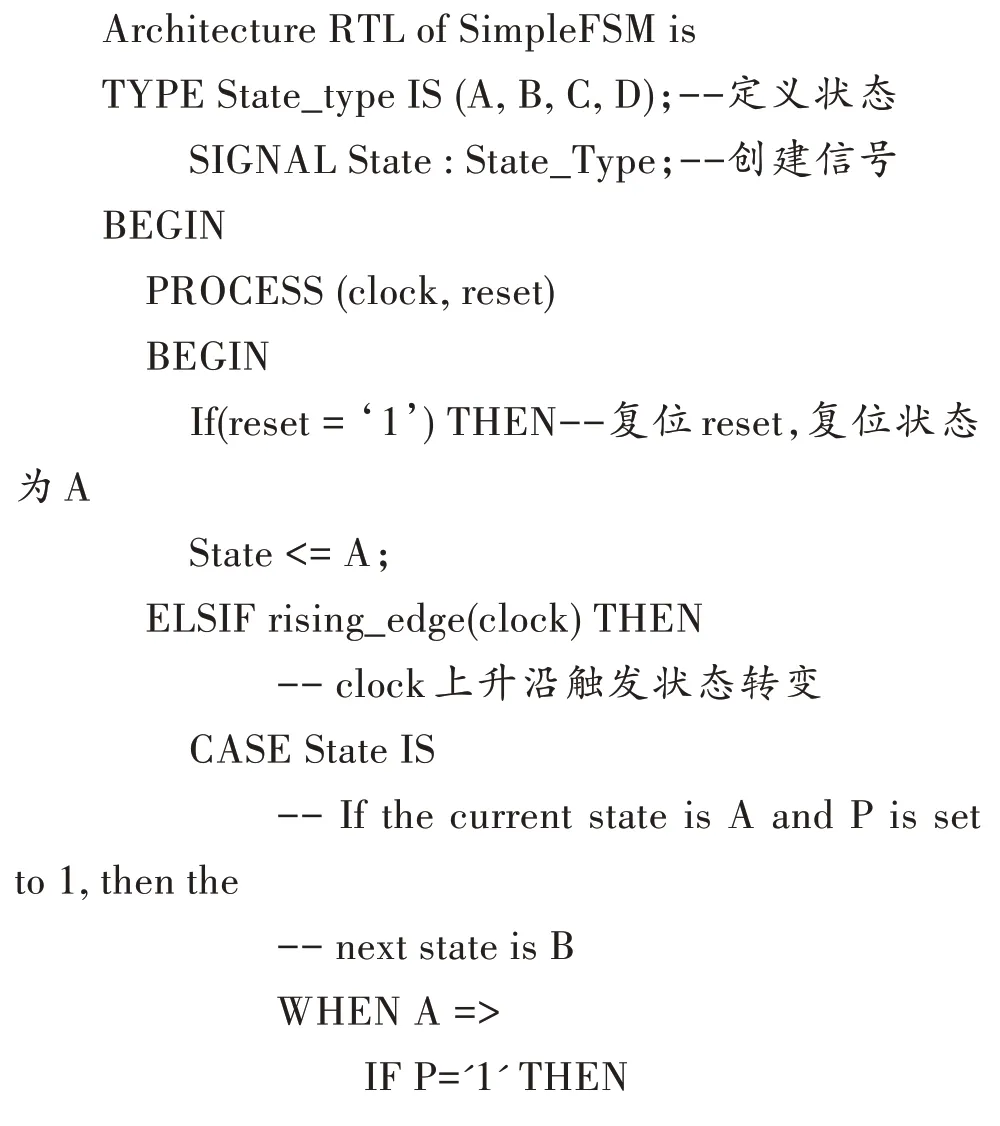

根据功能结构图可以编写VHDL的实体号,代码示例如下:

中断寄存器能够记录中断线的全部中断信号,并且可以经总线写入或成功读出全部中段寄存器存在的内容。中段寄存器结构图如图3所示。

图3 中段寄存器结构图

Bufoe模块作为VHDL库内存在的元件之一,在设计过程中可以将相应接口映射至中段寄存器的结构内部接口中。Bufoe元件框图如图4所示。

图4 Bufoe元件框图

5 实验论证分析

通过对传统电子系统工作流程展开研究,与本次设计应用的VHDL语言电子系统工作方法相结合,在实验中分析电子系统的实际运行工作效率,对比所测量的频率值,完成实验取样[14]。

通过分析能够发现,运用VHDL语言设计电子系统,可以在接收信号频率时有效降低误差[15]。由于电子系统无论在接收还是传播中,都存在不稳定因素,因此用传统的电子系统及VHDL语言设计的电子系统进行对比,对比实验数据如图5所示。

图5 对比实验数据

通过图5可知,应用VHDL技术的电子系统模型,能够获得更高的电子信号准确率和信号接收强度,证明了VHDL能够运用于电子系统设计中,有效增强电子系统的功能性,可以在一定程度上提升电子系统信息化水平。

6 结束语

文中研究表明,通过运用VHDL语言能够实现系统硬件描述,其具有强大的语言结构,可以描述十分复杂的硬件电路[16]。在电子程序信息化系统建设过程中,验证了基于VHDL语言电子系统设计技术的可行性,不但易实现且安全性高。在监测信号频率数据对比中发现,VHDL应用于电子系统设计中,能够真正增强电子系统的功能性,实现电子系统性能的最优化。