基于FPGA的可动态配置国产PCIe Switch应用设计

刘 鑫,林凡淼,刘 凯

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

PCIExpress(PCIe)总线是目前数据处理设备之间传输高速数据信号的主流总线。相较于采用单端并行总线形式的PCI/PCI-X总线,PCIe采用了高速串行差分总线形式,满足了处理器与设备之间高性能、高可靠性、易于布线的数据通讯需求[1-2]。

PCIe总线以PCIe Switch(PCIe交换机)为核心构建总线拓扑结构,广泛应用于芯片级、模块级互联,为解决长距离的系统级PCIe互连提供了新思路[3]。

1 PCIe总线要点概述

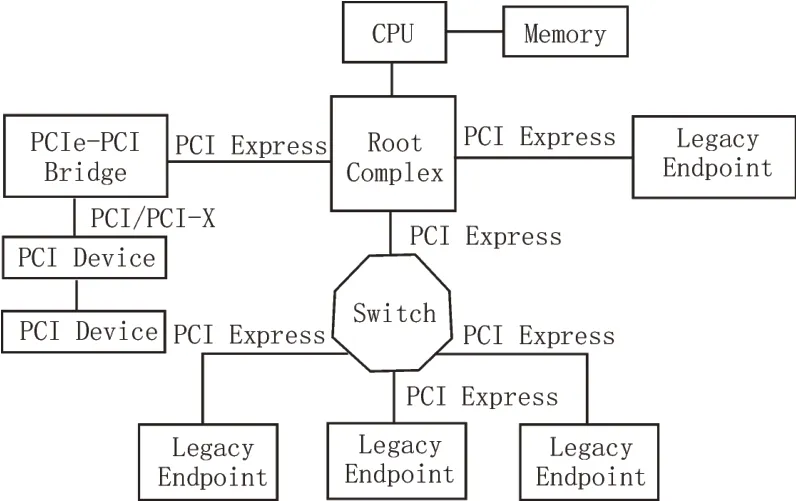

PCIe总线为全双工串行总线,为设备提供高速、高性能、点对点的通信链路,可以根据负载应用需求调整PCIe通道数量,进而改变设备的带宽。不同于PCI/PCI-X基于总线共享的交换模式,PCIe总线需要通过交换器实现多台PCIe设备互联[4]。典型的PCIe总线系统拓扑结构如图1所示。

图1 PCIe总线系统典型拓扑结构

PCIe总线系统主要由根复合体RC、交换器及端点设备组成。RC为CPU内部总线向外部总线过渡的通信媒介,是PCIe总线操作的实际管理者;Endpoin(t EP)处于PCIe总线系统拓扑结构的末端,接收来自上级拓扑的数据包或者向上级拓扑发送数据包[5]。

PCIe Switch对PCIe总线进行扩展,形成完整的PCIe总线拓扑结构,是支撑总线通讯的关键环节。PCIe总线规定,在一个Switch中与RC直接或者间接相连的端口为上游端口,其他所有端口被称为下游端口。下游端口一般与EP相连,或者连接下一级Switch继续扩展PCIe链路[6]。

2 国产交换芯片技术要点

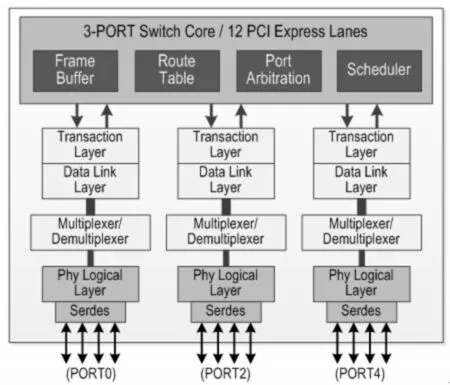

国产PCIe Switch芯片设计对照的国外芯片型号为IDT公司生产的89PES12T3G2,是一款基于PCIe-2.0总线协议的高性能交换芯片,广泛应用于服务器、存储器、网络交换器等设备。国产PCIe Switch芯片的内部功能简图如图2所示。

图2 国产PCIe Switch芯片内部功能简图

国产PCIe Switch芯片的主要技术特性如下:

1)具有12路5 Gbps PCIe-2.0通道(具备8/10编/译码器的SerDes接口),3个交换机端口(其中包括1个x4上游端口和2个x4下游端口),各端口自适应支持的链接宽度为x4,x2,x1,所有端口支持通道自动翻转;

2)具备低延迟快速转发交换架构,支持最大有效载荷为2 048 bytes;

3)具有一个Master SMBus接口,支持通过EEPR OM自动加载配置信息;

4)具有一个Slave SMBus接口,CPU、微处理器、FPGA等能够通过该接口访问PCIe Switch内部寄存器空间;

5)支持与PCI兼容的INTx及总线锁定;

6)下游PCIE端口支持热插拔;

7)具有9个通用输入/输出引脚,以及IO扩展功能。

3 PCIe扩展系统设计

由于台式机主板或嵌入式主板上的PCIe插槽数量有限,因此,需要利用PCIe Switch的扩展功能对PCIe总线拓扑结构进行扩充才能挂载更多的终端设备。采用国产化PCIe Switch芯片设计基于FPGA的可配置总线扩展系统,能够满足总线扩展的需求[7-9]。

3.1 系统方案设计

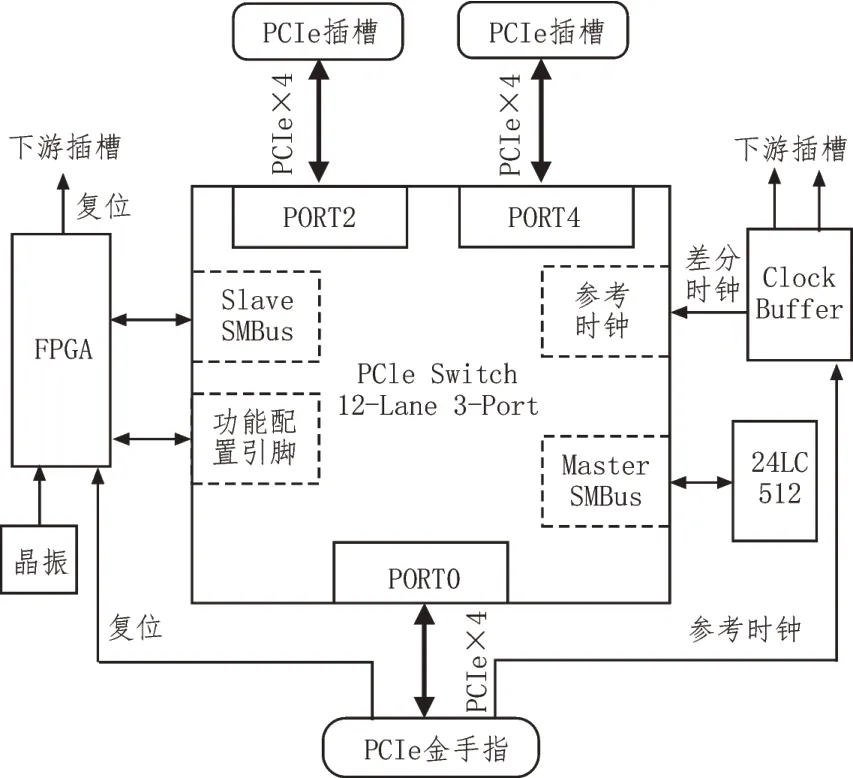

PCIe链路数据包的分发级联是国产Switch芯片实现的基本功能,同时芯片的其他基本功能,如启动方式、参考切换、复位模式切换等由特定的IO引脚进行设定,内部配置寄存器空间可以通过挂接在Master SMBus总线上的EEPROM进行初始化,也可以通过Slave SMBus总线在线修改配置参数。PCIe Switch总线扩展板方案设计框图如图3所示。

图3 PCIe Switch扩展板方案框图

该方案以国产PCIe Switch芯片作为核心转接芯片进行PCIe总线的扩展,同时采用FPGA芯片对芯片功能进行动态配置,从而实现以下功能:1)参考时钟管理;2)复位功能管理;3)Slave SMBus接口控制及配置空间访问;4)板级状态监控及管理等功能。除此以外,选用时钟Buffer芯片分别为下游两个插槽及Switch芯片提供高质量的差分时钟信号。

分析系统配置任务对FPGA的实际需求,选择Xilinx公司A7系列的XC7A100T芯片作为PCIe Switch的动态配置芯片,负责上电后的动态管理功能。该芯片的逻辑单元总数为101 K,最大分布式RAM为1 188 kb,Block RAM为4 860 kB,电源网络采用核压1.2 V,IO电平3.3 V,高性能与低功耗的芯片特性满足设计需求。

3.2 时钟及复位设计

PCIe Switch及PCIe设备根据情况可以选择100 MHz或125 MHz作为参考时钟。参考时钟架构采用PCIe-2.0协议推荐的Common Refclk Architecture方式,该方式要求Switch及下游设备采用相同的时钟源信号[10-11]。该设计采用上游金手指输入的参考时钟并用Clock Buffer输出至Switch及下游插槽。与此同时,采用内外源切换的冗余设计方式方便单板调试。

时钟Buffer选用ICS9DB803,该芯片输出时钟抖动小于50 ps,偏斜小于50 ps,工作在PLL模式时,输出频率为50~100 MHz,最多输出8路差分时钟信号,并具备输出使能控制。此外国产Switch芯片的参考时钟频率由REFCLKM引脚进行设置,默认置0时为100 MHz。

PCIe总线复位信号贯穿整个链路,信号由系统主板发出,由金手指向下传递至下游Switch或EP设备。将该复位信号分别接入国产Switch芯片的复位引脚以及FPGA的IO引脚,实现交换芯片内部复位功能以及FPGA配置翻转和复位监控功能。

3.3 Serdes硬件接口设计

PCIe采用全双工的串行差分信号进行通信,并引入了嵌入式时钟,PCIe Gen2采用8b/10b编码技术,使接收端可以从数据Lane中恢复出时钟[12]。国产Switch芯片内部采用Serdes器件实现PCIe中的PCS层和PMA层,接口通信速率为5 GT/s。

根据PCIe-2.0规范,总线两端设备的通道位置和极性可以交换顺序,因此,在设计PCB时,可以根据实际布线情况对PCIe通道的位置或极性映射关系进行调整,在PCIe链路初始化时由链路训练状态机完成物理层映射链接搭建。

PCIe差分信号采用高速布线原则进行布线,对于TX,RX全链路(包含过孔)的TDR单端阻抗要求为50±5Ω,差分阻抗要求为100±10Ω。另外在等长布线的基础上,还需要lane间的衰减相等。

3.4 FPGA配置电路设计

FPGA配置功能包括复位状态监控及分配管理、参考时钟配置管理、PCIe Switch配置管理等功能。上游复位信号由金手指的RESET#引脚接入FPGA,然后分别输出至下游的两个插槽,以及PCIe Switch芯片的复位引脚。FPGA根据上游复位信号状态管理当前PCIe Switch配置信息。参考时钟默认由上游金手指的REFCLK差分引脚输入,并经过ICS9DB803功分三路分别接入下游的两个插槽及PCIe Switch参考输入引脚。

PCIe Switch配置空间信息一般由操作系统在系统上电后进行配置,但是除了头标区64 Byte以外的配置寄存器一般由EEPROM在初始化时读入设定值且不再更改[13]。在常规应用中,该方法可行,但是在需要动态修改PCIe Switch状态信息的情况下时,缺乏灵活性。文中着重讨论采用FPGA由Switch芯片的Slave SMBus总线接口进行在线配置PCIe配置空间的方法。

4 FPGA程序设计

根据上述分析,FPGA首先需要实现SMBus主机总线接口的功能,用以与Switch芯片进行通信。在底层通信实现的基础上,对PCIe Switch的配置空间进行访问,实现动态管理功能。

4.1 SMBus接口时序需求

SMBus(系统管理总线)是基于I2C总线架构的两线制接口,各设备之间以及设备与系统的其他部分之间可以通过SMBus总线互相通信而不占用系统资源。SMBus总线设备分为主设备和从设备两种,主设备是用于发布命令、产生时钟和终止发送的设备;从设备是用于接收或响应命令的设备[14]。在该设计中,FPGA实现主设备功能,通过PCIe Switch芯片的Slave SMBus接口访问并配置寄存器。

在SMBus总线上,任何一个作为从模式的设备都有唯一的地址,即从设备地址。PCIe Switch从地址由引脚SSMBADDR[5,3:1]进行设置,该设计中全部置0。

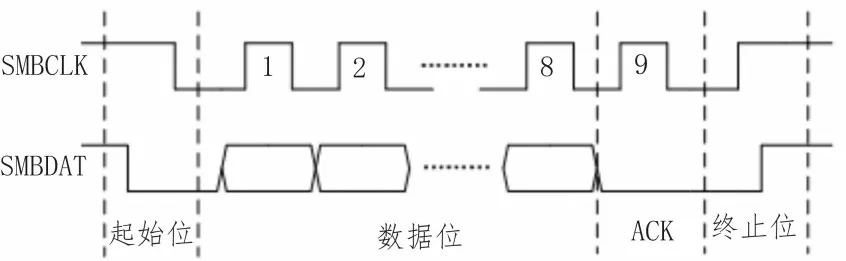

SMBus总线由一条数据线(SDA)和一条时钟线(SCL)组成,通信基本状态由起始位、8位数据位、ACK相应位以及终止位组成。SMBus总线的单字节传输时序图如图4所示。

图4 SMBus总线单字节传输时序图

根据上述分析,8位数据+1位ACK组成了总线通信协议的最小传输单元,实际的通信数据由多个字节与对应的ACK信号组成。当执行写操作时,数据位由主设备提供,ACK位由从设备返回0作为有效响应值,返回1表示无效并终止当前操作;当执行读操作时,数据位由从设备提供,ACK位由主设备返回1作为有效响应值,表示不会接收更多的字节,此时响应位即为NACK。

在数据传输过程中,只有在SCL信号为低电平时允许SDA变化,而在SCL为高电平时,SDA必须保持稳定。SMBus总线规范要求的最大传输速度为100 kHz,最小传输速度为10 kHz,即SCL周期为10~100μs。此外,SMBus具有超时功能,因此当SCL太低而超过35 ms时,从器件将复位正在进行的通信。

4.2 Block读写模块设计

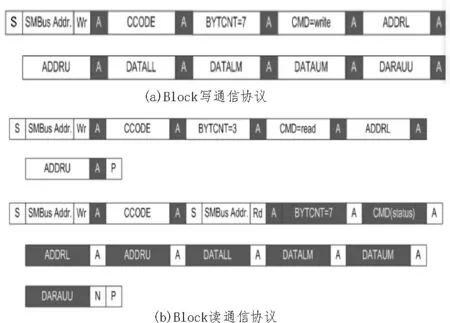

SMBus总线操作分为两种模式,一种是Byte字节模式,一种是Block块模式,PCIe Switch的SMBus操作同样兼容两种操作方式。首先实现的方式是效率更高的Block块访问模式。PCIe Switch的Slave SMBus块读写操作协议如图5所示。

图5 SMBus块读、写操作协议

FPGA访问Slave SMBus的通讯模块分为Block Read和Block Write两个子模块,分别与上述两个通讯协议相对应。分析协议可知,Block读操作以写操作为先导,包含Master和Slave的交互操作。以Block读模块为例进行详述设计,内容如下:

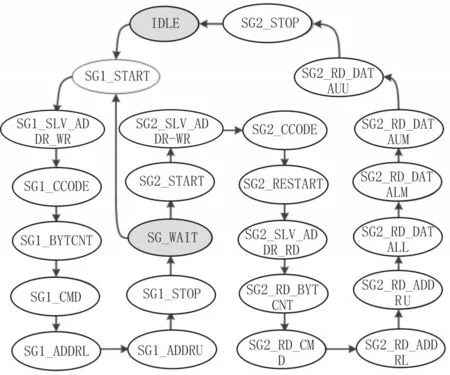

读取配置寄存器首先由Master发起写操作,分别由总线地址码、CCODE命令码、操作字节长度码、读命令码、配置寄存器地址码组成,然后Slave执行回传操作,在Master操作码的基础上增加数据码。图6为Block读操作的状态转移简图,详细描述了读操作的核心状态机切换功能。此外ACK应答异常响应处理程序会根据SDA状态判定当前的SMBus总线状态,选择是否主动退回至IDLE状态。

图6 Block读操作状态转移简图

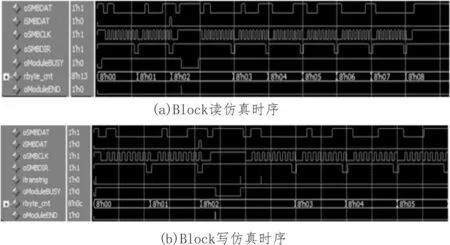

采用Verilog HDL语言设计Block读写模块代码及Testbench仿真测试文件,并采用ModelSim SE软件对上述代码进行逻辑仿真[15-16],得到对应的波形如图7所示。

图7 Block读、写仿真时序图

在仿真设计文件中插入了ACK应答无效的情况,模拟SMBus总线通信异常时的主机响应情况。从逻辑仿真时序图可以看到,主机Block操作进程能够从应答异常情况下恢复,并自发重启当前操作,同时给出异常报警指示。

4.3 PCIe配置模块设计

PCIe总线在软件上向前兼容PCI总线,并完整地继承了PCI总线中配置空间(Configuration Header)的概念。在PCIe总线中Header1代表桥设备,Switch每个端口(Port)都可以对应于PCI总线中PCI-to-PCI桥的概念。也就是说,Switch中一般都有多个类似于PCI-to-PCI桥的设备[17]。

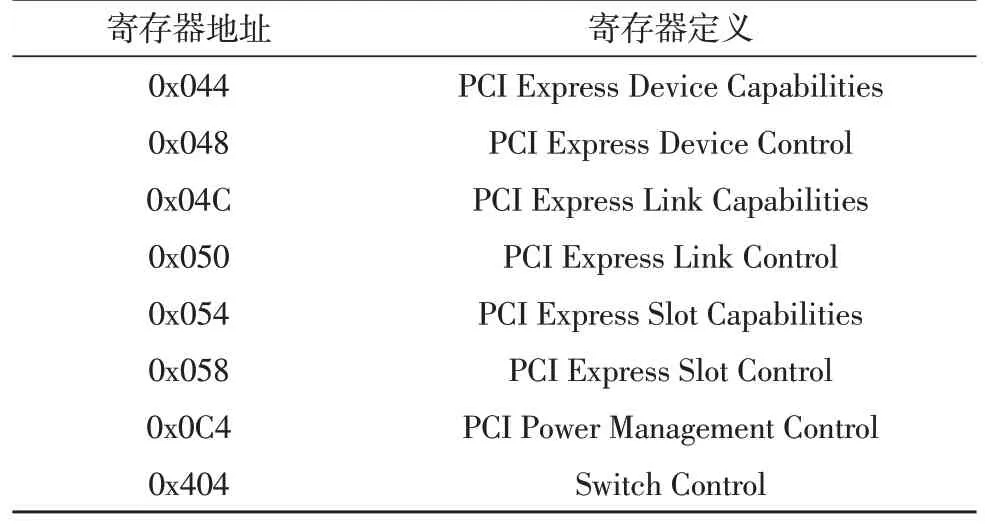

PCIe配置模块实现了对Switch配置寄存器的访问、管理以及设置功能。系统上电初始化阶段结束后,根据应用需要动态调整PCIe Switch的设定参数及功能目标。PCIe Switch的配置空间类型为Type1,配置头标区为0x000到0x03F共64 Byte,包括总线号、BAR空间地址分配等初始化信息。其余寄存器空间中需要动态调整的部分寄存器如表1所示。

表1 动态配置寄存器表

根据应用需求,Switch配置程序对相应的配置寄存器进行配置,并根据读数据给出配置完成情况。此外,程序会定时读取所有寄存器值并进行暂存,以备供电异常或者复位信号状态异常时重新恢复读值,出现总线无应答或者写入失败现象时,由外置LED状态进行显示。

FPGA程序功能仿真完成后,进行综合布局布线,然后通过Vivado进行在线调试,Debug完成后再将生成的.mcs文件烧入Flash芯片。

5 测试与分析

PCIe Switch扩展板上游为金手指,可以直接插入系统主板,下游两个插槽可以直接插入PCIe网卡等其他PCIe设备。测试系统采用x86主板平台,下游设备选用E82571千兆网卡。在系统测试前,首先对扩展板硬件进行上电调试,确认Switch芯片供电正常后再插入主板进行测试。PCIe链路上的所有设备随着系统上电启动进行初始化,完成BAR空间分配、PCI总线地址分配、设备驱动加载等工作。

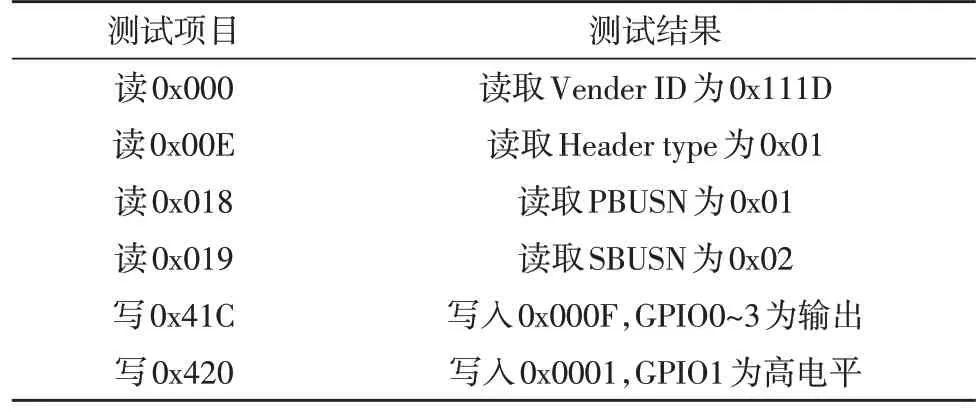

测试分为SMBus总线通讯测试和PCIe Switch动态功能测试两个内容。首先通过Vivado软件的Debug功能对PCIe Switch芯片的配置寄存器读写访问进行测试,测试表明SMBus总线读写操作正常。部分测试项目及测试结果如表2所示。

表2 SMBus总线测试结果

FPGA对PCIe Switch的动态设置采用异步交互方式切换设定。选取Switch Control&Status类寄存器进行测试,依次设置Fundamental Reset、Hot Reset、Disable Link Down Hot Reset等功能,观察扩展板工作状态,并通过远程访问下游E82571网卡工作状态,监控PCIe链路工作情况。测试结果表明FPGA能够通过SMBus总线设定动态功能,系统运行稳定、正常。

6 结束语

国产PCIe Switch芯片丰富了PCIe链路的拓扑结构,使PCIe总线更具扩展性和通用性。通过对Switch扩展卡的测试表明,基于FPGA的可编程特性能够充分利用国产Switch芯片的各项功能,在不调整硬件PCB的情况下适用于更多的应用场景,同时探索了在不占用PCIe总线资源的方式下,利用SMBus总线访问PCIe配置空间并进行动态设置及状态监控,为后续国产PCIe Switch芯片的大规模应用奠定了基础。