基于Innovus工具的IR Drop自动化修复

万 健 ,王 硕 ,邱 欢 ,陈飞阳 ,叶 林 ,武辰飞 ,2,欧阳可青 ,2

(1.深圳市中兴微电子技术有限公司 后端设计部,广东 深圳 518055;2.移动网络和移动多媒体技术国家重点实验室,广东 深圳 518055)

0 引言

在先进工艺节点下,芯片集成度极大提高,电源网络的电阻增加和高密度的晶体管(可称为Cell)同时翻转会在供电线(Power nets and Ground nets,简称PG)上产生IR Drop[1-4]。先进工艺下,5%~10%的IR Drop 可能会引起时序问题,20%~30%的IR Drop 可能会导致功能性障碍,因此在芯片设计过程中,IR Drop的预防和优化也就显得越来越重要。

本文中,基于Cadence 公司的自动化布局布线工具Innovus,利用IR-Aware Placement、IR-Aware PG Strape Addition 和Pegasus PG Fix Flow 这三种方法自动化修复设计的动态IR Drop,并对比分析各方法的优化效果。

1 芯片物理实现过程中的IR Drop 概述

1.1 IR Drop 定义

IR Drop 是指在集成电路中VDD 或VSS的电压的下降或升高的现象,综合考虑VDD 和VSS的IR Drop 为双边压降(本文中的IR Drop 均指双边压降)。IR Drop 过高,芯片就会出现时序问题甚至功能性障碍,使芯片彻底失效[5-6]。

动态IR Drop 是电路开关切换时电流波动引起的,更能反映芯片工作时的供电情况,所以本文主要探讨动态IR Drop的优化(下文的IR Drop 均指动态IR Drop)。

1.2 传统IR Drop 修复流程和局限

IR Drop的优化一般是在芯片物理实现后期进行,通常有三种方法:加cell padding 将cell 推开、添加稳压二极管减小电压波动、减小cell的驱动。但是以上方法存在如下局限:

(1)加cell padding 和稳压二极管时,很难仅针对IR Drop 违例的区域添加,会造成面积和资源的浪费;

(2)如果整体减小设计中cell的驱动,可能会造成严重的时序恶化;

(3)优化效率低,迭代次数多,IR Drop 修复工作量大;

(4)没有从补强PG 网络方面进行对IR Drop 进行优化。

2 IR Drop的自动化修复流程设计

针对传统IR Drop 修复方法的缺点,本文中利用IRAware Placement、IR-Aware PG Strape Addition 和Pegasus PG Fixing Flow 这三种方法在postroute 阶段对模块的动态IR Drop 进行自动化优化。

2.1 IR Drop的自动化修复流程设计

本文中利用一个在先进工艺下设计的模块为例进行说明,Floorplan 如图1(a)所示。模块面积约为555 μm×925 μm,instance 数目约为130 万,最高走线金属层为M17,最高频率超过1.0 GHz,Signoff 方式为SOCV(Statistical On Chip Variation)。模块的端口分布在四周,八边形的bump 打在M17 上,给底层逻辑供电。

图1 实验模块的Floorplan 和IR Drop的自动化修复流程设计

本文中会分别利用如图1(b)所示的三个自动化流程优化模块的动态IR Drop,并对比分析各方法的优缺点和优化效果。

(1)IR-Aware Placement

该方法会自动调用Voltus工具(Cadence 公司的功耗分析Signoff工具)识别设计的IR Drop hotspot 区域,并将在小范围内将这些区域的cell 推开,降低IR Drop 区域cell的密度,减小IR Drop,用到的命令主要是:

(2)IR-Aware PG Strape Addition

该方法也会自动识别设计的IR Drop hotspot 区域,设计者可根据不同区域的IR Drop 情况设置不同的PG pattern,利用命令可自动将这些PG 加在IR Drop hotspot区域,有针对性地优化IR Drop。例如,当IR Drop 大于5%时,设计多层的PG pattern 来进行优化,而IR Drop 小于5%时,设计单层的的PG pattern 来进行优化。用到的命令主要是:

其中,pattern_map 用于指定IR Drop 范围和用于优化的PG pattern。本实验中,当IR Drop 大于1.2%时,利用复合的PG pattern 就能在相应区域的M4、M6、M8、M11 和M13 上添加PG,优化IR Drop。

(3)Pegasus PG Fixing Flow

在Innovus 中可以调用Pegasus工具(Cadence 公司的物理验证Signoff工具)全局地或局部地添加PG,以优化IR Drop。用到的主要命令是:

add_pg_fill -fill -working_dir ***

该方法不会自动识别IR Drop hotspot 区域,需单独调用Voltus工具检验IR Drop 优化效果,添加的PG 为fill的形式,可以随时删除或添加,且不会造成新的DRC 违例。

2.2 IR-Aware Placement的IR Drop修复

本部分利用三次refinePlace 命令对模块IR Drop 进行优化,动态IR Drop的阈值定为6.54%(下同)。如表1 所示,三次优化后违例的instance 数目由2 893 降为1 914,违例数目减少33.8%,最小供电电压(Minimum Effective Instance Voltage,Min EIV) 从0.699 V 提高到0.721 V,提高3.1%,动态IR Drop 优化效果较为明显。

表1 refinePlace 前后模块instance 分布和比例

如图2 所示,三次优化后,模块在①处的IR Drop 改善比较明显,说明该处虽然cell 密度很高,但是有推开的空间。而在Memory 上和端口处的iobuffer 区域优化效果不明显。

图2 refinePlace 优化前后模块的动态IR Drop Map 图

如图3(a)、图3(b)所示,从局部来看,IR Drop的优化效果也比较明显。在第三轮优化时cell 移动的路径如图3(c)所示,该轮优化过程中cell 移动的平均距离为0.32 μm,最大移动距离为7.21 μm。

图3 refinePlace 前后模块局部的动态IR Drop Map 图和第三轮优化时移动cell的示意图

如图4 所示,随着优化次数的增多,移动的instance逐渐减少,违例instance 减少的速度变缓,且最小电压值的增速减缓甚至有恶化的趋势,这说明优化的力度随着优化次数的增加而减少,第一轮的优化力度最大,移动的instance 最多,违例的instance 减少了28.6%,Min EIV增加了2.7%。

图4 每一轮优化移动的instance 数目、最小供电电压值和违例instance 数目的变化

如表2 所示,每一轮优化后模块时序和DRC的变化较小,且运行时间均在100 min 左右,在可接受的范围内。

表2 三轮refinePlace 优化前后模块的参数对比

综上可知,利用refinePlace 命令进行三轮优化后,违例数目减少33.8%,Min EIV 提高了3.1%,IR Drop 优化效果比较明显,且对时序和DRC 影响较小,运行时间可控。随着优化次数的增加,工具的优化效率逐渐降低。

2.3 IR-Aware PG Strape Addition的IR Drop修复

IR-Aware PG Strape Addition的方法利用reinforce_pg命令来优化IR Drop。如表3 所示,优化后,IR Drop 较大的instance 数目减小,违例的数目从2 893 减小到2 367,减小18%,Min EIV 从0.699 V 提高到0.716 V,提高2.4%,IR Drop 优化效果明显。

表3 reinforce_pg 优化前后模块instance 分布和比例

如图5 所示,优化后,在①等高cell 密度区域和②、③等Memory 区域,IR Drop 有明显的改善。

图5 reinforce_pg 优化前后模块的动态IR Drop Map 图

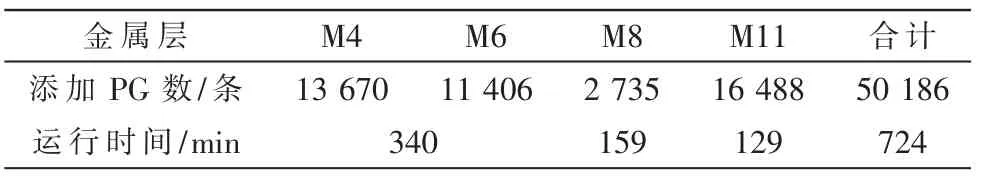

表4 为工具在各金属层添加的PG 和运行时间(仅指打PG的时间)。M4、M6 和M11 绕线资源比较丰富,添加PG 较多,而M8 和M13 等金属层绕线资源相对紧缺,添加的PG 数目较少。总体的运行时间为724 min,优化效率相对较低。

表4 各金属层添加的PG 条数

图6 为M4 和M11 上添加的PG,可以看出优化前的电源条均比较短,优化时工具会充分利用剩余绕线资源添加较长的电源条,补强设计的电源网络。但是在M11层会出现原始PG 和添加PG的重叠的情况,这个还需要后期进行流程优化。

图6 reinforce_pg 优化后在M4 和M11 添加的PG

如图7 所示,当添加PG的层数逐渐增加时,Min EIV也逐渐提高,违例的instance 数目减小。在M4 和M6 添加PG 时Min EIV 提高最快,这是因为这两层PG 孔能直接打到M0 和M1 等IR Drop 较大的金属层,给底层instance 提供更多供电点。当PG 打到了M11 和M13 等奇数层后,违例instance 减少的速率加快,这是因为高层走线电阻更小,IR Drop 也减小。

图7 添加多层PG 时instance 违例数目和最小供电电压的变化

如表5 所示,利用reinforce_pg 优化后,时序恶化较少。但是DRC的数目从82 条增加到了1 000 条,主要增加的违例是Short 和MinStep 等两类。Short 类型违例主要为在M6、M8 和M11 上电源线和信号线的Short,这是由于该方法优化时会忽略信号线的绕线造成的。MinStep的违例全在M11 层,由孔未完全包住PG 线造成,该类违例可通过减小PG的长度来解。此外,优化时添加的PG 多达50 186 条,难以直接通过ecoRoute 来解DRC。

表5 reinforce_pg 优化前后模块的时序和DRC

综上可知,利用reinforce_pg 命令的优化可减少18%的违例instance,优化模块的IR Drop,且对时序影响较小,但是使DRC 数量增加了13.5 倍。添加5 层PG的运行时间可达724 min,优化效率相对较低。此外,该方法能改善Memory 上的IR Drop。

2.4 Pegasus PG Fixing Flow的IR Drop修复

在Innovus 中可调用Pegasus工具全局地或局部地添加PG fill,增强设计的电源网络,优化IR Drop。如表6所示,优化前的违例instance 数目为2 893,添加local PG fill 和global PG fill 后instance 违例数目分别为2 717 和1 518,分别减少了6%和48%,Min EIV 均从0.699 V 增加为0.708 V,但是添加global PG fill 后平均供电电压(Average Effective Instance Voltage,Avg EIV)从0.814 V 提高到0.815 V,且IR Drop在0~2.18%范围的instance 数目更多,可以看出添加global PG fill的优化效果更好。

表6 添加PG fill 前后模块instance 分布

如图8 所示,添加global PG fill 后,模块在端口处的高cell 密度区域(如图8(b)的区域①和③)和部分Memory上(如图8(b)的区域②)的IR Drop 有较为明显的改善。

图8 添加global PG fill 优化前后模块的动态IR Drop Map 图

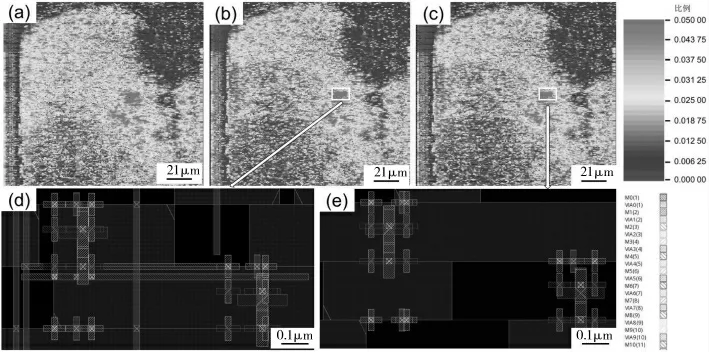

如图9 所示,可以看出,添加global PG fill 和local PG fill 都能减小IR Drop 违例的范围。如图9(d)、图9(e)所示,global PG fill 可以打得更长更密,供电效率更高,所以该类PG fill的优化效果也更好。

图9 优化前(a)、加global PG fill(b)、加local PG fill(c)后动态IR Drop Map 图和加global PG fill(d)和local PG fill(e)的放大图

如表7 所示,添加PG fill 后,时序情况基本维持不变(甚至稍有改善),优化后DRC的数目没有新增。利用6 个licence 可以在237 min 内添加4 120 962 条global PG fill,适合在postroute 阶段全面修复设计的IR Drop。

表7 添加PG fill 前后模块时序和DRC

综上可知,添加global PG fill的方式比local PG fill的IR Drop 优化力度更大,打上的PG fill 密度更高,且两总方法均不会使时序和DRC 恶化。此外,添加PG fill的方式能改善Memory 上的IR Drop。

3 结论

(1)利用Pegasus工具添加global PG fill的方法能使有IR Drop 违例的instance 数减少48%,且时序和DRC没有恶化,动态IR Drop的优化效果最好。

(2)利用refinePlace 命令优化IR Drop,instance 违例数减少33.8%,对时序和DRC 影响较小,IR Drop 优化效果比较明显。

(3)利用reinforce_pg 命令优化IR Drop,instance 违例数减少18%,对时序影响较小,但是使DRC 数量增加13.5 倍,且运行时间较长,优化效率较低。

(4)利用添加PG fill 和reinforce_pg 优化等方法可以改善端口处和Memory 上的IR Drop。