分时交替模数转换器通道失配校准技术进展

刘 聪,罗向东,牛光珊

(南通大学 信息科学技术学院,江苏 南通 226019)

近20 年来,随着通信技术迅速发展,现代通信系统对模数转换器(analog to digital converter,ADC)提出了很高的要求,往往需要其接收宽带、大动态信号。对ADC 来说,宽带和高频意味着快速的数据转换速率;大动态则意味着高效的采样精度。由于制造工艺的限制,单片ADC 很难同时满足这两个指标。1980 年Blank 和Hodges[1]首次提出了分时交替模数转换器(time interleaved analog to digital converter,TIADC)采样技术,作为一种多通道数据并行采集技术,TIADC 依靠各子通道间的精确配合,可以突破高速与高精度相互制约的瓶颈。利用TIADC技术是目前高速高分辨率ADC 设计的一种有效方案,它能够将系统的整体采样速率提高到每秒千兆次采样(Gsps)以上。

然而,由于器件不匹配、电压不稳定等环境因素的影响,各个通道间工作情况不可能完全一致,会造成各通道间存在失配误差。这些失配因素主要包括偏置误差、增益误差和时间误差,此外还有带宽误差及非线性误差,它们在信号的输出频谱中引入噪声,严重影响了TIADC 系统的性能。因此,如何校正TIADC 系统通道间的各种失配误差,提高系统整体的性能是目前国内外模数转换器数据通信领域所共同面临并亟待解决的关键问题之一。

1 TIADC 采样技术

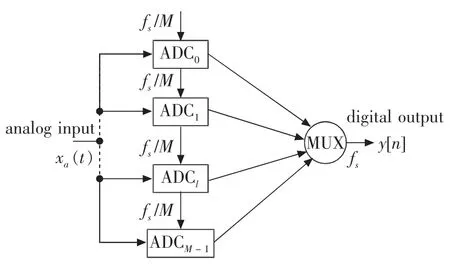

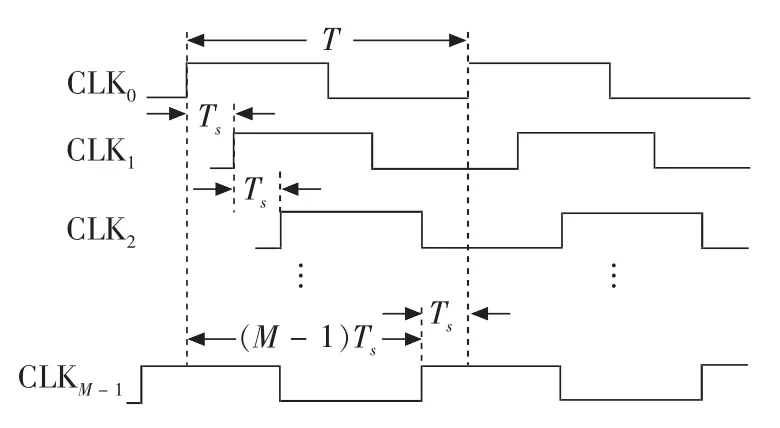

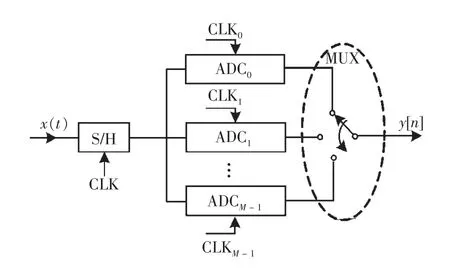

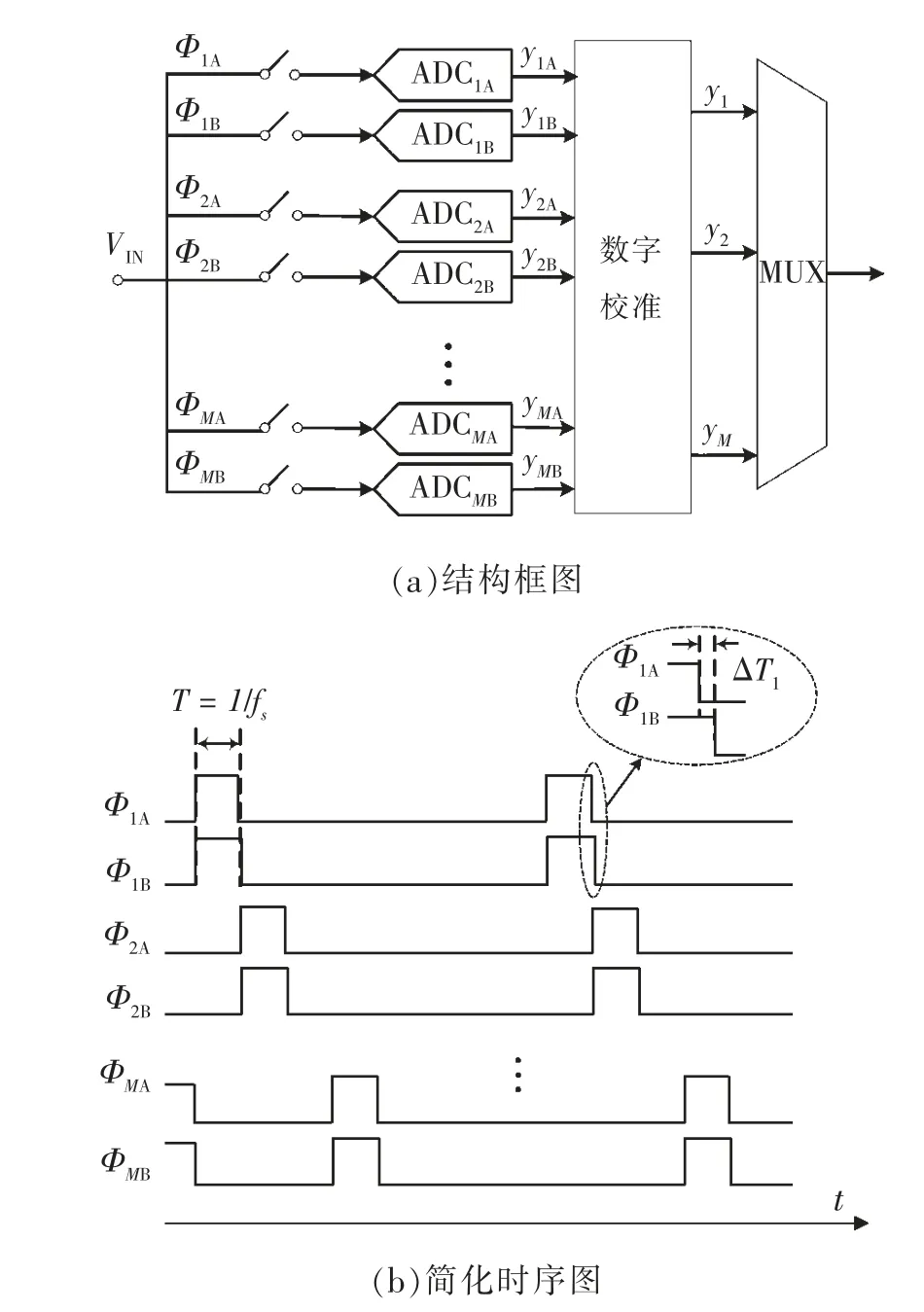

TIADC 系统由M 个完全相同的ADC 组成,并行工作,如图1 所示。系统中每一个ADC 实际上以较低的采样速率fs/M 进行采样和转换,而整个系统就可以实现更高的净采样速率fs(采样周期Ts=1/fs)。举例而言,通过分时交替4 个12 bit,250 Msps 的ADC,理论上就可以实现12 bit,1 Gsps 的TIADC 系统。子ADC 的采样时钟是通过时钟分相电路产生,该电路将采样时钟周期为T 的时钟信号先送入第1片ADC 中,然后延迟1 个Ts时间间隔送入第2 片ADC 中,依次类推,直至采样时钟经过M-1 个Ts延时送入最后一片ADC,形成各个通道的时钟信号,使得Ts=T/M 成立。TIADC 的工作时序如图2所示。

图1 具有M 通道的TIADC 结构示意图Fig.1 Structure of TIADC with M channels

图2 M 通道TIADC 工作时序图Fig.2 Timing diagram of TIADC with M channels

理论上,TIADC 系统可以在按照通道数成倍地提高采样率的同时保持单片ADC 的精度,实际上TIADC 系统会产生通道间失配,这些失配因素包括以下诸多原因:1)工艺制造技术的限制,使得器件不匹配及电路结构不对称,导致了偏置误差和增益误差的产生;2)延迟单元或时钟缓冲区中的器件不匹配及时钟信号在硬件电路布线上的延迟和抖动使得TIADC 非均匀时间间隔采样,导致了时间误差的产生,包括时钟抖动和时钟偏斜;3)由于制造工艺的缺陷,各通道的输入电阻Rin和互联电容Cin引起误差,或是ADC 的采样电容C 和开关电阻Ron,以及它们之间的互联引起误差[2],都会造成系统带宽失配;4)各通道采样保持器输入相关电荷注入、跟踪非线性及运算放大器等模拟器件的非理想特性带来的非线性误差大小不同,导致系统产生非线性失配。此外,温度、电压、老化等环境因素也会导致误差产生。

这些失配误差对TIADC 系统的影响主要体现在以下几个方面:1)偏置误差导致通道间直流偏置不一致,在时域上相当于加性噪声;2)增益误差导致输入信号的幅度调制,在时域上相当于乘性噪声;3)时间误差对时域的影响表现为数字信号幅值发生畸变,对频域的影响表现为频谱拓宽,寄生谱峰[3]等;4)带宽误差与输入信号频率有关,实际导致输出信号的增益和相位不匹配;5)非线性误差导致各通道ADC 产生高次谐波,使得TIADC 的并行结构在输出频谱中引入额外误差谱。以上这些失配会导致信号谐波失真,并极大地限制了系统的性能。因此,作为不可避免的因素,TIADC 系统的通道失配需要通过有效的方法进行校准。

2 TIADC 通道失配误差校准技术分类及实现方法

2.1 TIADC 通道失配误差估计技术

研究人员在设计和优化TIADC 通道失配误差校准方法之前首先重点关注如何检测并提取出失配误差。在研究如何估计TIADC 通道失配误差时所采用的方法之一是基于正弦波拟合的算法[4-6]。其原理是用一个已知信息的正弦波输入信号对系统进行测量,对各通道采样输出进行参数拟合,通过估算得到每个通道的增益、偏置和相位参数[7]。文献[8-9]利用最小二乘法对正弦信号进行参数拟合,利用插值获取非参考通道的理想输出,再比较理想输出和实际输出的区别,从而获取系统误差。文献[7]采用正弦波四参数拟合的方法估算了通道失配误差,相比三参数拟合法,该方法还能够得到系统的频率信息。采用基于正弦波拟合的算法优点是能够较全面准确地估计得到整个系统的通道失配误差,缺点是依赖于高精度的正弦波信号。

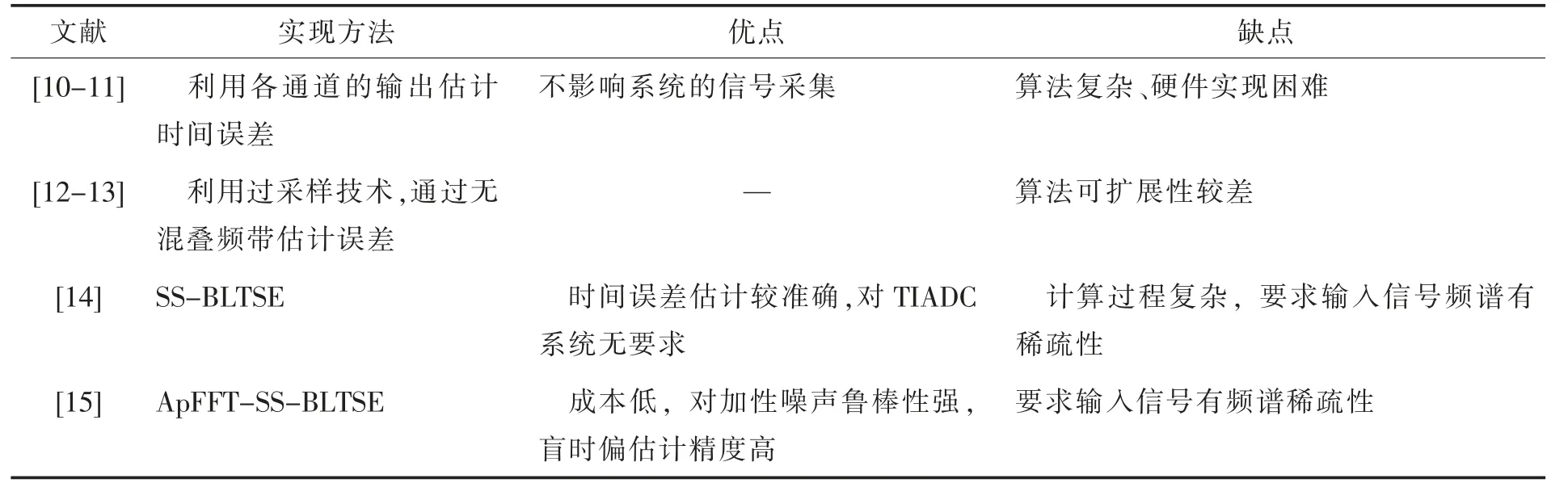

盲估计作为TIADC 通道误差估计技术之一也吸引了大量的学术研究,其最大的优点就是不需要获取输入信号的已知信息。文献[10-15]采用了几种不同的盲估计算法,其优缺点如表1 所示。

表1 盲估计算法优缺点总结Tab.1 Summary of advantages and disadvantages of blind estimation algorithms

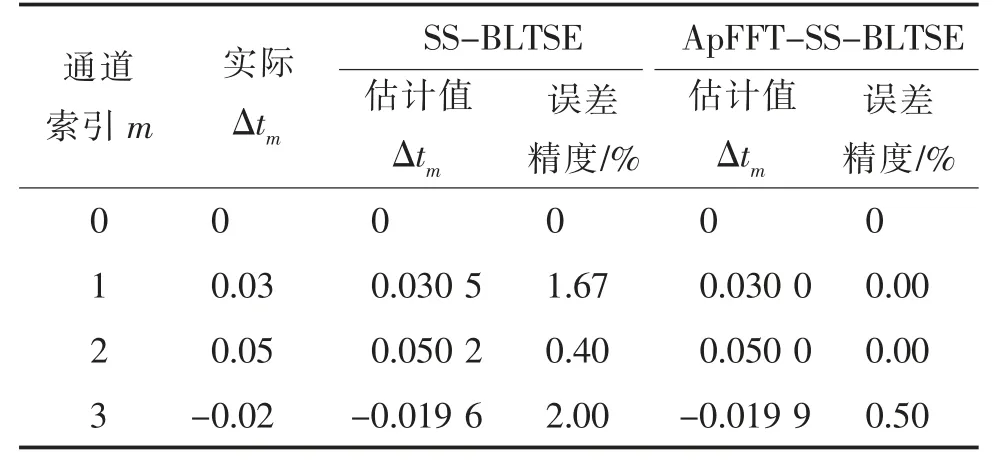

其中,基于频谱稀疏性盲时偏估计(spectrum sparsity-based blind timing skew estimation,SS-BLTSE)算法,需要一个N 点FFT 来确定非重叠频率分量及其相位信息,N 越大,误差估计越精确。文献[15]在文献[14]的研究基础上提出一种基于频谱稀疏性和全相位FFT(all phase FFT,ApFFT)的盲时偏估计算法,由于FFT 谱估计存在局限性,如由频谱离散化引起的窗口和栅栏效应,会导致“频谱泄漏”,故利用ApFFT[16]技术获得更为精确的相位谱估计,并在此基础上得到ApFFT-SS-BLTSE 算法。两种算法的TSE 对比结果如表2 所示。综上,盲估计算法需要信号过采样,并会消耗额外的硬件资源,如低通滤波器和额外的ADC。与非盲估计算法相比,其误差估计性能性[14],但是在实际使用中相对灵活。

表2 两种盲时偏估计误差结果对比Tab.2 Comparison of two BLTSE results

利用FFT 算法,从频域特征获取通道失配也是一种常见的方法。文献[17]使用FFT 计算获得增益误差,但其计算量比仅用简单乘法获得增益误差的方法稍显复杂。文献[18]基于FFT 算法估计得到TIADC 系统的增益误差和偏置误差。该方法的优点是没有通道数限制;缺点是没有给出硬件描述,并且FFT 实现存在缺陷。除此之外,文献[19]利用相邻两通道的差值来估计时间误差,算法简单,缺点是收敛速度慢。文献[20]通过额外增加一个辅助通道来检测失配误差,能快速实现误差估计和校准,缺点是增加了系统的复杂度。文献[21]利用待校准信号误差的统计特性,利用输入信号的均值和方差来估计和提取TIADC 通道的偏置误差和增益误差,该算法硬件成本低,易实现。文献[22]将数理统计和频谱分析相结合,分别估计得到偏置误差、增益误差及时间误差。该方法简单易实现,在算法性能上优于正弦拟合算法。误差估计方法虽然很多,但是需要根据具体的情况配合校准方法完成误差校准。

2.2 TIADC 偏置和增益误差校准技术

作为线性误差,偏置误差等效于各通道输出直流分量的偏差,增益误差等效于各通道输出绝对值的比值。基于这种数理机制,通常采用数字域校准技术完成误差校准。数字域校准指TIADC 系统的误差估计和校准都利用数字电路实现,根据校准过程是否阻断ADC 正常的数据输出又可将数字域校准划分为前台校准和后台校准。前台校准要求ADC校准过程中暂停工作,校准完成后再进行转换;后台校准是在ADC 工作的同时,通过数字信号处理技术提取通道失配的估计值,同步校准误差[23]。

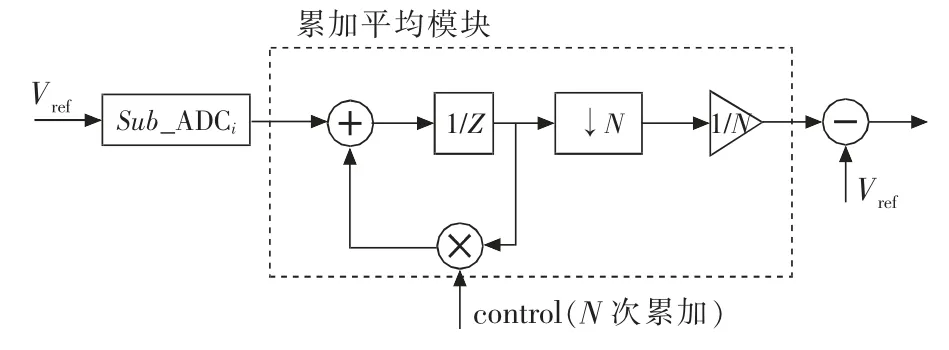

偏置误差和增益误差的校准最早使用的是前台校准方法。文献[24]利用已知输入信号进行测试,分析经ADC 转换后的数字输出,提取出偏置失配误差参数,再反馈到硬件电路中,通过调整各通道ADC 的偏置电压及前端放大电路的零点做校准。文献[25]在TIADC 系统输入一个已知的参考电平Vref,经ADC 转化后输出,将输出结果与Vref相减得到偏置误差并保存,将各子ADC 的输出减去偏置误差即可完成校准,如图3 所示。其中,控制信号control 用于完成采样序列的N 次累加。同理该方法可以应用于增益误差校准。这类前台校准方法优点是校准速度快、精度高、易于实现;缺点是必须要中断系统的正常工作,不能实时校准,主要用于系统维护等情况。

图3 偏置误差的前台校准Fig.3 Foreground calibration of offset error

相比前台校准,后台校准不会影响系统正常工作,能够实时估计和校准失配误差,因此成为目前的研究重点。文献[26]提出一种类似随机斩波法的增益误差校准方法,如图4 所示。将一个±1 的伪随机序列通过一个1 bit 的DAC 叠加到系统输入端,利用乘法器对包含叠加信号的输出解调,通过累加平均提取出误差并完成校准。该方法避免了各通道采样信号幅度的误校准情况,但是需要额外电路资源,且对输入信号进行调制将导致信号动态范围降低。

图4 具有随机信号注入的增益误差后台校准[26]Fig.4 Background calibration of gain error with random signal injection[26]

随着ADC 自身的工作能力和环境条件的变化,TIADC 通道失配也会发生改变,因此,后台校准大都与自适应技术相结合,利用TIADC 输出时域或频域上的某种特征作为反馈量,能够跟踪失配参数的变化,自适应地改变校正网络参数,控制校准过程[27]。文献[28]提出一种由导数滤波器和额外的参考通道组成的自适应补偿结构,利用时钟控制参考通道与子通道在某些时刻同步采样,通过对比参考通道和子通道导数滤波器组的输出得到通道静态增益误差,进而完成校准。该方法对于AD 量化为14 位的TIADC 系统,校准精度达到约12 位。文献[29]提出了一种流水线后处理器结构,采用自适应滤波技术,将后处理算法LMS 算法应用到ADC 的输出码中,跟踪失配随时间的变化,估计并校准偏置误差和增益误差。该方法只利用了一个校准单元实现所有通道的校准,大大降低了硬件要求和功耗,并且能够在FPGA 上硬件实现,缺点是TIADC 校准精度一般,通常不超过10 位。文献[30]利用样本输出构造误差函数,通过计算误差函数的导数来获得偏置及增益的调整步长,并通过改变偏置和增益误差来减小误差函数值。该方法适应性强,精度较高,对8位TIADC 系统进行校准,精度达到7.69 位,缺点是导数计算将消耗系统更多资源,且时间成本也较高。文献[31]为了校准嵌入在数字通信接收器中的双通道TIADC 增益误差,提出一个新颖的基于完美重构通道器的校准结构,利用LMS 算法估计误差,结合FIR 滤波器校准,成功过滤了信号中的混叠音调。该方法具有硬件可行性,缺点是有通道数限制。此外,文献[18,21,32]专门针对偏置误差和增益误差进行了校准,重点是研究其估计方法,这里不再赘述。

2.3 TIADC 时间误差校准技术

偏置和增益误差对输出的影响是有规律的,而时间误差由于受到输入信号频率的影响,难以从输出结果中直接提取,并且随着该频率的增加,误差对系统性能影响更严重。因此,时间误差的校准最困难,也最有研究价值。目前,针对时间误差校准技术的研究进展体现为以下3 个方面:

1)模拟域校准 模拟域校准是指在模拟电路设计过程中针对误差设计相应的模拟电路以完成对误差的检测和校准[33]。对于时间误差的校准,首先考虑从源头上消除误差。文献[34]采用单一的前置采样保持(SHA)电路。其基本思想是使每个子ADC 的采样时钟保持同步,从根本上消除了时钟失配误差的影响。单一的前置SHA 电路结构如图5 所示。采用该电路只需要一个SHA,降低了硬件复杂度,但是需要控制系统工作频率,且有带宽和通道数限制,不利于提高TIADC 采样率。该结构一般只用于精度为10~12 位,工作在较低频率的逐次逼近型(SAR)ADC,用来实现性能和功耗的折中。

图5 单一的前置SHA 分时交替ADC 结构示意图Fig.5 Single pre-SHA TIADC structure

早期的模拟域校准一般通过设计高精度的分相时钟来实现时钟信号的均匀分布。文献[35]设计了一个具有低时钟偏斜和低抖动的分相时钟,但是在不同的时钟相位之间实现低时钟偏斜仍然是一个挑战。分相时钟通常基于环形振荡器的锁相环(PLL)或基于延迟线的延迟锁相环(DLL)来实现。文献[36-37]介绍了关于低抖动PLL/DLL 时钟发生器的设计,其设计核心正是环形振荡器或延迟线。文献[38]改进了分相时钟的设计,在每个通道的主延迟单元和输出路径之间插入一个额外的延迟单元。利用延时比较器来感知延迟,并通过电荷泵建立各种控制电压Vctrli,校准所用的电荷泵为简单的电流转向结构。主回路采用全局控制电压Vctrl控制粗延时设置,各通道延时由Vctrli独立微调。这种改进的时钟发生器结构,能够将50 ps 以上的时钟偏斜减小到大约10 ps 或更小,实现了低抖动、低偏斜的设计目标。

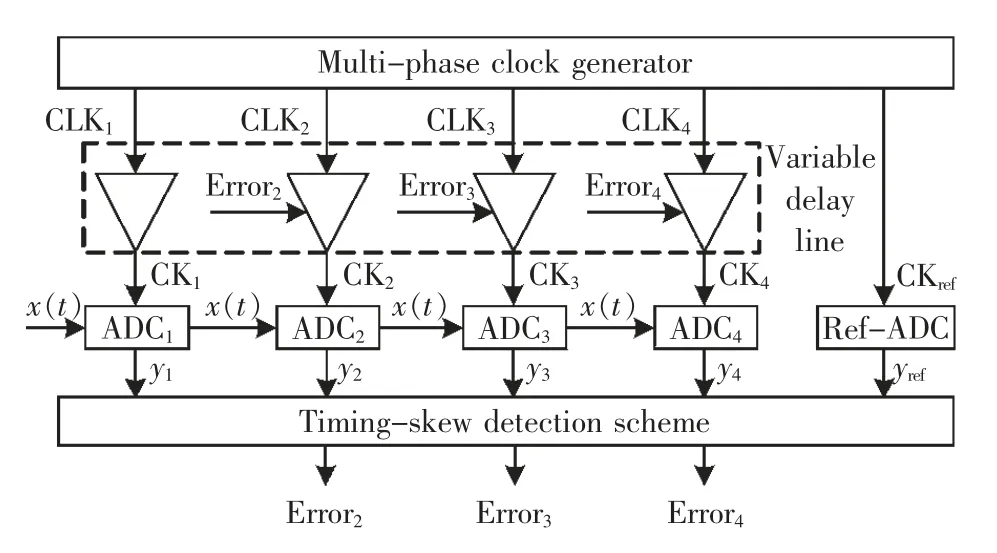

2)数模混合域校准 数模混合域校准即在数字域完成失配误差的估计,再将误差值返回设计好的模拟校准电路来完成校准[39]。数模混合域校准方法通常使用数控延迟单元(digital control delay element,DCDE)来实现[40]。其基本思想是先在数字域测得电路中的时间误差,再在模拟域中利用DCDE 来实现分相时钟的调整,从而完成误差校准,如图6所示。文献[39]通过调节ADC 中的DCDE 来调节采样时钟的相位,实现时钟误差的校准。文献[19,41]是通过调整数控延迟线来微调每个ADC 通道的时钟相位,从而校准时钟误差,但是该方法容易受到电压、器件老化等因素的影响。针对时钟偏斜,文献[42]提出一种改进的基于电荷泵的时钟误差校正方法。该方法复杂度低,不需要任何附加校准信号,利用电容式电荷泵检测任意两个相邻交替通道的时钟偏斜,并且这种时钟偏斜误差可以通过数控延迟器件最小化。以上校准方法要求系统中必须有可以精确控制时钟相位的调节电路。

图6 使用数控延迟器件的TIADC 校准结构示意图Fig.6 Calibration structure of TIADC using DCDEs

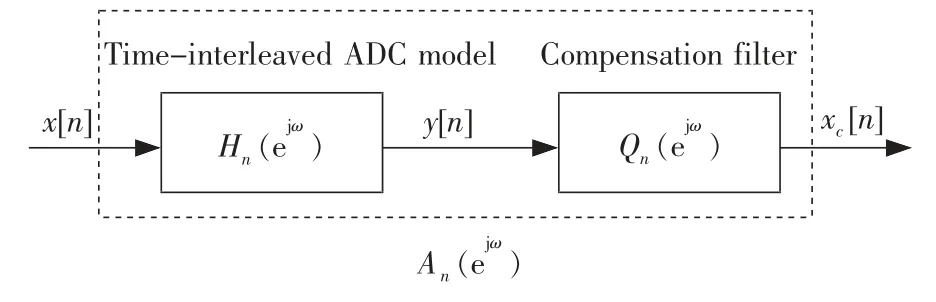

3)数字域校准 由于前台校准的缺陷,越来越多的学者将研究重点投向了数字域后台校准。时间误差后台校准不是直接改善时钟源,而是通过数字信号处理技术对带有时间误差的输出进行补偿校准。基于滤波器组[13,43-44]的后台校准方法是目前的研究热点之一,其原理是将时间误差的校准等效为滤波器的设计,利用滤波器的延迟特性来补偿数字域中的时间失配[45],原理图如图7 所示。图中Hn(ejω)为TIADC 等效滤波器组,Qn(ejω)为补偿滤波器组。

图7 TIADC 时间误差的数字滤波器校准方法Fig.7 Calibration method of a digital filter for time error of TIADC

器件老化、电压不稳定、环境变化等因素会导致时间失配发生变化,这种情况下校准滤波器的补偿系数需要重新设计。为此,有学者提出了信号误差重构[46-49]的自适应校准方法,文献[48]利用Hadamard 变换来重构误差信号,通过补偿的TIADC输出和伪混叠信号之间的互相关来估算时间误差,从而完成时钟偏斜的校准。该方法校准精度较好,其时序误差系数在30 000 个样本后收敛,缺点是消耗较多的资源。文献[49]利用离散微分器对多通道输出进行误差重构,该方法优点是低频信号校准良好,缺点是不适用于高频校准。然而片上实时重新设计复杂的滤波器极其困难且成本高昂[50]。为了避免这种情况,同时让信号重构自适应地跟踪误差变化,文献[51-53]提出了基于分数延迟滤波器组的修正方法。该方法优点是只需要调整校准滤波器的1个系数即可完成校准;缺点是需要对信号过采样,限制了ADC 的工作速度,从而违背了TIADC 技术的初衷。改进的滤波器结构的自适应校准方法还有基于时变滤波器[54-55]和基于Farrow 结构的分数延迟滤波器[45,56-58]。文献[54]需要一个存放滤波器系数的查找表(look up table,LUT),需要耗费大量存储器资源。基于Farrow 结构的分数延迟滤波器优化了传统的时延滤波器,将检测到的时间误差值作为输入送至滤波器,这种结构的好处是当失配发生变化无需重新设计滤波器的系数,也避免了使用LUT。此外该滤波器阶数不超过5 阶,降低了运算复杂度。

Split-ADC 是一种有效的数字后台校准方法[59-61]。Split-ADC 采用分裂结构来实现完整ADC 的功能,分时交替Split-ADC 结构框图如图8(a)所示。将每个子ADC 分割成一半大小的A 和B 两部分ADC并互为参考,Φi为第i 个子ADC 的输入时钟,每个ADC 的A 和B 输入相同,输出为ya和yb。图8(b)为split-ADC 的简化时序图,ΔTi指分割每部分的采样时间差,是由采样开关和时钟缓冲器之间的定时不匹配引入的。相较于整体结构的ADC,采用split-ADC 并不改变ADC 系统在电路功耗、带宽、噪声、面积等方面的性能,对模拟电路设计复杂程度带来的影响也较小,同时具有算法结构简单的优点,缺点是适用于低频校准、高频校准效果差。

图8 Split-ADC 结构框图和简化时序图Fig.8 Block diagram of the Split-ADC and the simplified Split-ADC timing diagram

在最新的研究中发现,利用信号的(一阶或二阶)统计特性进行误差估计,采用函数近似理论的结构进行时间误差校准是一种较为出色的方法。文献[62]提出一种基于一阶统计的方法,首先利用泰勒级数近似,将时间误差建模为加性误差,然后利用通道中信号的一些有价值的特性来简化计算。在此基础上,应用了一种减小稳态误差的可变步长迭代技术,最后通过加法器、乘法器和固定系数的多相FIR 滤波器实现校准。该方法能够在三步迭代内精确收敛,对于12 位TIADC 系统,校准精度达到11.2 位,具有复杂度低、计算效率高、校准快速精确的优点,缺点是只适用于广域平稳输入信号。文献[63]采用一种改进的基于统计的方法,利用校准ADC 与各通道子ADC 之间的互相关来检测并校准时间误差,其中校准ADC 采用的是一个特定频率的时钟控制冗余ADC。校准后,时间误差从最大值18.0 ps 减小到0.8 ps 左右。该方法与传统的基于统计的算法相比,校准通道的输出在数据处理期间被延迟,故不易受到量化噪声的影响,并且具有不增加数据存储量的优点,可以推广到4 通道以上的TIADC 系统,缺点是适用于低分辨率系统。文献[64]提出一种基于二阶统计的方法,利用低复杂度采样序列干预技术,通过处理一组相关器的输出来联合估计所有时间误差值,然后对数字校准电路的要求进行定量研究,并设计数字滤波器实现校准。该方法克服了盲估计的局限性,具有鲁棒性高、功耗低的优点,并且没有通道数限制,缺点是仅适用于SAR ADC。

此外,已发表的时间误差数字域校准方法还有盲适应校准法[65-68]、基于插值的校准方法[69-71]等,基于这些方法进行校准后,TIADC 系统性能均得到了一定的改善。以上所述3 类时间误差校准技术的优缺点比较如表3 所示。

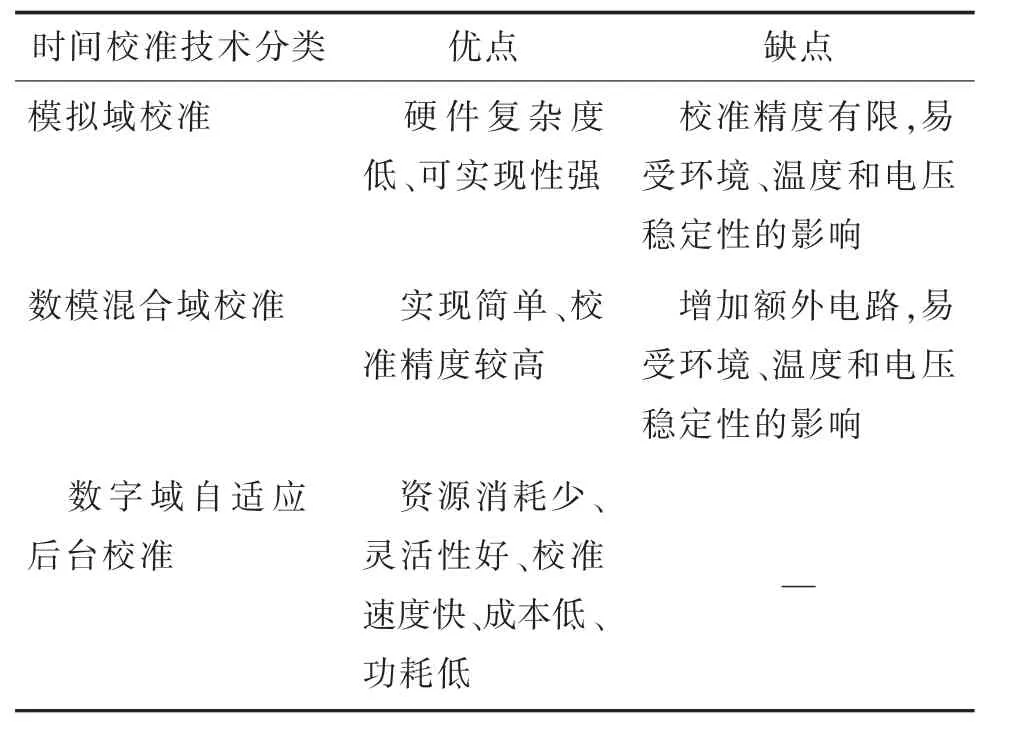

表3 时间误差校准技术优缺点Tab.3 Summary of advantages and disadvantages of time error calibration technology

2.4 其他TIADC 通道失配误差校准技术

随着大动态范围模拟输入信号要求的提高,仅有线性失配和时间失配的校准对于要求严格的高分辨率TIADC 系统的性能提升能力有限,因此,针对带宽及非线性失配的校准方法研究不可避免。目前,有关这两个方面的研究成果非常少,针对带宽失配的校准大都只是在针对模拟前端的SHA 电路进行校准。文献[72]采用前端SHA 以整体采样率对输入进行采样;还有一种方法是增加SHA 带宽,使其远远大于需数字化的最大输入频率,但是不适用于输入包含高频噪声的情况。文献[73]基于一阶SHA模型,利用滤波器设计实现了双通道TIADC 系统的带宽失配数字校准。该方法首先估算SHA 带宽失配的影响,通过对增益系数滤波器进行仿真并根据晶体管和电容器失配数据估算SHA 的时间失配常数τ=RonC,然后根据ADC 的性能来确定校正滤波器的复杂性。最后,将FIR 滤波器F1(z)和F2(z)插入通道路径中进行带宽失配校正,目的是补偿各通道SHA 引入的滤波效果,并消除杂散分量。

TIADC 系统中存在的非线性失配,主要包括积分非线性(INL)和微分非线性(DNL)[74]。直到2004年,Vogel 和Kubin[75]发表了第一篇分析TIADC 非线性失配的文章,解释了非线性失配的主要特征,扩展了线性混合滤波器组的理论,并提出了一种冗余TIADC 阵列的随机化策略。2008 年,Asami 等[76]对TIADC 的非线性效应进行建模,并补偿了ADC的INL。2009 年,Goodman 等[77]基于多相非线性量化研究了校准TIADC 非线性失配。文献[78]通过正弦拟合技术提取出了每个通道的误差,并将误差通过LMS 算法自适应地更新线性组合权重,实现流水线ADC 的非线性校准,缺点是需要较大的存储空间来处理大量样本。2019 年,Salib 等[79]提出了一种查找表的前台校准方法,用于校正无记忆的非线性失配,在此期间有关研究甚少。

研究针对带宽失配及非线性失配的数字校准技术具有重要意义,也必然成为未来TIADC 通道失配校准技术的研究热点。

3 TIADC 校准技术评估与分析

3.1 评估准则

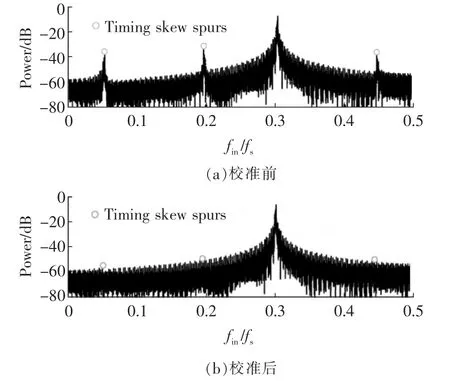

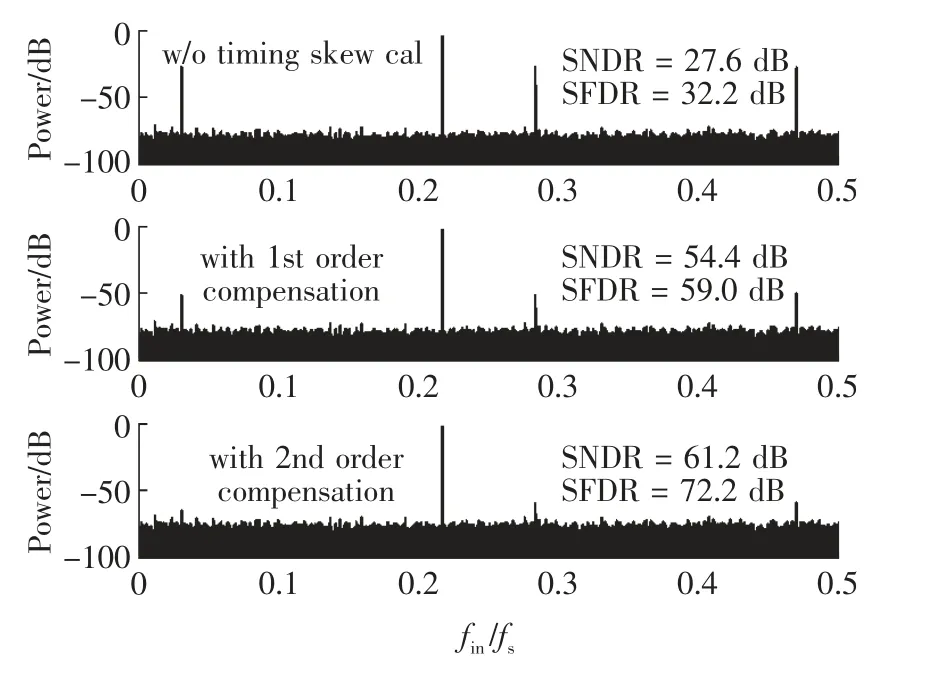

衡量TIADC 系统的性能主要采用以下的度量准则:信噪比(signal noise ratio,SNR)、信噪失真比(signal to noise and distortion ratio,SNDR)、无杂散动态范围(spurious-free dynamic range,SFDR)、有 效量化位数(effective number of bits,ENOB)。SNDR和SFDR 这两个关键的指标在数据传输、医疗设备、军事通信和电子对抗及移动通信和无线通信等领域应用广泛,ENOB 更多应用在数字滤波器和频谱分析中,其数值由SNDR 决定。实际的TIADC 系统受到通道失配的影响,在输入信号上产生谐波,从而导致度量值下降。因此,提高SNR/SNDR 和SFDR的能力可以直接度量校准算法的性能。以文献[80]为例,采用带Lagrange 插值的二阶补偿方法最小化时间误差,校准前后输入信号的输出频谱如图9 所示。可以发现,在校准后,时钟偏斜杂散得到显著抑制。校准前后计算得到的SNDR 和SFDR 信息如图10 所示。可以发现,通过传统的一阶补偿校准的方法,将SNDR 和SFDR 分别提高到54.4 和59 dB,利用文献[80]的二阶补偿校准的方法将SNDR 和SFDR 分别提高到61.2 和72.2 dB。当时序偏斜相对较大时,二阶校准的方法性能较好,且比一阶校准方法更优。

图9 输入信号的输出频谱[80]Fig.9 Output spectra of the input signal[80]

图10 时钟偏斜校准前后的输出频谱[80]Fig.10 Output spectra before and after timing skew calibration[80]

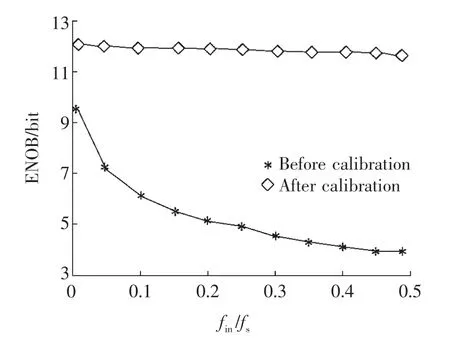

当信号的输入频率变化时,校准算法能否保持校准能力,是评判算法性能的关键。以文献[81]为例,当输入频率变化时该方法的校准效果如图11所示,结果表明,该方法适用于整个Nyquist 频率内的校准,且在高频输入时,校准效果明显。因此,该校准方法性能较优。

图11 输入频率变化时该方法的校准效果[81]Fig.11 Calibration effect of the method when the input frequency changes[81]

除此之外,校准算法的时间、精度、复杂度、可靠性、成本等也都是重要的评估准则。

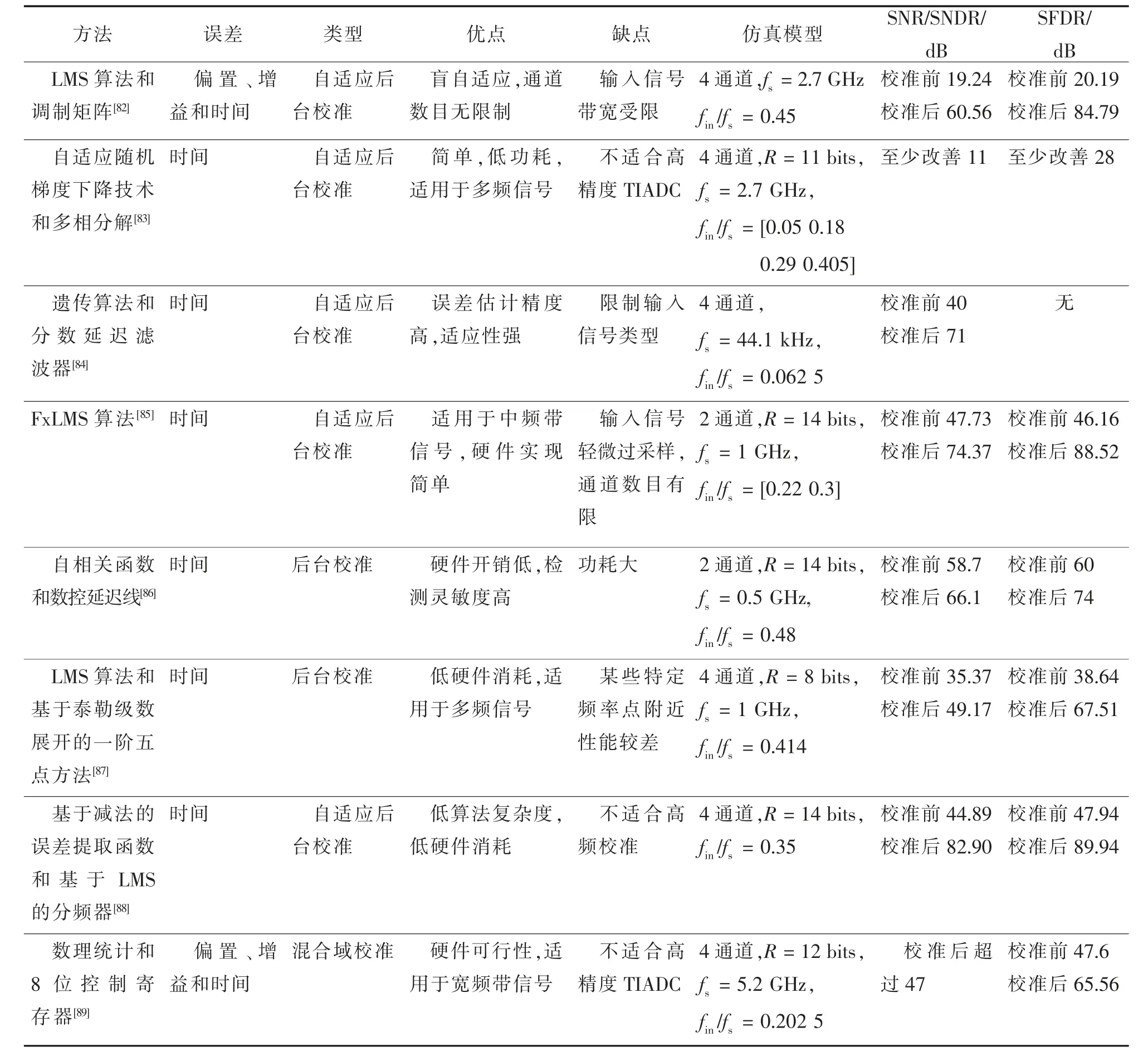

3.2 对比分析

选取并归纳了近几年性能较优的TIADC 通道失配校准方法(部分),如表4 所示。其中,R 表示采样精度,fs表示采样率,fin表示输入信号频率,fin/fs表示归一化频率。经对比可知,目前,全数字校准是TIADC 通道失配校准技术的研究大方向,时间误差是校准技术最主要的研究对象,将后台校准技术与自适应校准技术相结合是最主要的研究手段之一。

表4 近几年TIADC 通道失配校准方法对比Tab.4 Comparison of TIADC channel mismatch calibration methods in recent years

在算法对比和数据分析研究的基础上,提出以下两个关键问题:第一,目前的校准方法虽然能大幅提高TIADC 性能,但有些算法对于高精度的TIADC(12 bits 以上)校准效果欠佳,且对于超高分辨率TIADC 系统(16 bits 以上),算法适用性尚未得到验证,在校准能力上存在瓶颈;第二,许多校准算法只是在Nyquist 频段内某些频点或某一段频带上表现出优异的性能,导致算法对于输入信号的应用范围受到严格限制。

4 结论与展望

分时交替采样技术是目前实现高速高精度ADC 最有效的方法之一,而TIADC 通道失配校准技术的涌现为这项技术从理论构想到投入市场应用带来了发展机遇。但是由于技术和条件等多方面的限制,TIADC 通道失配校准技术目前还存在诸多不足,主要表现在几个方面:1)有的校准方法不具备自适应跟踪误差变化的校准能力,甚至还会受通道数限制;2)很多校准算法受输入信号的限制,有的只适用于窄带信号,有的依赖于正弦信号,不具普遍适用性,然而在实际中,宽带信号及多频率混合信号应用广泛;3)校准方法在提升TIADC 系统性能上遇到瓶颈,对于高分辨率大动态范围的TIADC系统应用难度很大;4)目前所做的研究大多是针对时间误差校准,对于带宽失配及非线性失配的研究较少;5)一些数字校准算法在提高系统性能的同时仍存在计算复杂、资源浪费、硬件实现困难等缺陷,未能兼顾性能和成本。

针对以上问题,为了更好地提高TIADC 系统性能,未来可以建立更加精确的TIADC 通道失配模型进行研究,模型的改进主要有:1)将线性失配和非线性失配同时加入到失配模型当中;2)将TIADC 的失配与通信中的信道模型相结合,利用信道校准技术校正系统的内部失配;3)使用任意的输入信号;4)扩展TIADC 系统采样通道数量(4 通道以上)。对于非线性失配误差的校准,提出以下几点预测:1)将TIADC 问题和非线性问题结合起来,采用基于Hybrid Volterra 级数的行为模型进行误差建模;2)采用如压缩感知的方法来选择Volterra 级数的系数;3)使用NARMAX 非线性模型,进一步考虑系统的反馈;4)采用神经网络进行误差校正。对于带宽失配误差的校准,可以通过获取各通道的频响,设计一种改进的自适应校准方法来实现。对于宽带输入信号数字校准技术的研究,将以拓宽信号带宽为目标,可以加入Hilbert 滤波器,实现工作在Nyquist 频段外输入信号的有效校准。对于低功耗、低复杂度和资源优化的高性能校准系统的研究,需要保证其工作在较低的频率,可以通过模块化的算法设计来实现。以上的研究有助于研发具有更高分辨率及采样率的TIADC 系统,同时使系统具有扩展性和稳定性。