基于FPGA+DSP的弹载组合导航系统设计∗

李炳臻,李 杰∗,胡陈君,张泽宇,纪志敏

(1.中北大学电子测试技术重点实验室,山西 太原 030051;2.苏州中盛纳米科技有限公司,江苏 苏州 215123)

随着现代战争对于常规战术武器要求的进一步提升,常规武器弹药的“信息化、制导化”已经越来越作为新设计趋势。因此,实现低成本高精度的导航作战平台将愈来愈重要[1]。

传统的常规战术武器的导航系统,其导航方式为单一的惯性导航,虽然惯性导航方式具有不需要与外界有任何信息交互,也不与外界进行能量交换,高度隐蔽和高度自主的特点,但是由于传感器和算法自身难以规避的缺点,其导航精度随解算时间的累加会将计算误差不断放大,无法提供长时间的可靠导航计算[2]。

随着GPS 卫星导航相关理论的完善和应用的扩大,SINS/GPS 这种新型的组合导航系统得到广泛的应用,它弥补了传统的惯性导航计算误差随时间积累的问题,也解决了卫星导航系统在高动态环境中定位经常失锁的问题,提高了导航系统的更新速率、导航精度和抗干扰能力[3]。

本文针对目前常规武器制导化的趋势,设计了一种新的弹载组合导航系统,它可以完成对前端模拟信号(IMU 惯性单元)和数字信号(GPS 定位信息)的采集,同时拥有强大的导航解算能力,体积小,速度快,计算能力强,能够较为准确地算出弹体位置和姿态信息,可以在较为复杂的弹载环境下使用,满足大多数常规武器的作战需求[4-6]。

1 系统总体设计

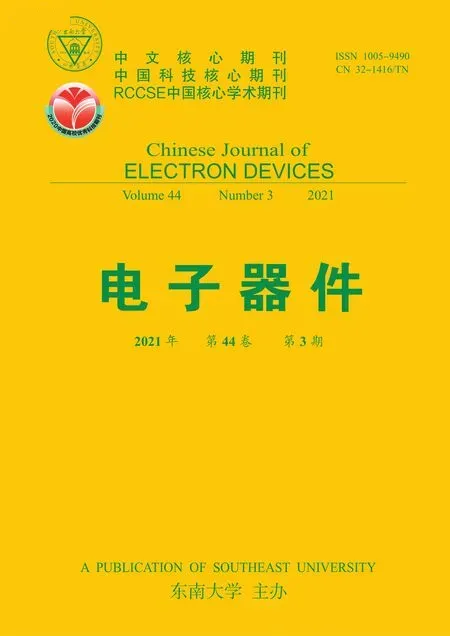

组合导航系统平台硬件设计采用“FPGA+DSP”的方案,即以FPGA 作为核心控制器,DSP 为解算模块,包含电源模块、信号调理模块、A/D 转换模块,数据存储模块等组成,系统总体结构见图1。

图1 系统总体结构

组合导航系统硬件平台的工作流程为,主控模块FPGA,通过控制A/D 转换器等完成前端模拟和数字信号的采集,将数据编帧预处理后,传给DSP数据解算模块,由DSP 模块对前端采集的数据按照组合导航算法,进行解算,对IMU 惯性数据和GPS定位信息进行组合导航后,再将解算后的数据信息回传给FPGA 主控模块,在FPGA 将数据存储的同时,将得到的部分关键姿态信息传送给遥测模块,由遥测模块将数据发送给控制大厅。

2 硬件电路设计

2.1 电源模块

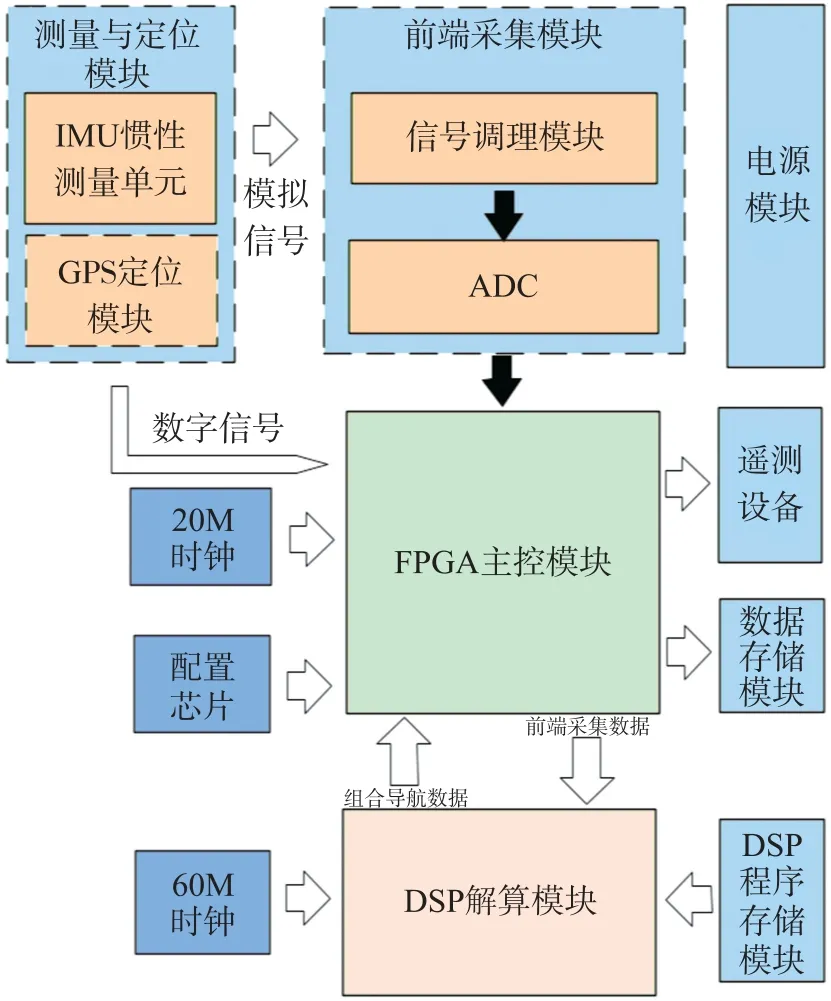

组合导航平台采取自供电的方式,采用16.8 V锂电池供电,通过TI 公司的LTM8022 稳压芯片,将16.8 V 电压降压为稳定的5 V 电压后供其他模块使用。同时,考虑到工作环境的特殊性,为对抗复杂环境下的电磁干扰,保障前端数据采集电路的采集精度,供电模块部分将数字电源和模拟电源隔离,16.8 V 转5 V 电路见图2。

图2 16.8 V 转5 V 电路

由于其他模块的供电要求,需要电源模块提供1.2 V 与3.3 V 的电压,选择TI 公司的TPS70345 型芯片,同时考虑到 DSP 芯片采用的是TMS320C6748,其上电有顺序有严格的要求,上电顺序必须依次为1.2 V-1.8 V-3.3 V 的顺序,所以在FPGA 上电工作后,通过控制TI 公司的LP5907-1.8和LP5907-3.3 来满足DSP 的上电要求,主控芯片电路图见图3。

图3 主控芯片供电电路

2.2 模拟信号采集模块

组合导航平台前端采集电路采集数据来自IMU惯性测量单元的加速度计信息,将其输出的模拟电压值转换为数字信号。

模拟信号采集模块是由信号调理模块和A/D转换器组成,信号调理模块是将输入的电压信号进行滤波,放大,增加其驱动能力,使得采集更为精确;A/D 转换模块则是直接将模拟量转换为数字量,因此它直接决定了组合导航计算的精确度。

信号调理模块采用TI 公司的OPA4340 型信号调理芯片,具有宽带宽增益和高输入阻抗的特性,拥有非常良好的直流特性,可以有效降低前端模拟信号传输过程中的损耗,确保其驱动能力,可以对惯性传感器输出电压0.5 V~4.5 V 进行信号调理。

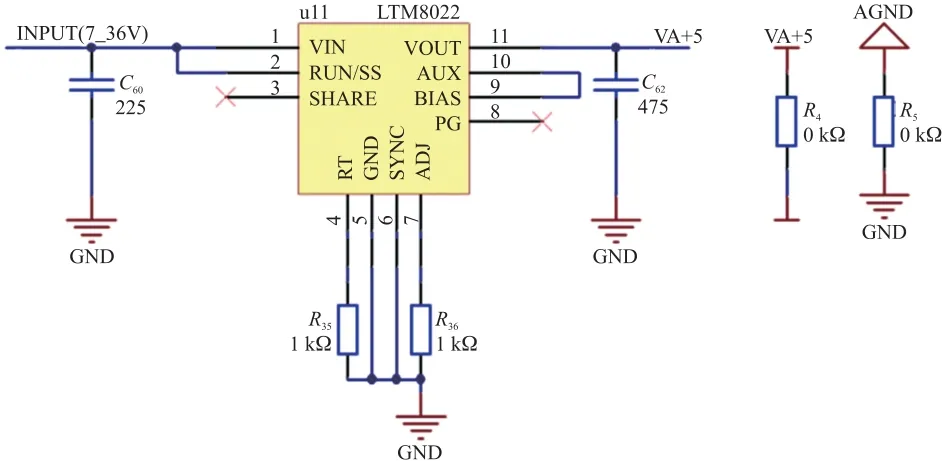

A/D 转换模块选用TI 公司的ADS8365 型芯片,该芯片支持六路采集,拥有16 位的采样精度,最高允许5 MHz 的时钟输入,每个通道的转换时间仅为4 μs,转换后的数字信号可以进行高速并行传输,完全能够满足导航系统对前端传感器的采集要求。A/D 转换器电路设计见图4。

图4 A/D 转换器电路设计

2.3 数字电路采集模块

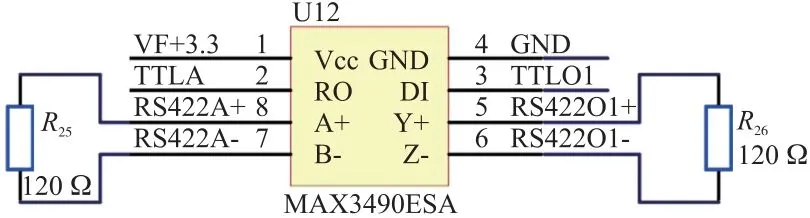

来自GPS 导航系统的定位信息为数字信号,在可能存在较强电磁干扰的环境下,其传输方式为差分串型传输,采用固定波特率,接口电平标准为RS-422 电平,而FPGA 的端口为TTL 电平标准,需要设计转换差分转单端电平的电路,完成电平转换。

电平转换芯片采用MAX3490,该型号芯片支持同时进行422 信号的输入输出,通道间相互隔离,电路设计见图5。

图5 电平转换电路

2.4 FPGA 主控模块

组合导航系统除了控制前端采集电路,还要对采集回来的数据做预处理,编帧,传输,存储等较为复杂的操作,因此核心处理器必须具有较为强大的功能,经过综合考虑,选择赛灵思公司的XC6SLX16-CSG324 芯片芯片作为主控芯片。

该芯片体积小,功耗低,价格相对较为便宜,可批量生产,支持多种接口协议,配合HDL 语言进行开发,完全满足作为组合导航系统主控模块的设计需求;XC6SLX16-CSG324 拥有丰富的硬件资源,有232 个I/O 端口、2 278 个SLICE 资源、14 579 个逻辑单元、576 KB 的缓存,拥有十分优良的硬件性能。

2.5 DSP 解算模块

虽然FPGA 拥有非常丰富的逻辑资源,但是组合导航的运算量极大,如果单纯靠FPGA 内部硬件资源搭建,计算速度和资源占用率都无法满足设计要求,因此拥有丰富乘法器资源的DSP 成为数据解算模块的最佳选择。

考虑到设计要求的实时性、小型化、低成本、工作环境等因素,DSP 芯片选择 TI 公司的TMS320C6748 型芯片,其主频率高达375 MHz,,可同时执行8 条指令,完全满足计算需求以及在弹载环境下工作。

并且该型号DSP 拥有一个通用并行接口,可用来与其他设备并行传输通信,并且该接口的控制信号少,并行通道UPP 的工作时钟是其主频(375 MHz)的四分之一,满足数据传输需求,因此本文用它来做数据解算模块,实现与FPGA 进行数据通信。

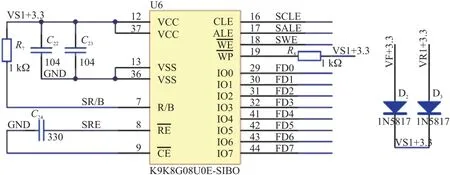

2.6 存储模块

在设计中,存储模块有两部分,一部分用作DSP回传解算后的数据存储芯片,另一部分是DSP 程序以及相应组合导航诸元的程序存储模块。因此,数据存储必须使用下电不丢失,长期工作稳定类型的存储芯片。

组合导航系统解算数据量大,更新快,导航周期短,所以必须快速写入存储器,不能有丢帧少数据的情况。因此,数据存储模块和程序存储模块均选用三星公司的K9K8GU0M 型NANDFLASH 作为存储器,其页编程时间仅仅200 μs,写入时间远远小于DSP 内置算法的计算周期,完全满足解算需求,存储模块电路图见图6。

图6 存储模块电路图

3 系统程序设计

3.1 A/D 数据采样模块

系统通过FPGA 控制AD8365 完成对模拟信号的采集。采集系统上电后,给A/D 芯片复位信号,完成系统的同步初始化。然后由FPGA 控制模块,对AD8365 发出指令HLODX,其为低电平触发。收到指令的AD8365 开始对输入的六路输入电压信息进行一次转换,A/D 转换完成后,A/D 内部下拉EOC 引脚,提示主控芯片完成转换[13]。

FPGA 收到AD8365 的提示信号后,FPGA 发送RD 指令,完成转换数据的读取,完成一次完整的数据转换过程。AD8365 工作时序,见图7。

图7 AD8365 工作时序图

3.2 前端采集信息处理

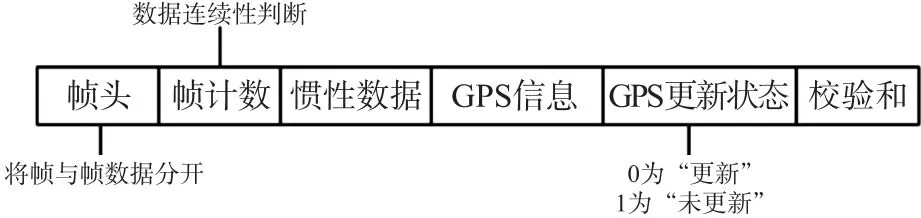

前端采集数据,既有相对频率较高的惯性传感器数据,又有更新速度较慢的GPS 定位信息。因此,必须采用合理的方式,将速度不同的数据信息进行处理后传输[7]。

考虑到后端DSP 处理的要求,系统采用编帧的方式,即在FPGA 内部对所有的前端采集数据进行数据编帧预处理,以更新频率较高的惯性数据为基础频率,同时也将收到的GPS 数据编帧,在GPS 数据后增加标志位作为更新标志字,“0”为更新,“1”为未更新。

在每一帧数据的前面增加帧头“EB90”作为区分不同帧的标志,每一帧帧头后添加累加的帧计数作为连续性判断标志,同时为了防止在FPGA 和DSP 数据传输过程中发生数据丢失或者数据失真的情况,在每一帧数据的结尾增加数据校验和,即前面所有有效的数据累加和的低八位。这样,该帧数据进入DSP 后,DSP 可以通过对校验和对接收数据进行判断,确保接收数据的准确性和解算精度,编帧格式见图8。

图8 编帧格式

当FPGA 将数据传输给DSP 后,DSP 把根据上一帧惯性数据和GPS 定位数据通过组合导航算法得到的组合导航解算信息加在该帧后面,回传给FPGA。接着,对刚得到的这一帧数据做解算,完成一次完整的数据传输,使FPGA 不仅可以得到完整的传感器的原始数据,还可以得到导航解算姿态信息,将其存储到Nandflsh 中[8-10]。

3.3 FPGA 与DSP 数据通信接口设计

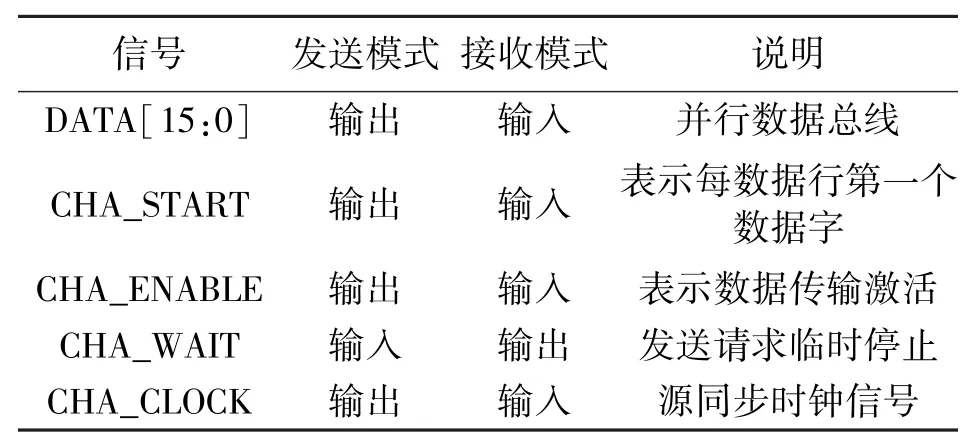

DSP 与FPGA 的数据传输是通过DSP 内置专门的并行端口UPP 来对外完成并行高速数据的传输,其拥有独立的数据缓存通道来缓存外部的传输数据。UPP 有两个独立的通道,为通道A,通道B,并且只有数量极少的控制线,配置灵活,支持SDR(单倍数据率),DDR(双倍数据率),UPP 通道信号说明见表1。

表1 UPP 通道信号说明

系统采用A 通道作为DSP 的并行数据接收通道,其时钟是由FPGA 提供。用通道B 作为DSP 的输出通道,输出DSP 解算后的数据,时钟由DSP 内部提供。通道A 和通道B,均为8 位,且都通过UPP接口内部的DMA 缓存区,传输过程见图9。

图9 FPGA 与DSP 通信示意图

为保证数据发送的连续性,解决不同芯片间的跨时钟域传播问题,在FPGA 主控模块内部设计两个独立的FIFO,数据发送FIFO 接收经过编帧后的数据,数据接收FIFO 接收DSP 导航解算信息。当数据发送FIFO 接收的数据到达一定的阈值后,FPGA 的发送模块开始发送数据给DSP 的通道A,同时给DSP 一个高电平信号,直到该帧数据发送结束。当导航解算完成后,DSP 通过通道B 发送数据给FPGA,通道A 和通道B 之间相互独立,这样数据的发送和接收不受影响,整个数据传输系统达到动态平衡。

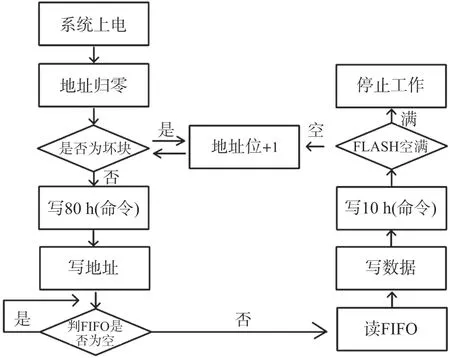

3.4 数据存储设计

数据存储模块是由FPGA 主控模块完成写操作,将DSP 回传的数据信息全部存储,方便事后对弹体的姿态位置信息进行分析处理。

组合导航解算后的姿态信息从UPP 接口回到FPGA 内部后,进入FIFO 中缓存,再由FLASH 写入程序从FIFO 中读出,存入FLASH 中,因为该型号FLASH 的页编程时间远远小于解算数据的时间,所以FLASH 控制器读FIFO 时钟的速度远远大于DSP给的写入时钟,保持了动态平衡,维持了数据的稳定[11-12]。

在该型号FLASH 上弹使用前,需进行相应的坏块检测,确保存储器的每一个数据块的工作状态,将其坏块信息写入程序中,当写入时先判断写入地址的坏块情况,再写入该地址,系统上电后,FLASH 工作流程见图10。

图10 存储模块工作流程

4 试验结果

弹载组合导航系统硬件平台的方案可行性验证是通过制造出实物后,将实物直接连接前端的IMU惯性测量装置,以及GPS 卫星导航板卡,得到相应数据信息,进行验证的。

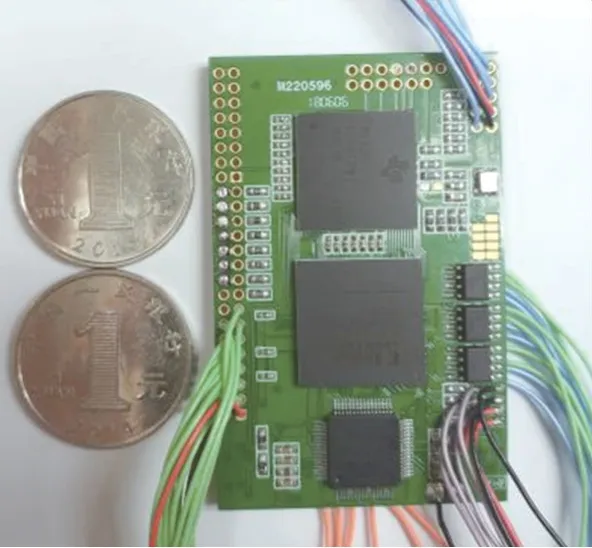

整个组合导航系统板卡采用六层PCB 布板,这大大提升了器件的布板效率,提升了板卡的性能,缩小了版卡面积,最后实际布板面积为62 mm×40 mm,实际板卡设计见图11。

图11 组合导航板卡实物图

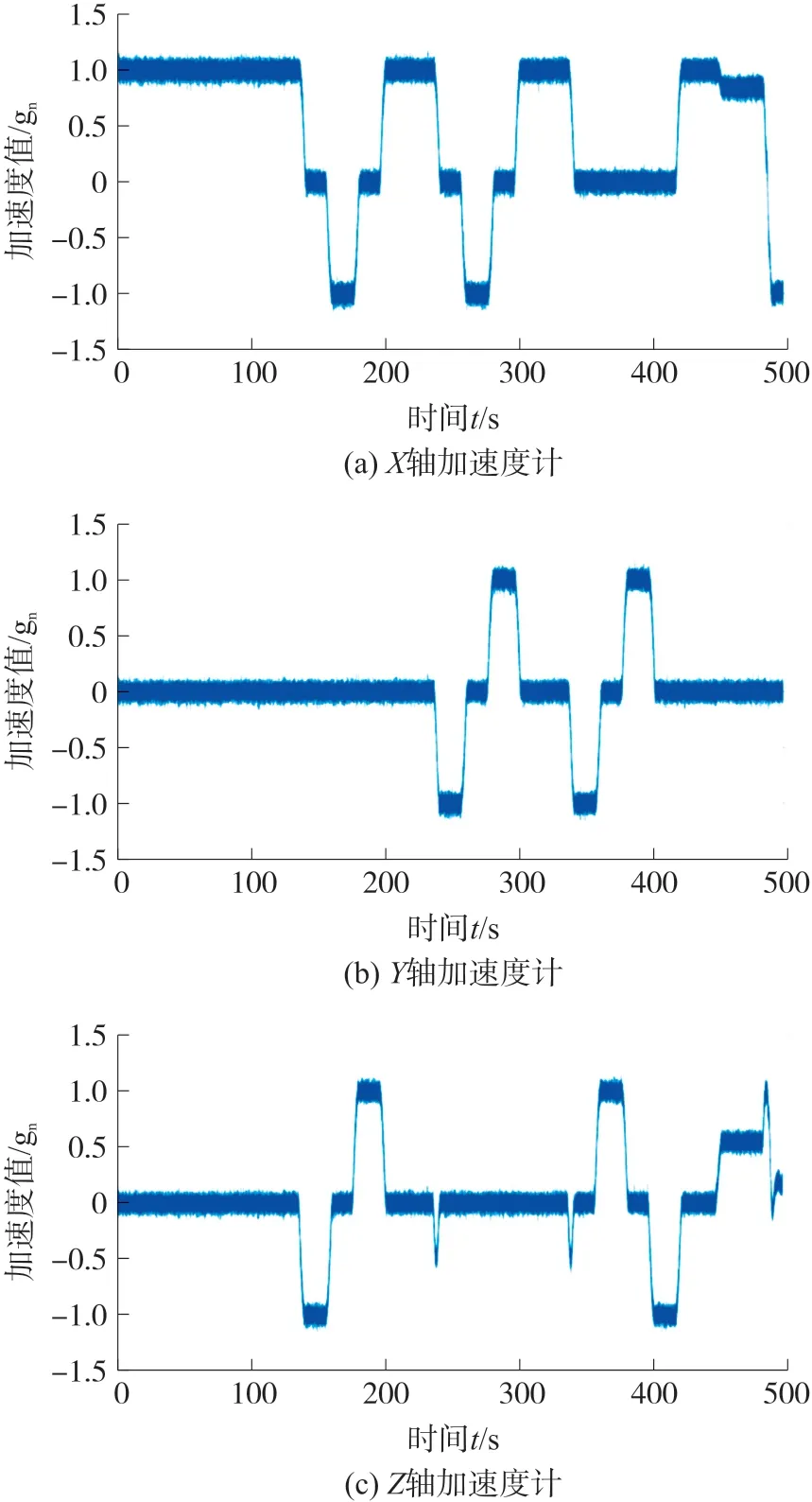

组合导航算法融合了惯性导航算法和卫星导航算法,因此,为保证其精度,首先需要对惯性传感器进行标定,得到相应的加速度计和陀螺零位,以及标度因数,通过三轴转台对加速度计标定后得到的结果,见图12。

图12 三轴加速度计标定后结果

为确保GPS 信号质量,使其保持自然收星状态,实物测试是在室外进行,系统上电后,如果正常工作,会将相关数据按照编帧格式存储在系统存储模块中。系统下电后,将配套的读数盒连接到存储模块,然后通过计算机内置上位机,读出数据信息,判断数据情况。

经过室外静态采集数据后,通过上位机按照事先定义好的编帧信息,将数据分离,从而得到的惯组陀螺仪数据Y轴信息,惯性组件整体处于静止状态,陀螺仪的整体输出在零位附近,这说明惯性数据采集正常,陀螺仪Y轴数据见图13。

图13 陀螺仪Y 轴数据

数据解算分离后,得到GPS 初始定位信息,以及组合导航解算后的相应姿态位置信息,GPS 定位高程与DSP 内部进行组合导航解算高程对比结果,见图14。

图14 GPS 定位数值与组合导航解算高程对比图

数据测量地点在西昌,测量所在地海拔在1 795 m,经过数据对比,可以看出,组合导航处理后的数据并没有与GPS 定位数值完全一样,而是围绕GPS 数据波动,这是组合导航算法融合GPS 数据和IMU 惯性数据进行计算的结果。

且为了模拟真实的实验环境,在实验中不断中断GPS 信号,让GPS 模块重新定位,完成信号失锁重补的过程,模拟弹上可能出现的环境。通过表2可以看出,在400s 内的上电过程中,定位高程与当地实际高程的误差精度绝对值最大在3%以内,满足设计要求。完全可以保证设备在弹载环境下,即便无法收到稳定的GPS 定位信息,也可以在短期内根据纯惯性算法完成可靠的数据解算。

表2 GPS 定位数值与组合导航计算高程与实际高程对比

基于以上组合导航系统硬件平台的室外实际上电测试,其数据采集前端工作正常,组合导航解算模块工作正常,FPGA 与DSP 之间数据传输稳定,DSP解算功能正常,数据存储模块功能正常。

5 结论

本文针对弹载环境下的组合导航硬件平台进行详细的介绍,该平台可以在高过载环境下,满足小体积、大容量、高速度的要求。通过FPGA 对前端数据采集模块的控制,以及与DSP 解算模块的并行数据通信,完成了采集和解算数据的存储,为弹体姿态和定位信息的后期理论分析,提供了非常可靠的数据保障。同时,该系统具有很强的移植性,除了弹载环境,还可广泛用于商业航天,深海探测等极端环境下的数据采集以及姿态计算。