基于FPGA+ARM 异构SOC 技术的sobel 算法实现

王 亚,余 宏,莫章洁,邓 睿

(贵州师范学院物理与电子科学学院,贵州 贵阳 550018)

1.项目研究背景

数字图像处理技术应用十分广泛,其主要是将图像信号转换成数字信号,从而利用计算机对其处理。利用ZYNQ SOC 开发板的FPGA+ARM 架构,重构嵌入式SOC 芯片系统架构体系,结合Sobel 边缘检测算法,设计实现一种灵活且可重构的嵌入式SOC 高速视频图像采集系统平台。通过FPGA 逻辑资源实现较快的计算速度,又可利用ARM 处理器进行多样化设计,可为不同的图像识别类人工智能场景应用提供高速且灵活的数据采集。具有灵活性高、功耗低、体积小、处理速度快等优点。本次设计中,采用友晶(Terasic)公司的MT9P001 图像传感器采集图像数据,将其传输至FPGA 系统平台,再由FPGA 系统平台将图像数据存储至SDRAM 中。与此同时,内部图像处理模块进行sobel边缘检测功能,并最终在TFT显示屏上实时显示。

传统的嵌入系统开发,以固定的单片机系统为主要的处理器核心,利用C 语言在keil 工具下进行软件设计,从而实现应用开发。在本项目的研究中,与传统的嵌入式开发环境有所不同。以数字系统设计为核心,将FPGA 与单片机ARM 系统合为一体,在同一开发软件平台上同时进行软硬件的灵活应用开发,具有很高的灵活性和自主性。所以对异构多核开发框架、流程进行熟悉,核间通信、ARM 与FPGA 通信等开发应用平台进行研究,根据不同的需求更机动灵活地完成嵌入式的应用开发。

图1 系统整体框图

2.边缘检测与Sobel 算法

边缘是图像的基本特征之一,其在图像分析与视觉分析中发挥着重要作用,常用于人们识别物体的有效信息。图像上不同亮度的区域之间的临界就是“边缘”的意思,在两个不同区域的“边缘”处有着许多像素点,这些像素点就组成了不同的坐标。常用的边缘检测法是用图像的灰度值来检测图像的边缘。算法主要计算公式是一阶或者二阶导数。

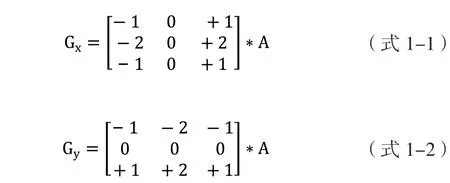

Sobel 算法是一种基于3x3 的矩阵实现的边缘检测算法,是边缘检测常用的重要技术之一,采用离散型计算方法,用差分计算方式计算图像亮度函数灰度的近似值。在边缘检测中,核心关键是图像数据与Sobel 卷积核进行卷积运算,卷积核分为x 方向和y 方向,其中x 方向检测水平边缘,y 方向检测垂直边缘。其算法流程如图所示。

图2 Sobel 算法流程图

图3 3x3A 矩阵

总梯度为:

实际使用中,常化简为绝对值形式:

梯度方向计算公式为:

如此,我们定义一个阈值M,如果G 大于M,则可认为该点是一个边界值,反之,则不是边界值。

3.系统整体设计

本论文中,硬件部分采用Altera 公司的QuartusII 集成开发环境进行硬件设计,软件部分采用Artera 公司开发的SoC EDS 设计软件进行软件设计。SoC FPGA 的硬件设计部分,在QuartusII 集成开发环境下的Qsys 工具中进行,建立一个HPS硬核系统:

创建QuartusII 工程,选择具有ARM 硬核处理器的FPGA器件;

在Tools 中选择Qsys 工具并新建Qsys 工程,在界面中添加HPS 处理器等IP 核,使用file->new component 配置好所需的信号,时序,端口等信息;

所有模块添加完成后,根据信号类型以及自己希望的数据连接定制模块间信号连接:

最后,为外设分配地址映射,以便软件开发中获取设备地址。

基于soC FPGA 的嵌入式软件设计,采用Altera 公司推出的嵌入式系统设计软件soC EDS,由soC EDS 开发套件下的ARM DS-5 开发环境设计视频传输系统。ARM DS-5Debugger可通过USB-Blaster 连接目标开发板并进行在线调试,也可基于ARM 架构处理器的模型进行调试。

4.图像采集模块

视频图像采集是一个视频采集系统的最前端部分,图像数据的优劣性如分辨率,帧率等很大程度上决定着整体系统的性能指标。本次设计图像采集模块采用TRDB-D5M 高清图像传感器,该传感器采用Micron 公司的MT9P001 数字图像传感芯片,为1/2.5 尺寸CMOS 结构感光元件,具有五百万像素。采用40pin 的标准GPIO 母口,能够与Artera 公司与友晶科技公司联合推出的Del-soC 开发板的GPIOO 公口连接[7]。该摄像头采用自动工作模式和可配置工作模式,默认工作模式为可配置工作模式,通过12C 总线设置其内部控制寄存器,对摄像头的分辨率,像素时钟等工作参数进行调节。

TRDB-D5M 图像采集需要在FPGA 中用Verilog 硬件描述语言配置,通过读取时序得到原始图像。每次上电之后,图像传感器通过12C 配置正确参数以正常工作,配置参数通过12C_Controller 模块传递给摄像头控制芯片。图像数据以扫描的方式输出,当LINE_VALID 信号为高时,输出有效图像数据,否则将是0 值。

图4 TRDB-D5B 图像采集模块

5.数据读写控制

数据读写控制选择SDRAM,其型号为HY57V2562GTR,拥有256Mbit 的容量,16bit 总线,地址线采用12 位行列地址设计,非常适合高宽带和大容量的存储设计。在进行实时图像处理中,这一优势至关重要。HY57V2562GTR 还拥有如下特点:

采用标准SDRAM 协议;

接口电压低,输入输出功率损耗降低;

内部有4 个存储阵列,可进行4Bank 操作;

器件所有引脚与LVTTL 接口兼容;

刷新周期8192 次/64ms。

HY57V2562GTR 在工作时,首先需要一个上电初始化过程,其次需要一个200us 的稳定期。不同的SDRAM 稳定期不同,在输入稳定期之后,需要对所有的L-Bank 预充电,使SDRAM内部所有存储器件进入待机状态。预充电结束后,SDARM 内部的刷新计数器会进行8 次刷新操作,不同的SDRAM 刷新次数不同,最后一阶段配置模式寄存器。电初始化过程结束后,我们就能将采集到的图像数据进行读,写,刷新等操作,并最终通过TFT 显示屏实时显示。

图5 SDRAM 存储阵列示意图

6.TFT 图像显示模块

传统的VGA 显示器采用的是模拟信号,而FPGA 输出的是数字信号,若采用VGA 显示器显示,则需要在两者之间加数模转换模块(DAC 模块),这使得设计更加复杂化。同时,由于转换芯片价格一般比较贵,这会造成成本的上升。TFT 显示屏为数字信号显示屏,省略了DAC 模块,为使整体系统设计简单化,我们选用了RGB 接口的TFT 显示屏。TFT 显示屏的扫描方式和VGA 显示屏标准类似,故可按VGA 显示器的设计方法驱动TFT 显示器。

VGA 接口的时序分为行扫描和列扫描,电子束从屏幕左上方开始扫描,从左向右,自上而下。每行扫完后,电子束都回到屏幕下一行左边的起始位置。这期间,CRT 对电子束进行消隐。每行结束时,用行同步信号进行行同步。扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕左上方。同时进行场消隐,预备下一场(帧)的扫描。不同VGA 显示屏之间仅时序参数不一样,可用相同方式进行设计。在设计VGA 驱动代码时,将时序指标进行参数化设计,以便在更换显示屏时省去代码编写的重复性过程,只需更改参数便可完成驱动。

7.检测结果

通过TRDB-D5M 高清摄像头对实物图的数据采集,本设计方案基本实现了sobel 边缘检测,且检测结果正确。实时对数据进行了处理,完成了预期的设计目标。

图6 测试图实物图与显示测试图

8.结语

通过FPGA-ARM 异构系统平台和TRDB-D5M 采集图片数据,以Sobel算子进行边缘检测。采用Verilog硬件设计语言编码,控制TRDB-D5M 采集图片视频流数据,并通过TFT 显示屏进行显示,验证了整体系统的可行性。本设计方案对各个部分进行模块设计,成功实现对视频流数据进行Sobel 边缘检测的实时处理,使开发出性能更高、用途更广泛的处理方法成为可能。