半绝缘碳化硅单晶衬底的研究进展

彭 燕,陈秀芳,谢雪健,徐现刚,胡小波,杨祥龙,于国建,王垚浩

(1.山东大学,晶体材料国家重点实验室,新一代半导体材料研究院,济南 250100;2.广州南砂晶圆半导体技术有限公司,广州 511458)

0 引 言

众所周知,半导体产业发展至今经历了三个阶段:第一代半导体材料以硅为代表,主要应用在以集成电路(IC)为核心的信息电子领域;第二代半导体材料以砷化镓等化合物半导体为代表,主要应用在光电子领域、通信领域;第三代半导体材料的兴起,则是以氮化镓(GaN)薄膜材料的P型掺杂的突破为起点,以高亮度蓝光发光二极管(LED)和蓝光激光器(LD)的研制成功为标志。随着生长技术的发展,第三代半导体材料和应用也越来越广泛。SiC材料就是典型的代表之一。

SiC具有一系列优良的物理化学特性,除了禁带宽度,还具有高击穿电场、高饱和电子速度、高热导率、高电子密度和高迁移率等特点,随着单晶材料的技术突破,这些性质使得SiC成为研究和产业的热点,有力推动了SiC单晶材料的进展。

SiC单晶作为晶体材料国家重点实验室最近二十年的重要研究内容之一,在蒋民华院士的主持下,从零起步,高起点布局,采取跨越式发展思路,攻克了一系列关键技术难关,培养了大批人才,为我国SiC单晶产业及其在核心领域的应用做出了卓越贡献。本文以SiC单晶衬底为主要研究对象,首先简要介绍其基本性质、研发历史和制备方法,并结合晶体材料国家重点实验室的半绝缘SiC衬底相关研究工作概述研究、产业现状和面临的挑战,最后对国产SiC单晶衬底的发展进行了展望。

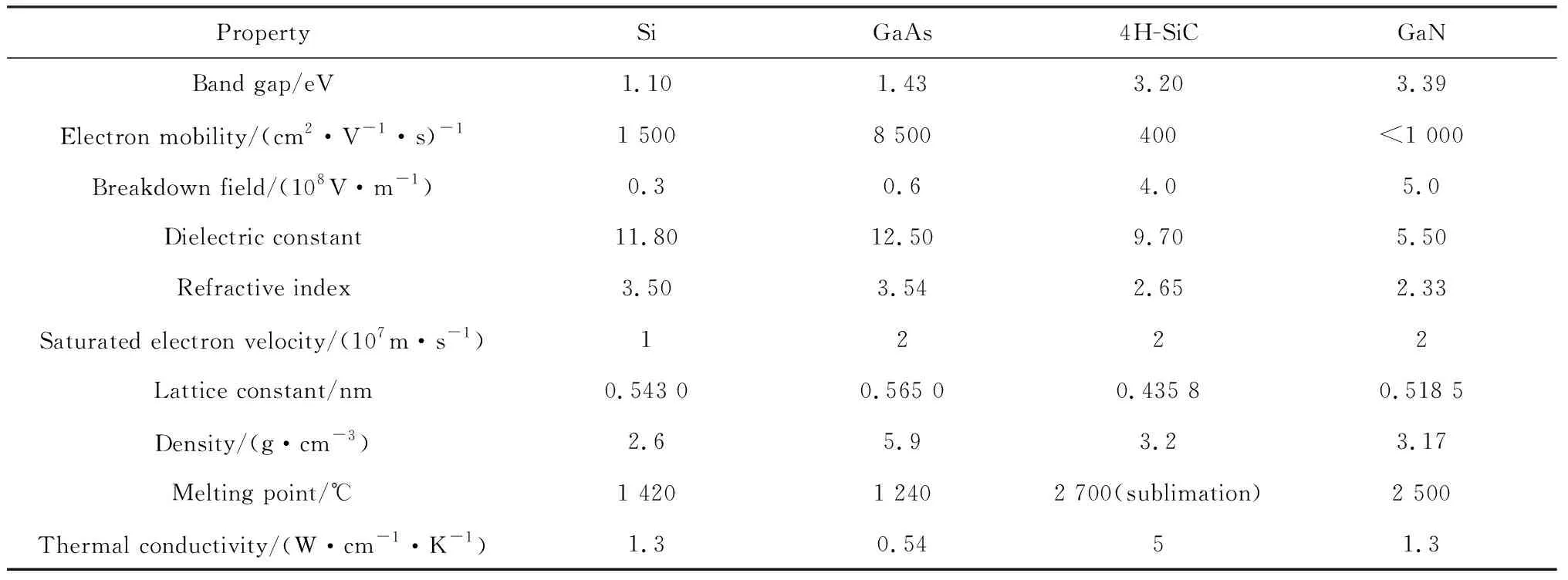

1 基本性质、研发历史

如表1所示,SiC的临界击穿电场是Si的10倍,GaAs的5倍,这提高了SiC基器件的耐压容量、工作频率和电流密度,降低了器件的导通损耗。加上比Cu还高的热导率,器件使用时无需额外散热装置,减小了整机体积。这些均是SiC材料的极大优势。SiC器件具有极低的导通损耗,而且在超高频率时,可以维持很好的电气性能。例如从基于Si器件的三电平方案改为基于SiC的两电平方案,效率可以从96%提高到97.6%,功耗降低可达40%[1]。因此SiC器件在低功耗、小型化和高频的应用场景中具有极大的优势。

表1 Si、GaAs、4H-SiC和GaN基本性质Table 1 Properties of Si, GaAs, 4H-SiC and GaN

Si和SiC作为半导体材料几乎同时被提出,但由于SiC生长技术的复杂和缺陷、多型现象的存在,其发展曾一度被搁浅。SiC的发展历经了多个重要阶段,如表2所示。第一个阶段是结构基本性质和生长技术的探索阶段,时间跨度从1924年发现SiC结构至1955年Lely法的提出[2-3]。第二阶段是物理基本性质研究和英寸级别单晶生长的技术积累阶段。在此阶段物理气相传输(physical vapor transport, 缩写为PVT)生长方法基本确定、掺杂半绝缘技术被提出,至1994年Cree推出了商用的2英寸(50.8 mm)SiC衬底材料[4-7]。从1994年以后,随着国际上半导体照明及2英寸SiC单晶衬底的突破性进展,掀起了全球SiC器件及相关技术的研究热潮。特别是SiC衬底作为核心衬底材料,引起了各国政府的高度重视。早在2002年,美国国防高级研究计划局(DARPA)就启动和实施了宽禁带半导体技术计划(WBGSTI),成为加速提升SiC、GaN以及AlN等宽禁带半导体特性的重要“催化剂”。

表2 SiC单晶技术研发历史Table 2 Research history of SiC single crystal technology

现阶段,SiC电力电子器件一般在N型SiC衬底上进行同质外延,制备器件包括肖特基二极管、MOSFET和IGBT等。Yole预测SiC功率半导体市场规模的年均复合增速预计将达到38%,产业界非常看好SiC器件市场的发展[11]。

半绝缘SiC作为衬底是GaN异质外延的优选材料,在微波领域具有重要的应用前景。相比蓝宝石14%、Si 16.9%的晶格失配,SiC与GaN材料仅有3.4%的晶格失配,加上SiC超高的热导率,使其制备的高能效LED和GaN高频大功率微波器件在雷达、高功率微波设备和5G通信系统等方面均有极大的优势。半绝缘SiC衬底研发工作一直是SiC单晶衬底研发的重点。

2 研究、产业的现状和挑战

2.1 研究进展与现状

鉴于SiC材料的优异性质,自2000年前后国内高校和科研单位开始了SiC单晶的衬底研发,山东大学晶体材料国家重点实验室是国内首批研发单位之一。蒋民华院士根据半导体材料的发展规律和晶体材料国家重点实验室的使命和初心,提出了发展SiC单晶的计划。在科研经费紧张的情况下,积极筹划建设经费,亲自带队,组建了以长江学者特聘教授徐现刚为课题负责人的攻关团队。考虑到国内几乎为零的研发基础,蒋民华院士在研发初始就制定以下重大决策并逐项落实:(1)从产业化着眼,高起点地进行研发。为此他抓住“211工程”二期的大好机遇,重点投入,从国外同时购进两台先进的设备,以加快研发速度。(2)生长和加工并举。SiC是硬度仅次于金刚石的晶体,极难加工,因此在生长和优化SiC晶体的同时,千方百计解决SiC切磨抛技术,攻克从单晶到衬底的难关,率先突破了SiC超硬材料的化学机械抛光技术,打通了走向应用的关键环节。(3)直接和器件研发单位挂钩,把材料置于器件研发的应用链条中,使器件的性能需求变成优化晶体材料质量的动力,从生长到加工真正达到“开盒即用”的指标,从而极大地促进SiC质量的提高。(4)自主创新研制国产PVT单晶设备,为生长装置国产化和SiC单晶的后续发展及产业化打下基础。

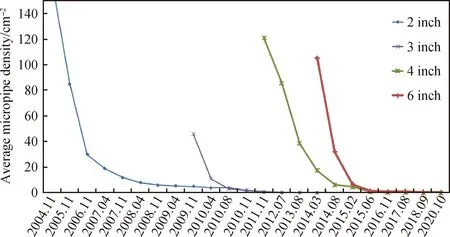

经过二十年的发展, SiC课题组出色地实施了蒋民华院士的决策和部署,不断解决生长和加工的关键问题,攻克了2~6英寸SiC热场调控、超精密加工、半绝缘电学特性、微管密度、单一晶型等多项关键核心技术(具体参见附录)。半绝缘SiC单晶核心技术的突破培养了一批SiC领域的领军人才,为国产半绝缘技术的发展做出了贡献,使我国成为目前世界上第三个掌握半绝缘SiC衬底材料制备技术的国家,山东大学的SiC研究历史就是国内半绝缘SiC单晶衬底发展的一个缩影。

图1 2英寸、3英寸、4英寸和6英寸微管密度逐年降低Fig.1 Micropipe density for 2 inch, 3 inch, 4 inch and 6 inch versus time

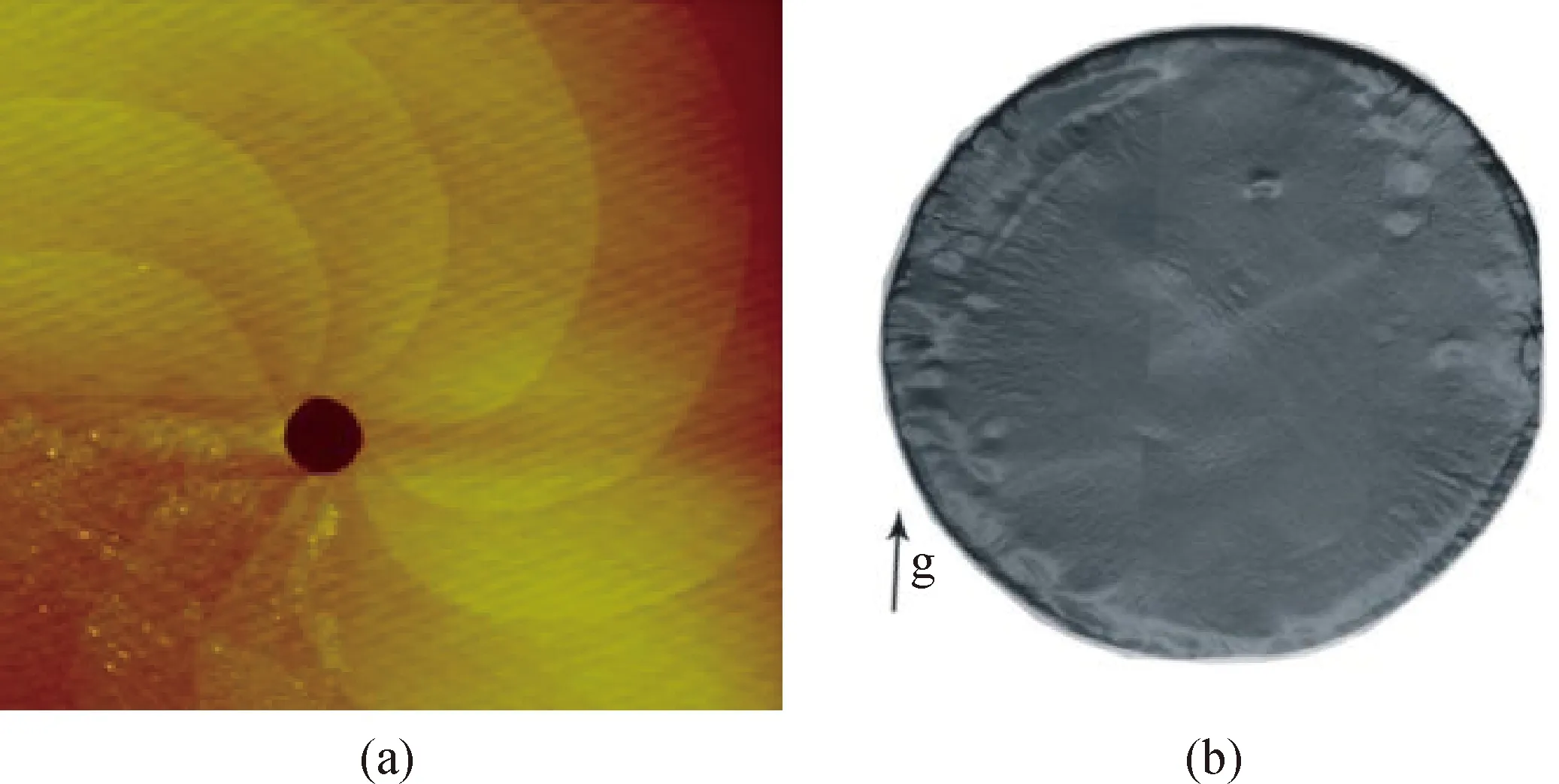

图2 (a)SiC晶体原生表面微管的AFM照片;(b)零微管SiC衬底全片同步辐射形貌结果Fig.2 (a) AFM image showing typical micropipes on the facet; (b) synchrotron topographic image for zero micropipe SiC substrate

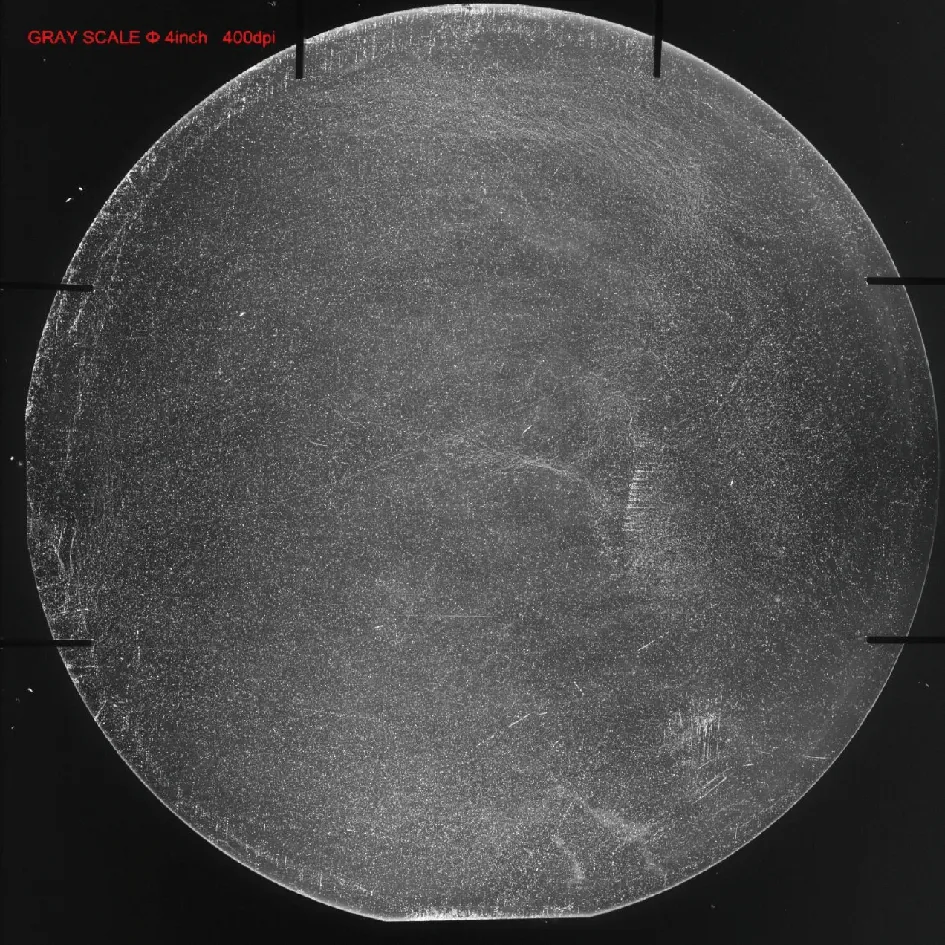

近年来,研究学者将目标转向降低SiC位错密度的研究。现阶段SiC衬底中位错密度的典型值为103~104/cm2。高密度的位错缺陷大幅降低了器件的性能。不同位错类型对器件性能产生不同的影响。螺位错(TSD)和刃位错(TED)会对器件产率产生影响,如降低载流子寿命;而基平面位错(BPD)对双极性器件的影响较大,会增加导通电阻和漏电流[22-24]。位错的表征手段有很多,其中同步辐射白光形貌术、透射电子显微镜(TEM)是通用的观察方法,但制样相对困难[25-26]。KOH熔融腐蚀结合显微镜观察是目前常用的方法,这种方法制样简单、方便快捷,根据腐蚀坑的形貌、尺寸、截面等信息可分辨出不同的位错类型,且可实现全片的观察[27-28]。而采用PL等光学方式可以全面分析缺陷、划痕、颗粒等[29]。山东大学在半绝缘SiC衬底腐蚀坑表征和辨别[30]、刃位错线形成小角度晶界机制[31]、氢气对缺陷密度影响[32]和选择区域侧向外延生长降低缺陷[33]等方面开展了大量工作。图3是山东大学SiC衬底全片腐蚀照片,其TSD密度为390/cm2,BPD密度为221/cm2。

具有不同电学特性的SiC衬底研制一直是SiC单晶研究中的重要工作。现阶段SiC衬底主要有两类。第一类是N型导电的SiC衬底,其电阻率小于30 mΩ·cm,主要用于同质SiC薄膜外延制备电力电子器件。第二类是半绝缘 SiC衬底,电阻率大于105Ω·cm,用于异质生长GaN薄膜制备射频器件。其中半绝缘SiC衬底材料一直是研发的重点,也是难点。生长半绝缘SiC材料的主要难度之一就是如何降低晶体中由石墨坩埚、保温吸附和粉料中掺杂引入的N施主杂质[34-36]。第二个主要难点就是在保证晶体质量和电学性质的同时,引入深能级中心补偿残存的具有电学活性的浅能级杂质[37-39]。其中引入过渡金属V作为深能级杂质制备的SiC衬底材料被称为掺杂半绝缘。2007年,山东大学宁丽娜等首次报道了半绝缘6H-SiC单晶的生长工作[40],采用V掺杂技术获得电阻率高于1010Ω·cm的衬底材料。SIMS测试显示其晶体中V的含量处于同一数量级(5.2×1016~1.1×1016cm-3),显示了较高纵向掺杂均匀性。2016年山东大学彭燕等报道了高质量半绝缘6英寸4H-SiC生长研究工作,利用数值模拟获得高均匀、高质量的半绝缘6英寸SiC衬底材料[41]。拉曼光谱Mapping 测量显示6英寸SiC衬底全片无多型,均为4H-SiC 晶型。X射线摇摆曲线显示半宽小于30 ″。采用掺杂过渡金属V杂质,获得了电阻率超过5×109Ω·cm 的SiC衬底。

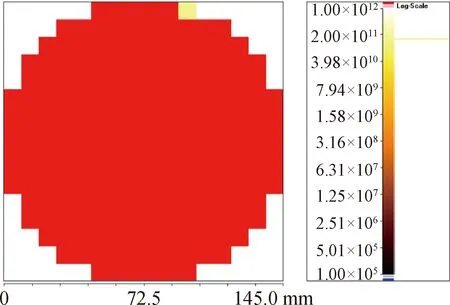

利用本征点缺陷作为深能级中心补偿浅能级杂质称为高纯半绝缘。由于高纯半绝缘SiC衬底需要将背景浅能级杂质控制在1016cm-3数量级,其制备难度相对更高。2010年以前只有Cree可提供PVT法制备的高纯半绝缘衬底材料。山东大学在掺杂半绝缘研究的基础上,首要解决的是高纯粉料的合成工作,采用二次合成法在保证合成产率的基础上,提高合成粉料的纯度[42]。并于2014年首次在国内报道高纯半绝缘SiC衬底制备工作,并以此为基础制备AlGaN/GaN异质结HEMT器件,其室温二维电子气迁移率达到2 053 cm2/(V·s)[43]。图4为山东大学6英寸高纯半绝缘SiC衬底的电阻率分布图。

图3 SiC衬底全片腐蚀,其TSD密度为390/cm2,BPD密度为221/cm2Fig.3 Whole wafer etching of SiC substrate, TSD density is 390/cm2, BPD desnity is 221/cm2

图4 6英寸高纯半绝缘SiC衬底的电阻率分布图Fig.4 Resistivity mapping of 6 inch high purity semi-insulating SiC substrate

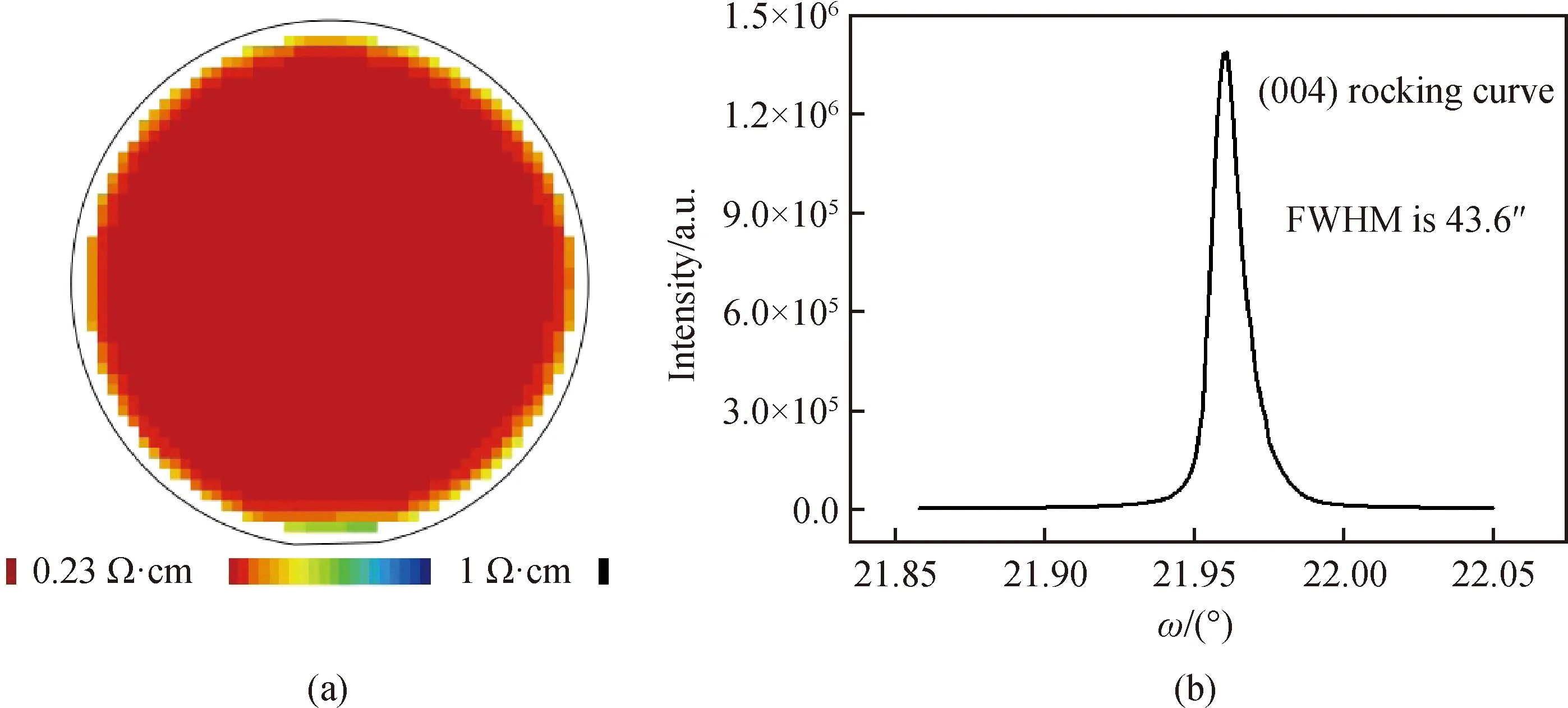

P型的SiC是制备高功率电力电子器件的理想衬底,但电阻率很难降低,其P型掺杂技术仍在研究阶段。由于P型掺杂的难点,如受主电离能高导致衬底电阻率高;缺少合适的气体掺杂源,导致掺杂不均匀;受主元素蒸汽压高导致晶体中产生大量缺陷等使得生长P型体块SiC相对困难[44-46]。在高压领域中,采用理论模拟表明:N沟道SiC IGBT在性能上远远优于P沟道SiC IGBT[47-48]。现阶段N沟道IGBT制备因为欠缺P型SiC衬底材料,制备过程相对繁琐,增加了N沟道IGBT器件的制备难度。因此,高质量低电阻率的P型SiC衬底对N沟道IGBT器件的研制具有重大的应用价值。山东大学采用B-Al共掺获得了高质量4英寸低电阻率的P型样品,其全片电阻率均低于0.258 Ω·cm,结果如图5所示。X射线摇摆曲线结果显示其半宽仅为43.6″。

图5 (a)4英寸P型SiC晶体电阻率分布图;(b)X射线摇摆曲线(004)晶面,FWHM为43.6″Fig.5 (a) Resistivity mapping of 4 inch P type SiC substrate; (b) X-ray rocking curves for (004), FWHM is 43.6″

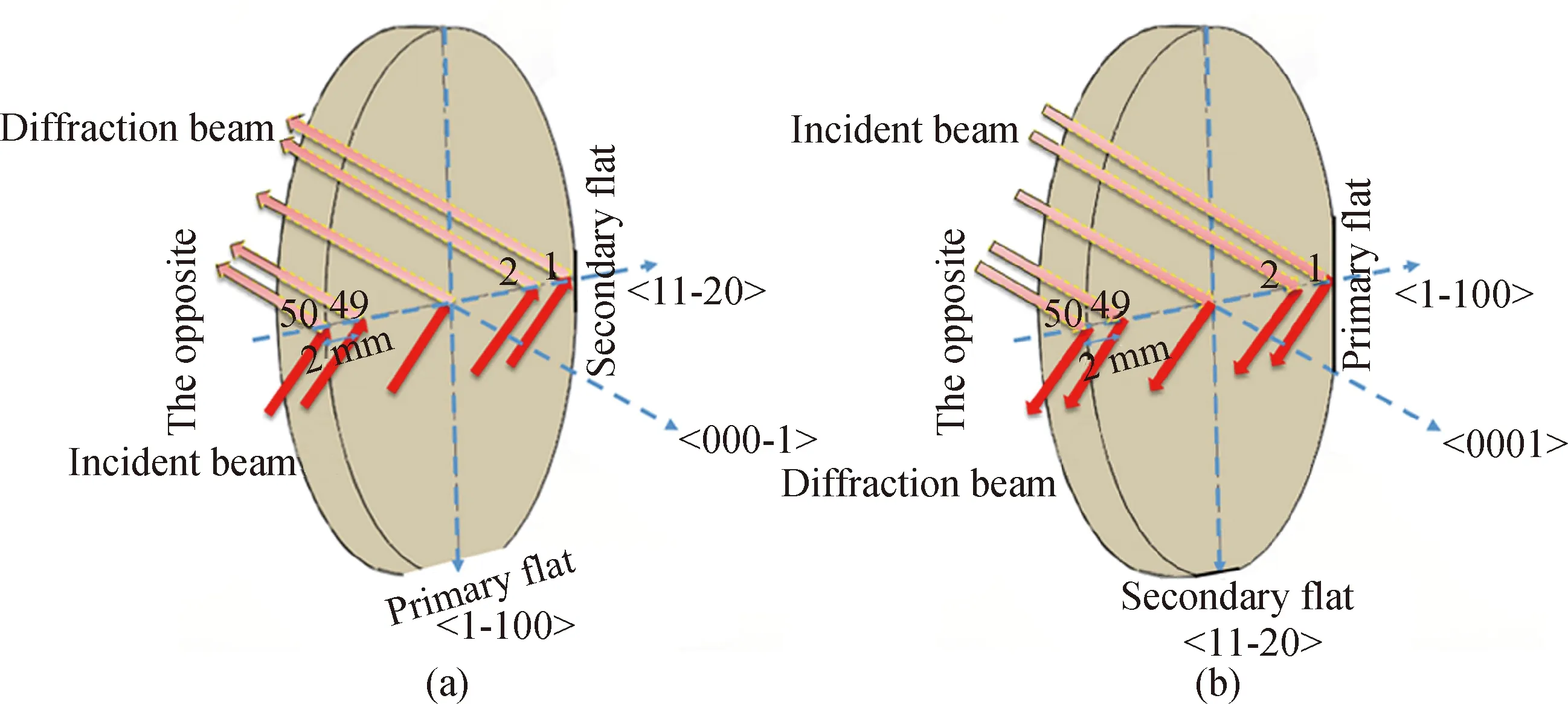

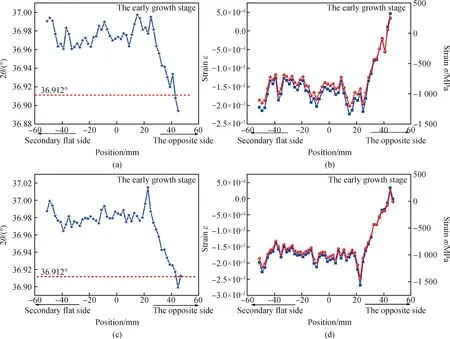

随着单晶直径的扩大,特别是6英寸(150.00 mm)和8英寸(200.00 mm)晶体的研发,较大的径向温度梯度会引入位错等缺陷,严重情况下甚至出现开裂等问题。山东大学的谢雪健等利用中子衍射方法定性分析了晶体中的应力情况,中子衍射测量示意图如图6所示,生长初期在小边区域晶体存在较大压应变,而在小边对面区域存在较小的张应变,应变大小在-2.230×10-3~4.633×10-4之间(见图7(b))。生长后期晶体(0004)晶面的应变在-2.685×10-3~3.317×10-4之间(见图7(d))。生长初期、后期晶体<0001>方向的应力大小基本一致,大小在-1 445~178 MPa,应力沿<11-20>方向。同时也说明晶体中<0001>方向的应力具有继承性[49]。

图6 中子衍射示意图(a)沿 <11-20>方向(11-20)晶面衍射测量示意图;(b)沿 <1-100>方向(1-100)晶面衍射测量示意图[49]Fig.6 (a) and (b) represent the measurement schematics of the (11-20) and (1-100) diffraction, respectively[49]

图7 (a)4H-SiC晶体生长初期沿<11-20>方向(0004)晶面衍射角度变化;(b)生长初期晶体<0001>方向应变和应力分布情况;(c)4H-SiC晶体生长后期沿<11-20>方向(0004)晶面衍射角度变化;(d)生长后期晶体<0001>方向应变和应力分布情况[30]Fig.7 The (0004) diffraction information obtained from the crystal grown at different stages. (a) and (b) represent the (0004) plane diffraction angles, and the strain and residual stress as a function of position of the crystal grown at the earlygrowth stage, respectively. (c) and (d) represent the (0004) plane diffraction angles, and strain and residual stress as a function of position of the crystal grown at the later growth stage, respectively[30]

2.2 挑战与产业现状

器件的飞速发展和应用的扩展,给SiC单晶带来诸多挑战。一是成本问题,SiC衬底的价格仍远远高于Si、蓝宝石等衬底。降低成本需要更加成熟的生长和加工技术,一方面提高衬底材料的成品率,另一方面是通过扩径研究增大面积,降低单个器件成本。2015年国际厂商Cree等推出了200 mm的SiC衬底样品,并积极扩大产能,与英飞凌、意法半导体、安森美等国际半导体厂商签订长期的6英寸SiC衬底供货协议,为光伏逆变器、电动汽车等高增长市场提供材料支撑。2019年,II-VI签署了一项总金额超过1亿美元的多年协议,为部署在5G无线基站的氮化镓射频功率放大器提供碳化硅衬底。

其次就是单晶质量方面的问题。SiC单晶衬底的位错密度仍高达103/cm2以上,其面型参数如Warp等也难以控制[22-24]。因此如何控制相关参数,减低缺陷密度、控制面型是6英寸和8英寸衬底质量优化的主要工作。2017年II-VI公司在Silicon carbide and related material 会议上报道了200 mm衬底位错密度控制的相关工作,其位错总数已经实现了2.8×103/cm2。然而如何控制位错密度鲜有报道。

最后一个技术挑战是包括新的生长方法、温场设计、掺杂和加工等技术探索。现阶段如高温化学气相沉积法(HTCVD)、液相生长技术仍在研发阶段,需要进一步的关注[50-59]。HTCVD法的特点是不受粉料的限制,以高纯气体作为原料,适合半绝缘单晶的制备。随着技术发展,其位错密度也逐步降低至103/cm2,生长速率从最初的微米量级提高到毫米量级[51-52]。但是相比PVT,其成本仍然较高。

日本相关单位一直致力于液相法。液相法的优点是近平衡生长,可以获得低缺陷密度衬底。难度是Si溶液中的C溶解度极低,很难形成化学计量比的溶体,这就导致单晶生长速率极低。因此考虑加入金属催化剂如Ge、Al、Cr、Ti、Fe等增加碳的溶解度,其中Fe基的Fe-Si合金速率可实现200 μm/h的生长[53-55]。现阶段液相生长可以实现扩径生长,直径最大到4英寸[60-61]。同时,在籽晶缺陷密度很大的情况下,生长的晶体缺陷密度也仅有籽晶的十分之一,有助于实现零螺位错、刃位错的衬底生长[59]。

3 结语与展望

纵观半导体70多年的发展历史,技术的不断进步与更新是其特色。SiC材料也是这样,一方面单晶尺寸不断增大,另一方面材料生长工艺持续改进,质量不断提升。

现阶段,国产SiC衬底技术和产业均有了长足进步。但从国际市场看,其占有率较低。SiC衬底生长工艺和产品从直径、缺陷密度、稳定性等参数上与国际主流商用单位Cree等的同类产品还有一定差距。这是挑战也是机遇。

基于SiC单晶生长饱和蒸汽压大、组分偏移、多晶共生等固有物性,如何满足未来外延和器件应用的不同需求,解决大尺寸、高质量、高性能单晶气相生长等科学问题,继续开展SiC单晶生长与加工的基础和应用研究,逐步突破核心技术,显得异常必要和迫切。

附录

(山东大学SiC研究历程)

2000年,正式启动SiC项目;

2003年,从国外同时购进的两台先进设备单晶炉到位,单晶生长和加工研发启动;

2003年,突破单晶生长技术,成功研发2英寸6H-SiC单晶;

2006年,突破超精密加工技术,获得2英寸开盒即用SiC衬底;

2007年,攻克掺杂半绝缘技术,2英寸SiC衬底试用取得突破进展;

2008年,掌握4H晶型稳定技术,成功自主研发2英寸SiC单晶炉;

2010年,成功自主研发4英寸SiC单晶炉;

2011年,半绝缘SiC衬底制备技术产业转化;

2013年,6英寸4H-SiC单晶研发成功,完成核高基专项半绝缘SiC衬底产品检验;

2014年,攻克高纯半绝缘制备核心工艺,荣获山东省科学技术发明一等奖;

2015年,突破高纯4英寸4H-SiC单晶制备,完成核高基专项高纯半绝缘SiC衬底产品检验;

2018年,8英寸SiC单晶炉研制成功;

2019年,6英寸SiC衬底制备技术产业转化。