BCD工艺下光电集成的单光子雪崩光电二极管及前端电路的研制

史晓凤,庞 雪,朱丽君,张新宇,张 媛,韩 波,李佩君,郭 博,程 翔*

(1.阜阳师范大学计算机与信息工程院,安徽阜阳236037;2.厦门大学航空航天学院,福建厦门361102)

1 引 言

随着工业仪器的智能化及人脸识别等技术的兴起,二维图像由于缺失深度信息存在无法甄别合成图像手段的风险。三维(Three-Dimensional,3D)信息能更加客观全面的重构实物,获得许多人眼所不能直接获取的量化参数,有效弥补二维图像的缺点,因此成为视觉传感的研究热点。主流的3D传感技术有双目视觉、结构光技术和时间飞行法(Time Of Flight,TOF)技术[1]。TOF技术通过计算传感器收发红外光的时间差来测量距离,具有响应速度快、深度精确度高(可达微米级)、功耗低,不需要复杂软件支撑等特点,因此得到了广泛的应用。TOF主要由盖革模式-单光子雪崩光电二极管(Gage Mode-Single Photon Avalanche Photodiode,GM-SAPD)探测阵列、淬灭复位电路以及时间数字转换器组成[2-3]。其中,淬灭复位电路用来控制雪崩脉冲,以方便光子计数。TOF对探测器阵列性能和相关电路的精确度的要求较高。随着CMOS工艺的不断进步,硅基SPAD器件的性能逐渐提高,高性能SPAD器件可以显著提高TOF系统的性能指标,因此其设计具有重要意义[4-6]。

GM-SPAD是基于雪崩效应的单光子探测器,主要用于探测微弱光信号。为了实现器件的高度集成化,探测单元面积应尽可能的小,并且结合淬灭电路可实现大规模阵列集成,用于量子通信、生物医学检测、荧光测温等领域。经过几十年的研究,GM-SPAD经历了从台式到平面的演变[7]。近年来,很多基于标准工艺的GMSPAD研究都提到了保护环的重要性,这是因为在深亚微米制造工艺中注入和扩散步骤难以避免在边缘区域形成弯曲的PN结,有研究表明弯曲结角处的电场比平面结电场高得多,所以容易导致边缘提早击穿,影响探测器的性能[8]。研究表明,通过设计保护环能够有效防止边缘提前击穿,比如低掺杂阱保护环结构,中心浅层P+的边缘注入轻掺杂的Pwell,具有消除突变的边缘掺杂曲线和角效应的作用,降低了电场强度,从而避免边缘提前击穿[9]。保护环的结构会显著影响器件的暗计数率(Dark Count Rate,DCR)[10-12]。理查森等人采用130 nm CMOS工艺实现了一种虚拟深阱保护环SP-AD结构。与常规Pwell保护环相比,虚拟深阱保护环显著降低了SPAD的DCR[13]。

BCD是一种有多层金属,N埋层和P外延层的双极型CMOS混合信号工艺。众所周知,P外延层与P衬底相比晶格缺陷和点缺陷少很多,金属杂质的浓度更低,在半导体器件制造中更为理想。本次设计的探测器主要针对600~900 nm波段的光子,由文献[14]可知1μm深的耗尽层处650 nm光的吸收率能达到30%左右,对于更长波长的光则需要更深的耗尽层。同传统CMOS工艺相比,BCD工艺的PN结深更深,可以提供30 V的高压,更符合本次设计的需求。

本文基于BCD工艺设计了一种用于检测微弱光信号的SPAD及前端淬灭-复位电路(QAC),该圆形P+/Nwell/Deep Nwell结构SPAD与传统的P+/Nwell结构以及P+/Nwell/BNwell结构相比,在击穿电压和响应度等关键指标上具有显著优势。,

2 SPAD结构设计与优化

2.1 结构设计

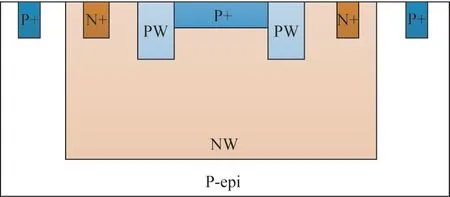

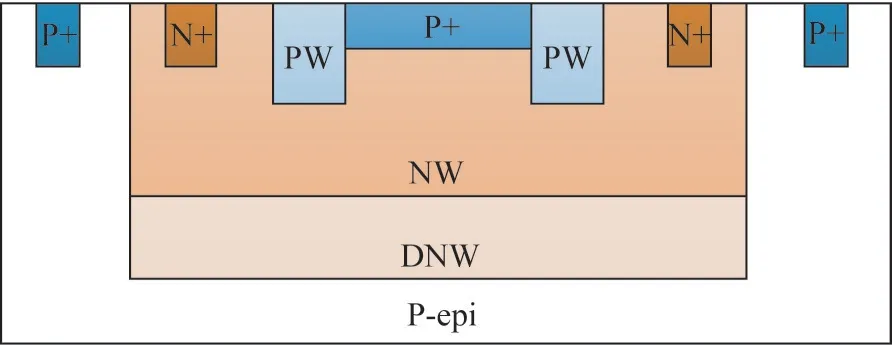

图1 为传统CMOS工艺中的P+/Nwell结构SPAD,记作PD1。该结构以P-epi为衬底,P+为中心有源区,P+附近的轻掺杂Pwell形成保护环,防止发生边缘提前击穿,P+与Nwell接触的地方为倍增区,从P+引出阳极金属接触,N+引出阴极金属接触。为了提高光谱响应,降低DRC,本文在结构P+/Nwell结构的基础上添加了DNwell,如图2所示,记作PD2。由于DNwell的浓度梯度呈逆向分布,即靠近表面的浓度更低,使形成的PN结能承受更高的电压,不易被击穿。同时,利用DNWell将器件与衬底有效隔离开,能减少噪声和闩锁效应。为与P+/Pwell/DNWell结构做比较,设计了P+/Pwell/Buried-Nwell结构,记作PD3,如图3所示。同样以P-epi为衬底,P+为中心有源区,利用Pwell增大了与Buried-Nwell的接触面积,同时避免了普通P/N阱高掺杂雪崩结引起的带带隧穿,有效降低DCR,两端的Pwell和Buried Nwell构成双重保护环,使电场分布更加均匀,能够有效阻止边缘提前击穿。

2.2 电场分布

图1 P+/Nwell结构(PD1)Fig.1 P+/Nwell structure(PD1)

图2 P+/Nwell/Deep-Nwell结构(PD2)Fig.2 P+/Nwell/Deep-Nwell structure(PD2)

图3 P+/Pwell/Buried-Nwell结构(PD3)Fig.3 P+/Nwell/Buried-Nwell structure(PD3)

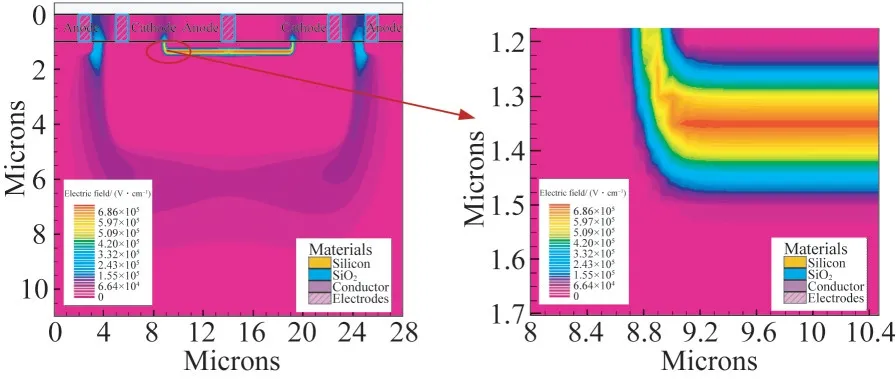

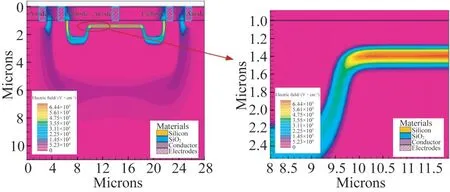

基于Silvaco对3种结构的探测器进行仿真设计。结合工艺设计规则,为了尽可能地减小探测器的整体面积同时增加探测器的填充系数,采用28μm长的衬底,以光敏直径为10μm进行仿真。图4为PD1无P阱保护环的电场分布,电场集中在P+注入区,且电场较强,从局部放大图可以清晰地看到拐角处电场高达6.6×105V/cm,在此高电场条件下容易发生角效应,引起边缘提前击穿。图5为PD1有保护环的电场分布,可看到电场主要分布在两个P阱和P+注入区的外缘线,P+注入区中间电场较高,两端边缘处电场较低,拐角处电场约为4.0×105V/cm,能防止提前击穿。从有无保护环两种结构的电场仿真可知,添加保护环结构能有效预防角效应引起的边缘提前击穿。

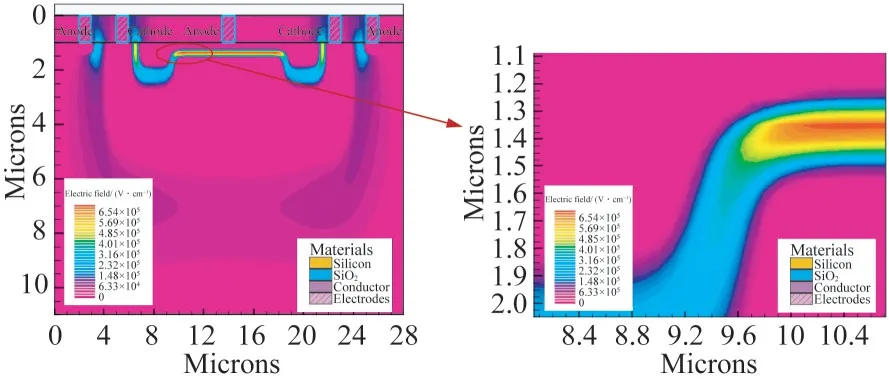

PD2的电场分布如图6所示。电场集中在P+区,两边的P阱上也承担了部分电压,从图6的局部放大图可以看出P+区两端边缘处电场明显降低,减少了边缘击穿的风险。

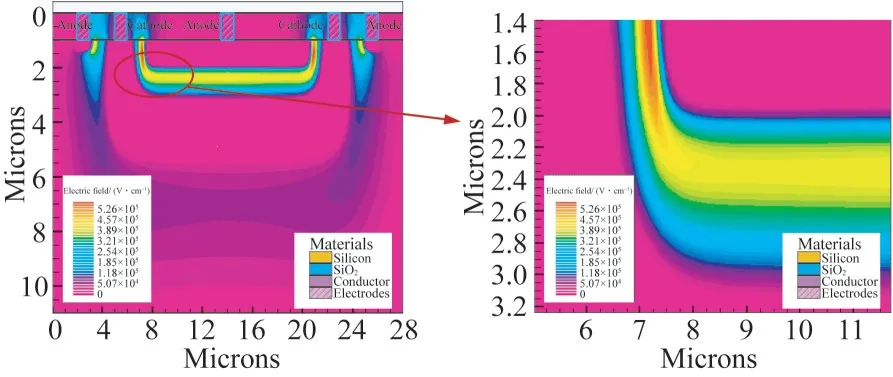

PD3结构的电场分布如图7所示。电场集中在Pwell上形成环状,电场分布均匀,拐角处电场约为4.4×105V/cm。由局部放大图可知,拐角处电场明显比其他区域电场小,证明此结构可以预防角效应导致的边缘提前击穿。

图4 PD1无保护环时的电场分布Fig.4 Electric field distribution of PD1 without protection ring

图5 PD1有保护环时的电场分布Fig.5 Electric field distribution of PD1 with protection ring

图6 PD2的电场分布Fig.6 Electric field distribution of PD2

从3种探测器的电场分布上看,他们均能有效地防止角效应带来的边缘提前击穿,前两种结构在P阱与P+注入连接处附近的电场变化更为明显,PD3的电场分布更均匀,数值也更高。

图7 PD3的电场分布Fig.7 Electric field distribution of PD3

2.3 I-V特性

反向电压增加到一定值,使PN结的电流急剧增加的现象被称为击穿现象,此时对应的电压为击穿电压。PD1的I-V曲线如图8中modelex720-3.log所示,反偏电压较小时,电流约为1.0×10-12A,且随着反偏电压的增大变化不大,电压增至10.2 V时电流陡增至1.0×10-2A,随后的电流增长趋于饱和。GM-APD的特性曲线表明,当电压小于10.2 V时,探测器工作在反偏线性区,击穿电压为10.2 V,电压大于10.2 V时处于盖革状态。PD2的击穿特性曲线如图8中modeldn720-3.log所示,电流在反偏电压为10.5 V处陡增至1.0×10-2A,击穿电压相比前一种结构增加了0.3 V,所以此种结构能承受更高的电压。

PD3的击穿特性如图8中modelbn720-3.log所示,击穿点约为21.6 V,比前两种结构都要高。这是由于形成的PN结位于Pwell和BNwell之间,结深较前两种结构大很多,P阱相比P+的浓度要低很多,导致空穴的浓度较小,形成的耗尽层宽度较大,所以需要提供更高的反向偏压才能击穿。显然,PD1和PD2的击穿电压较低。

图8 三种SPAD结构击穿电压的仿真曲线比较Fig.8 Comparison of breakdown voltage simulation curves of three SPAD structures

2.4 光谱响应

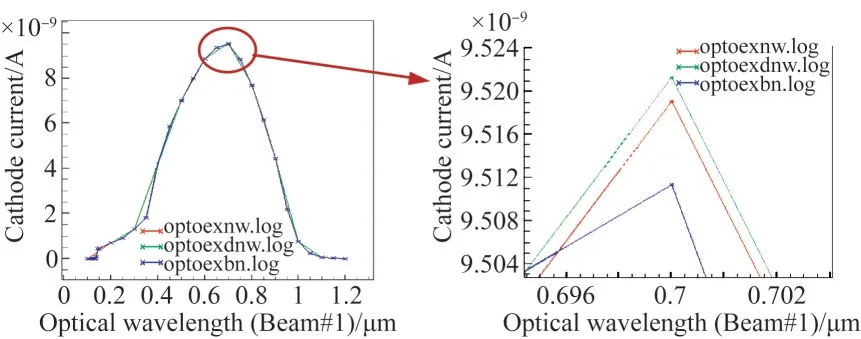

光谱响应反映了光子产生电子空穴对的能力,对于不同波长的光,探测器转换成光电流的能力也不一样,设置不同波长的光束照射探测器。3种SPAD结构在反偏电压相同时入射波长与光电流的关系曲线如图9所示,0.35~0.7μm波段中光电流随波长的增加速度更快并在波长约为0.7μm达到峰值,峰值处光电流约为9.5 μA,波谱范围较宽为0.35~1.2μm。将峰值处放大可见PD2的峰值最大,对应绿色的线条,且整个曲线都在P+/Nwell结构上方(彩图见期刊电子版)。因此,PD2的光谱响应能力优于另外两种。

图9 三种SPAD结构的光谱响应仿真曲线Fig.9 Spectral response simulation curves of three SPAD structures

2.5 有源区尺寸仿真

有源区作为光子探测吸收的主要区域,其尺寸对探测器也有重要的影响。大尺寸的有源区能增加探测面积,提高探测器的填充系数,同时也会引起较高的DRC,探测器整体体积过大等缺点,所以需要研究不同直径有源区的特性,优化设计以保证流片的效果。本文在有源区直径分别为6,8,10μm的情况下对3种探测器的I-V特性进行了仿真。

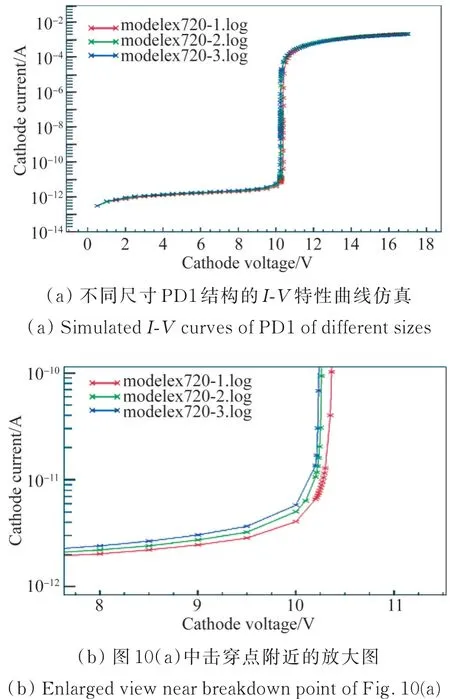

PD1反向偏压和电流关系的仿真结果如图10所示,其中modelex720-1.log、modelex720-2.log、modelex 720-3.log分别为有源区直径为6,8,10μm时的仿真曲线。击穿点附近的I-V曲线的放大图如图10(b)所示,由图可知有源区直径为6μm时击穿电压最高,10μm时击穿点电压最低。

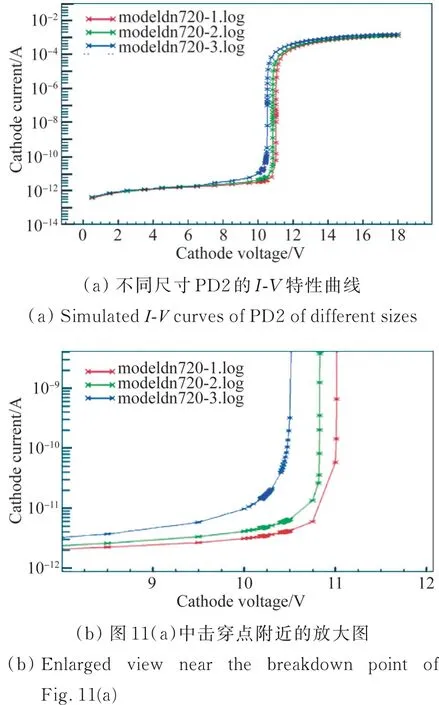

PD2的I-V仿真曲线如图11(a)所示,modeldn720-1.log、modeldn720-2.log、modeldn720-3.log分别为有源区直径为6,8,10μm时的仿真结果。击穿点处的局部放大图如图11(b)所示,有源区直径为6μm时探测器的击穿电压约为11 V,8μm时击穿电压为10.8 V,直径增加到10 μm时击穿电压为10.5 V。

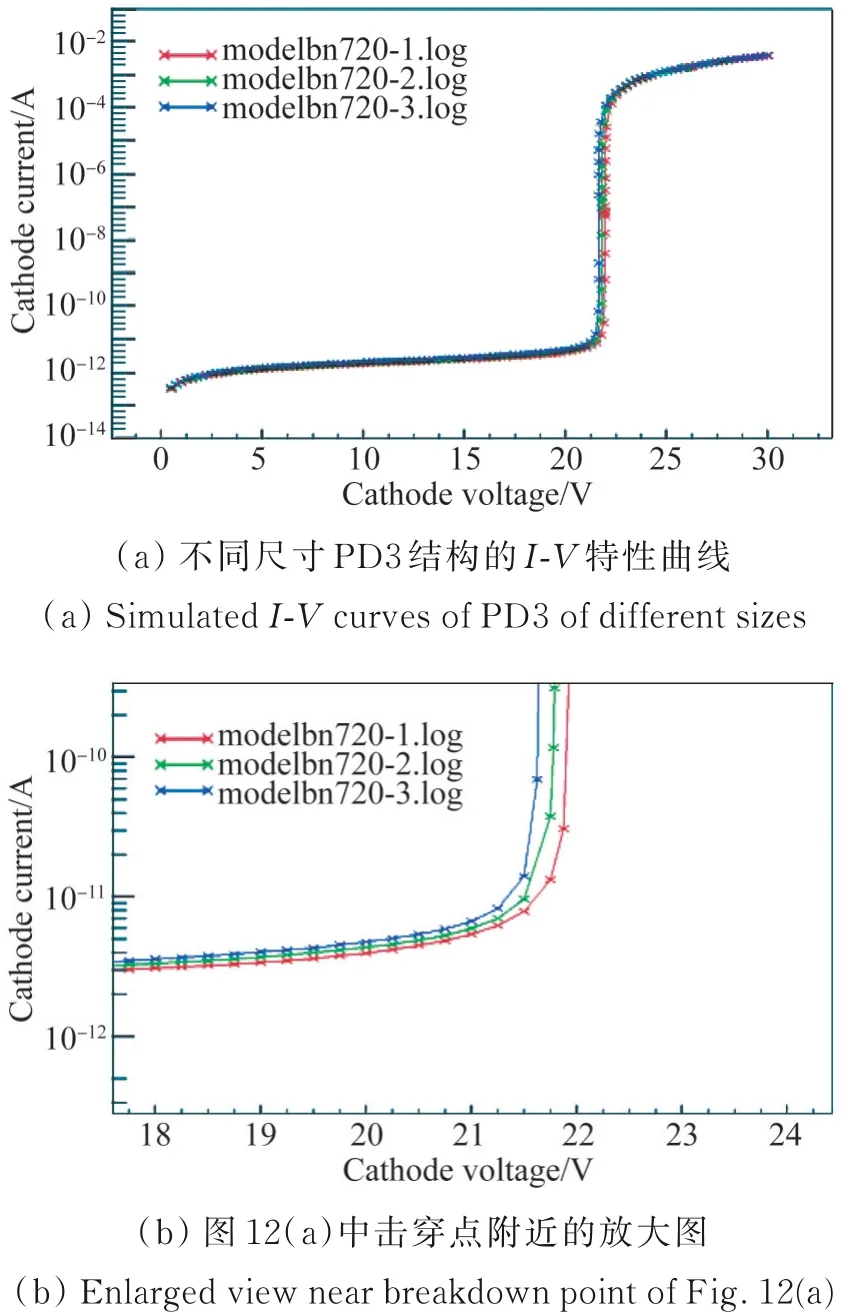

PD3的I-V特性仿真曲线如图12所示,modelbn720-1.log、modelbn720-2.log、modelbn720-3.log分别为有源区直径为6,8,10μm时的仿真结果。有源直径为6μm时击穿电压为21.9 V,8 μm时为21.7 V,10μm时为21.6 V。

图10 不同尺寸的PD1的I-V特性曲线Fig.10 Simulated I-V curves of PD1 of different sizes

通过比较3种光电探测器的仿真图,可以看出随着有源区尺寸的增大,3种结构的击穿电压的节点均逐渐减小,这跟大面积有源区的探测器中更容易碰到局部高电场区域发生击穿的情况有关。为了获得较低的击穿电压,较高的响应度,最终选取有源区尺寸为10μm的PD1和PD2进行流片。

3 前端电路的协同设计与仿真

图11 不同尺寸的PD2的I-V特性曲线Fig.11 Simulated I-V curves of PD2 of different sizes

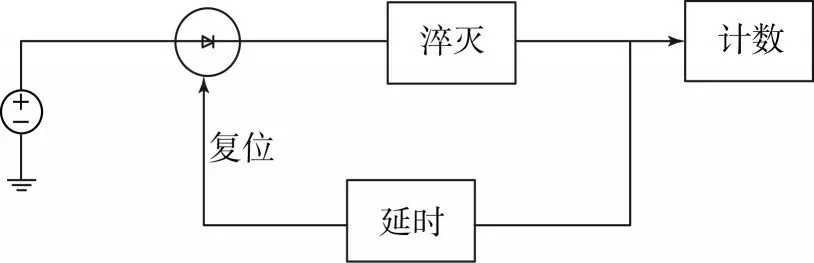

由于探测器雪崩过程不能自主熄灭和发生,因此前端电路对GM-APD的控制和信号读出发挥着重要的作用。前端电路的工作结构如图13所示,信号光引发探测器发生雪崩,同时作为TDC(Time Digital Conventor)的计时开始信号,淬灭电路快速淬灭雪崩并经延时复位恢复雪崩准备状态,产生的雪崩脉冲作为TDC的计时终止信号。

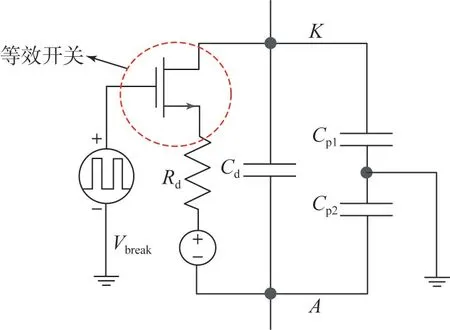

3.1 GM-APD等效模型设计

原始的等效模型结构[14]简单,能模拟GMAPD的充电特性,在电流源充电时探测器两端电压呈线性增长,但是缺乏对体电阻及寄生电容等因素的考虑,只能进行粗略的仿真分析,并不能准确地描述探测器工作时阴阳两极电压的变化。在改进探测器结构时应考虑体电阻和寄生电容的影响。如图14所示,Vbreak是雪崩击穿电压,Rd为APD的内电阻,电容Cd为反相偏压结电容,Cp1和Cp2分别为阳极-衬底结电容和阴极-衬底结电容,通常有Cp1≈Cp2。开关控制雪崩的发生,开关导通时电容放电探测器处于准备探测状态,开关断开时电容充电探测器不发生雪崩。仿真中开关采用MOS管代替。

图12 不同尺寸的PD3的I-V特性曲线Fig.12 Simulated I-V curves of PD3 of different sizes

图13 外围电路结构Fig.13 Peripheral circuit structure

3.2 淬灭电路的设计仿真

APD工作在盖革模式下意味着一旦触发雪崩,雪崩电流会持续存在,无法继续进行检测,且长时间的大电流通过会导致器件发热产生较大的功率损耗,载流子被深能级的陷阱捕获使后脉冲发生的概率增加,因此必须采取措施控制雪崩并恢复原来的状态。淬灭电路的功能就是中断雪崩倍增过程,改进的主动淬灭电路拓扑如图15所示,其中Vex为过偏压。改进后的电路结构紧凑,没有比较处理单元和相关多余电阻,不需要选取合适参考电压,开关切断电流路径即可达到淬灭的目的,相比于传统的淬灭结构响应速度更快。

图14 仿真电路的模型Fig.14 Model of simulation circuit

当NMOS栅源偏压大于导通阈值电压Vgs时管子导通,利用这一性质用NMOS管代替开关,其中MQ为淬灭开关,MR为复位开关。M2和M3为一组由PMOS和NMOS构成的简单反相器,MQ导通MR截止时,探测器的阳极处接地电压为低电平,经反相器翻转输出高电平信号,此时探测器两端偏压大于击穿电压,有光子入射时激发雪崩,M1和MQ形成的支路受探测器突增的光电流影响电流增大。同时,M1和M3形成电流镜结构,电流复制至反相器使二极管阳极处的电压增加,输出信号电平减小最终使MQ的栅极电压低于阈值电压Vgs,此时的MQ处于截止状态,相当于一个高阻值电阻使阳极的电压逐渐上升直至探测器两端偏压小于击穿电压,探测器成功淬灭。经过后续延时电路处理过的高电平信号作用在MR的栅极上,MR导通并对探测器进行充电。通常为了防止淬灭,充电没有结束开关就已导通或者淬灭不完全有后脉冲的影响,设置延迟时间大于淬灭时间。

仿真基于cadence/spectre,设置击穿电压为10.5 V,二极管阴极处外加电压为12 V,仿真波形如图16所示。从上至下依次为模拟光子到来的开关脉冲波形,二极管阳极处的电压波形,out处电压波形和reset复位管栅极处波形。其中,开关脉冲延迟时间为2 ns,上升时间为1 ps,下降时间为1 ps,脉冲宽度为3 ns,周期为10 ns。从二极管的阳极电压波形可以看出,当开关管处于断开状态时阳极电压近乎为零,二极管两端的反向偏压大于10.5 V;当开关管闭合光子到来时,二极管发生雪崩击穿的同时阳极处电压迅速升高,峰值电压约为1.9 V,此时二极管的两端偏压小于10.5 V的击穿电压,二极管被成功淬灭,随后经复位电路对二极管进行充电使阳极处电压回落到0 V,二极管再次处于击穿状态等待下一次光子的到来。以阳极峰值电压1.9 V的百分之一为标准,即单个周期内电压超过19 mV的时间段可作为死时间,此电路的死时间约为2.6 ns,能够达到快速探测的目的。

图15 淬灭电路仿真Fig.15 Simulation of quenching integrated circuit

图16 淬灭电路的仿真波形Fig.16 Simulation waveforms of quenching integrated circuit

4 实验结果及分析

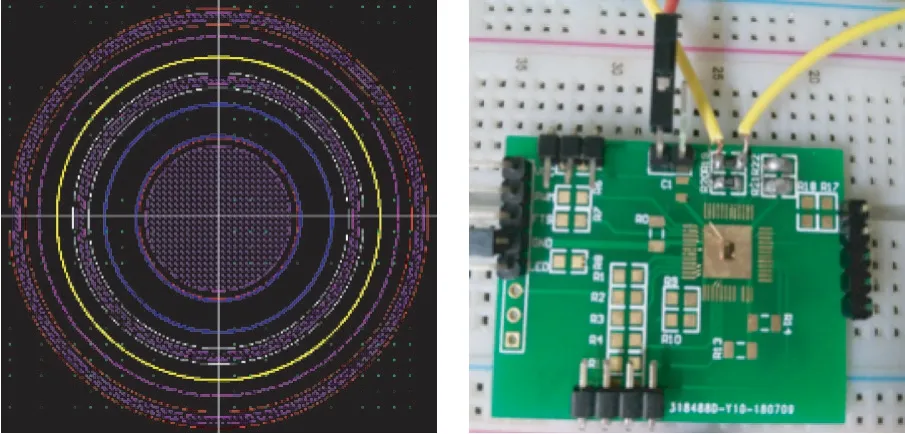

图17 单个探测器的版图及芯片打线封装后的照片Fig.17 Map of individual detectors and test board of chip after drawing package

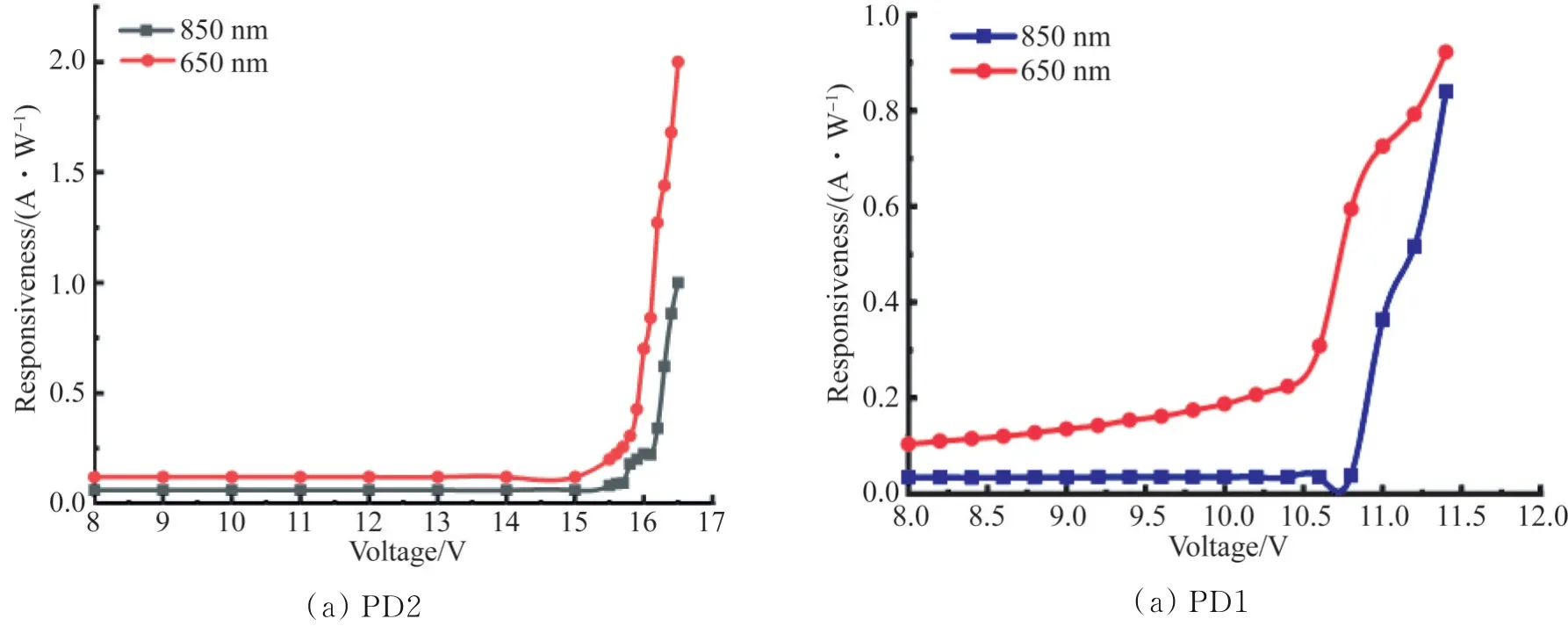

测试实验在室温下进行,图17为单个探测器及芯片封装后的照片。PD2和PD1的APD两端的反向偏置电压与阴极电流关系曲线分别如图18(a)和18(b)所示。由图18(a)可以看出,不加光照时,反偏电压在15.8 V以下,暗电流很小,在10-14A量级;但当反偏电压增至15.8 V时电流增加明显,并随着反向电压的增大不断增加。给APD分别施加650 nm波长和850 nm波长的激光照射,在偏置电压小于15.8 V时,受光生载流子的影响,阴极电流明显比不加光照时大很多,不过仍维持在较低水平;当电压增加至15.8 V附近时电流陡增。从测试I-V变化曲线上不难得出,PD2结构APD的击穿电压为15.8 V,比仿真的击穿电压10.5 V高,这是因为流片工艺的影响,该偏差在允许范围内。电流随电压的变化规律与仿真结果吻合,同时在相同光功率照射下,650 nm波长光对应的电流明显大于850 nm对应的电流,证明了前面的仿真结果和设计的可行性。同时发现,曲线在偏置电压增至约16.3 V时出现了拐点,电压超过拐点后阴极电流迅速增加。这是由于此结构包含P+/Nwell、DNwell/Sub两个PN结,DNwell/Sub形成的PN结因为掺杂浓度较低,所以相对于P+/Nwell形成的PN结击穿电压较高,在电压升高至16.3 V左右时会形成第二次PN结击穿。

从图18(b)可以看出,偏置电压低于10.6 V且无光照时阴极电流较小,在10-12A数量级,在此偏置电压下给予光照会发现,阴极电流比不加光照时有所提升,当偏置电压达到10.6 V后,阴极电流陡增,且相同的偏置电压下和光功率下,650 nm波长对应的电流大于850 nm波长的电流。根据3条曲线的走势可以判断出P+/Nwell结构的雪崩击穿电压点为10.6 V,与仿真结果10.2 V非常接近,在可允许的范围内,测试结果与仿真趋势基本一致。

图18 光电探测器的I-V测试曲线Fig.18 Tested I-V curves of photodetectors

图19 是对两款APD的响应度测试曲线。从图中可以看出,在击穿电压点附近两款APD的响应度明显上升,且650 nm光均比850 nm光的响应度高。PD2在电压达到16 V时,650 nm光和850 nm光对应的响应度分别约为0.8 A/W和0.25 A/W。P+/Nwell在电压为10.8 V时,650 nm光和850 nm光对应的响应度分别约为0.71 A/W和0.39 A/W。

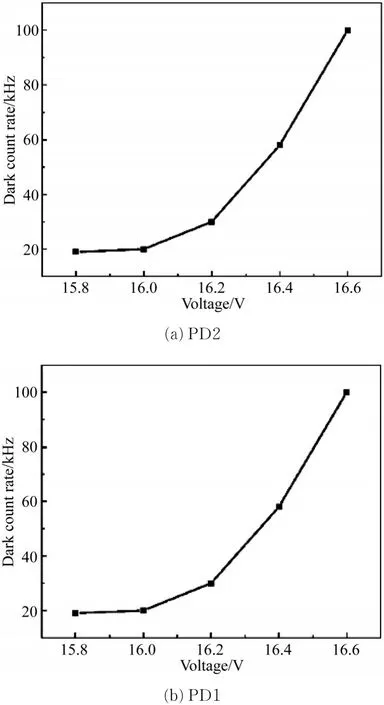

在遮光情况下对APD进行无源暗计数测试,暗计数是APD自身材料缺陷或热载流子造成的雪崩触发,会导致APD在没有光子照射的情况下产生误计数。在APD两端施加不同电压并记录对应的DRC,测试数据如图20和表1所示。随着偏置电压的增大,DRC不断增大,P+/Nwell/DNwell结构中当偏压为16 V时DRC约为20 kHz,P+/Nwell结构中当偏压为10.8 V时DRC约为60 kHz。

图19 PD2和PD1的响应度曲线Fig.19 Responsiveness curves of PD2 and PD1

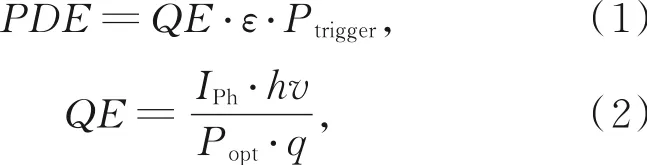

光子探测效率(Photon Detection Efficiency,PDE)是衡量探测器件性能的重要参数指标之一,其数值是探测到的光子数量与入射光子数量的比值,代表了探测器探测光子的能力。影响PDE的主要因素有:(1)有效雪崩区域的量子效率(Quantum Efficiency,QE);(2)几何填充因子ε;(3)入射光子触发雪崩的概率Ptrigger。其中ε为光敏面积与整体面积的比值[7]。则有:

其中:Iph为探测器内部产生的光电流,Popt为入射光的光功率,q是电荷,h为普朗克常量,ν代表入射光子的频率。由式(2)可得响应度R和量子效率η的关系式η=R·1.24/λ。由式(1)可知,PDE与响应度R成正比,而本文设计的SPAD在峰值650 nm处具有较高的响应度(0.8 A/W),因此,在650 nm处应具有较高的PDE。

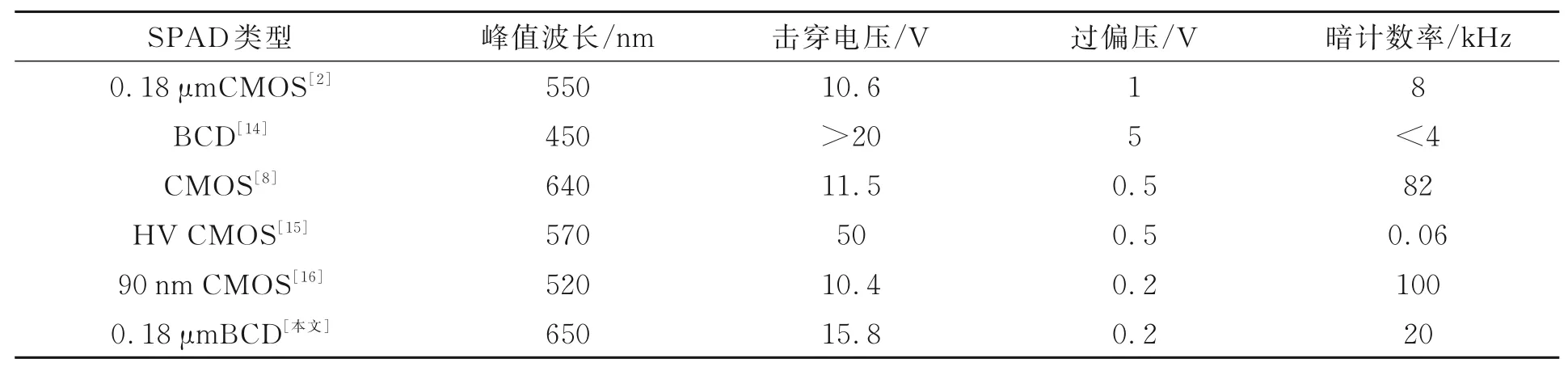

文献[2][15-16]获得了比较低的DRC,尤其是文献[16],在过偏压0.5 V下,仅有60 Hz的DRC,但是APD采用高压CMOS工艺制作,击穿电压高达50 V;文献[15]的击穿电压也高于20 V;文献[2]整体性能都较好,然而其峰值波长在550 nm处,当探测器工作在650 nm处时光子探测概率下降较大。文献[9]的峰值波长在640 nm,击穿电压较小,然而DRC达到80 kHz。文献[17]有较低的击穿电压,但其工艺为90 nmCMOS,价格比较昂贵。综合比较可得,本文设计的SPAD在峰值650 nm处具有较高的响应度,适 合在波段0.6~0.85μm内工作,击穿电压较低。

图20 暗计数率与击穿电压的关系曲线Fig.20 Relationship between dark count rate and breakdown voltage

表1 不同文献中SPAD参数比较Tab.1 Comparison of parameters of different SPADs

5 结 论

本文提出了一种在0.18μm BCD工艺中设计的圆形P+/Nwell/DNwell结构SPAD和前端淬灭-复位电路。SPAD器件雪崩区形成在P阱和DNW之间,具有更均匀的掺杂分布,边缘击穿概率显著降低,深N阱有效减少P衬底流向雪崩区的暗电流,降低DRC,也保证了较小的纵向渡越时间,提高了响应速度。通过TCAD对P+/Nwell/DNwell结构、P+/Nwell结构和P+/Nwell/BNwell结构进行了建模,并且对3种结构的I-V特性、电场分布和光谱响应特性进行了仿真。仿真结果表明,圆形P+/Nwell/DNwell结构具有较低的击穿电压,P+区两端边缘处电场明显降低,降低了边缘击穿的风险,且在650 nm具有较高的光谱响应。同时,为了研究有源区尺寸对器件性能的影响,又在6,8,10μm等不同尺寸下分别对3种结构进行了I-V特性仿真,仿真结果表明,随着有源区尺寸的增大,3种结构的击穿电压的节点均有逐渐减小的趋势,综合考虑,选取有源区尺寸为10μm的结构进行流片。为实现光电探测器与集成电路的协同设计与仿真,改进了APD光电器件的等效电路模型,设计了主动淬灭复位电路,死时间约为2.6 ns,能够达到快速探测的目的。基于CSMC 0.18μm BCD工艺对10μm的P+/Nwell/DNwell结构和P+/Nwell结构进行流片,测试表明,650 nm波长的光均比850 nm波长的响应度高,P+/Nwell/DNwell结构在电压达到16 V时650 nm和850 nm对应的响应度分别约为0.8 A/W和0.25 A/W,以及DRC均优于P+/Nwell结构。由此可见,基于BCD工艺采用高压深N阱工艺,通过合理地设计尺寸和结构,可获得工作波段在0.6~0.85μm,且具有较低的击穿电压和高响应度的SPAD。本文的研究工作为可见光领域的硅基光电集成的高性能探测器的研制提供技术积累。