基于FPGA 的多路抢答器设计与仿真

刘德方,王先超,陈秀明,赵 佳

(阜阳师范大学 计算机与信息工程学院,安徽 阜阳236037)

抢答器在各种竞赛场合被广泛应用,比如:知识竞赛或智力竞赛。目前,其设计方案基本上有两种:一种是用单片机作为主控制器;另一种是用规模较小的数字逻辑芯片设计实现。前者比较灵活,其缺点是若抢答组数多,会有I/O 口不够用的问题[1];后者设计思路简单,但电路可靠性低,而且实现起来难度较大。由于EDA(electronic design automation)技术的飞速发展,以计算机为平台,用EDA 软件为开发工具,借助大规模可编程逻辑器件FPGA(field programmable gate array)芯 片EP2C35F672C8 为实现载体,可以完成以软件方式设计八人四组抢答器硬件电路,并且可以向小型化,速度快,功耗低,便于携带方向发展[2-4]。

利用EDA 技术,采用自顶向下的设计方法,在集成开发环境QUARTUSII9.0 下,利用VHDL(very-high-speed integrated circuit hardware description language)程序设计并生成各个逻辑模块,即各模块的逻辑符号图,最后将各逻辑符号图级联实现基于FPGA 芯片EP2C35F672C8 的多路抢答器。该抢答器可以执行八人四组参赛选手的同时抢答,针对每位参赛选手,设置一个开关按键,以供抢答使用。抢答使能信号由裁判员设置(即授权),当抢答使能信号有效时(高电平),允许抢答。同时设置倒计时信号,当倒计时信号为高电平时,进行20 秒倒计时;为低电平时,倒计时单元被关闭。复位后,裁判员授权抢答允许信号,抢答者开始抢答,同时倒计时单元进行20 s 计时,参赛者们按下抢答开关按键,抢答器能判断出第一抢答者(将抢答允许信号清零)并显示该组组号,同时使得其他组参赛者的抢答按键无效。在倒计时阶段,若没有人抢答,报警模块就会发出警示信号。抢答器有复位清零功能。

1 抢答器总体设计方案

1.1 抢答器总体方案设计

本设计主要实现判断第一抢答者,抢答倒计时和显示组号等功能。其总体设计框图如图1。软件部分则通过QuartusII9.0 软件,用VHDL 程序设计实现多路抢答器的主要功能。

图1 抢答器总体设计

1.2 FPGA 芯片EP2C35F672C8 资源简介

主芯片采用Altera 公司推出的Cyclone II 系列的FPGA EP2C35F672C8,该器件有672 个引脚,片上逻辑宏单元(LE)共有33 216 个,存储容量为4 KB 的RAM 有105 个,片上的18×18 硬件乘法器共有35、高性能锁相环时钟发生器有4 个,用户自定义I/O 引脚多达475 个[5]。

2 抢答器的顶层电路设计和主要模块设计

2.1 抢答器顶层电路设计

根据设计要求,该系统的顶层电路如图2所示。

该抢答器主要由以下电路模块组成:抢答判别电路、分频电路、组别判断电路、扫描信号产生电路、数码管位信号与段信号匹配电路、倒计时电路和译码显示电路。其中:组别判断电路和抢答判别电路是关键模块,前者是对每一位参赛者的组号进行判断,后者主要完成对最快抢答者的判断功能;倒计时电路对抢答进行20 s 倒计时;分频电路是为了得到1 Hz 的时钟信号;扫描信号产生电路产生的扫描信号除了能作为多位数码管显示的位选信号外还能作为多位数码管显示相应位的段码扫描信号;数码管位信号与段信号匹配电路是将多位七段数码管相应位位信号和段信号进行匹配以正确显示组号和倒计时时间信号;译码显示电路则是显示抢答器的状态。

抢答器的输入信号CLK、CLR 和EN,分别是时钟、复位、使能信号;参赛者抢答按键开关信号A0、A1、B0、B1、C0、C1、D0、D1;输出信号有:报警信号M、数码管的LED 位信号和LED 段信号。

抢答器的工作流程:先将抢答使能信号EN和倒计时开关信号RST 置于高电平,然后进行复位,此时参赛者可以开始进行抢答,同时倒计时数码管显示从19 开始进行倒计时,A、B、C、D 四组抢答者谁最先按下抢答按键,谁抢答成功,同时,抢答成功者面前的指示灯被点亮,而且译码显示电路模块显示抢答成功者的参赛编号、主持人设置倒计时开关信号为低电平,禁止报警;如果倒计时结束时没有人抢答,则发出报警信号。

2.2 主要模块设计

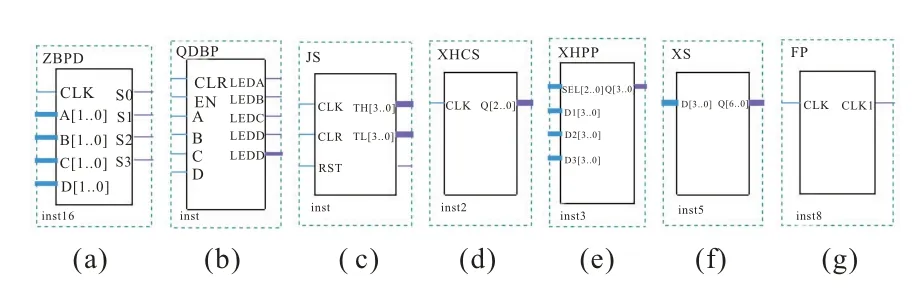

该抢答器由组别判断模块、倒计时模块、抢答判别模块、数码管位信号与段信号匹配模块、扫描信号产生模块、译码显示模块和分频模块组成如图3。本设计使用VHDL 语言编程。

图3 各模块逻辑符号组别判断模块(a)组别判别;(b)抢答判别;(c)倒计时;(d)扫描信号产生;(e)数码管位信号与段信号匹配;(f)译码显示;(g)分频

2.2.1 组别判断模块设计

组别判断模块的主要作用是对每一位参赛者的组号进行判断。其模块符号如图3(a)。该模块输入信号有时钟信号CLK(1 KHz)、四组按键A[1,0]、B[1,0]、C[1,0]、D[1,0],输出信号为每一组的抢答信号S0、S1、S2、S3。

2.2.2 抢答判别模块

抢答判别模块具有第一抢答信号的鉴别和锁存功能,在进行锁存的同时,对抢答状态进行显示。其模块符号如图3(b)。输入信号有参赛者抢答按键开关信号、清零信号CLR、EN 使能信号,各组抢答状态显示信号LEDA、LEDB、LEDC、LEDD 和抢答成功组别编号信号Q[3,…,0]为输出信号。

系统复位后,当使能信号EN 为高电平时,系统根据选手按下抢答按钮的先后顺序选择最先抢答信号,其对应的抢答状态显示信号LEDALEDD 输出高电平,抢答成功组别编号由信号Q[3,…,0]输出,并锁存抢答器此时的状态,使其他选手的抢答按键无效直到清零信号有效为止。在每一轮抢答开始之前,都要使用复位清零信号CLR,使电路恢复初始状态。

2.2.3 倒计时模块

倒计时模块的主要作用是进行抢答倒计时。系统复位后,当倒计时开关信号为高电平时,倒计时数码管从19 开始以秒为单位进行倒计时,当有选手抢答时,主持人给出停止计时信号;如果倒计时结束后还无人抢答,倒计时模块会输出一个高电平使LED 灯亮。其模块符号如3(c)所示。时钟信号CLK(1 Hz)、清零信号CLR、倒计时停止信号RST 这三个信号为输入信号;TH[3,…,0]、TL[3,…,0]、LED 灯报警信号M 为输出信号,它们分别是计时器高位信号、计时器低位信号、倒计时报警信号。

2.2.4 扫描信号产生模块

扫描信号产生模块的主要作用是产生扫描信号,它不仅能作为多位数码管显示的位选信号,还能作为数码管显示相应位的段码扫描信号。其模块符号如3(d)所示。时钟信号CLK(1 KHz)是输入信号,Q[2,1,0]是输出信号,该信号是作为基于时钟的扫描信号使用。

2.2.5 数码管位信号与段信号匹配模块

由于该系统需要显示一位选手编号和两位倒计时时间信号,要正确显示这些数据,需要对多位七段数码管相应显示位的位信号与段信号进行匹配。其模块符号如3(e)所示。该模块的输入信号有扫描信号SEL[2,…,0]、抢答选手编号的BCD码D3[3,…,0]、倒计时模块输出的时间信号的高位和低位的BCD 码D1[3,…,0]和D2[3,…,0];输出信号为显示信号Q[3,…,0]。

2.2.6 译码显示模块

译码显示模块的实质是一个LED 共阳极显示模块的译码器,其作用是将输入的BCD 码转换成可供数码管直接显示用的七段码。其模块符号如3(f)所示。其中D[3,…,0]为输入的BCD 码,Q[6,…,0]为输出的七段码,它将输入的BCD 码译码显示为十进制数字的0~9。

2.2.7 分频模块

由于倒计时模块需要1 Hz 的时钟信号,而FPGA EP2C35F672C8 的时钟信号为50MHz,所以需要分频来得到1 Hz 的时钟信号。其模块符号如3(g)所示。

3 抢答器的设计实现与仿真分析

根据抢答器的工作原理及其顶层电路,各模块的设计实现与仿真结果与理论一致。以下仅对组别判断模块、抢答判别模块及顶层电路的的组别判别模块的仿真结果进行分析。

3.1 组别判断模块的仿真

组别判断模块的波形仿真如图4 所示。抢答信号为低电平有效。图中只有当同组的两个参赛者都输出高电平时,该组的输出信号才为高电平。

图4 组别判断模块的仿真波形

3.2 抢答判别模块的仿真

其波形仿真如图5 所示。从图中可看出,A组最先抢答,LEDA 输出高电平,同时输出信号为“001”。这说明该模块能对第一抢答信号进行鉴别并锁存该信号,同时与抢答成功者组号相对应的LED 灯会被点亮以发出提示。

图5 抢答判别模块的仿真波形

由图中可看出,当CLR 信号无效和RST 为高电平时,倒计时模块从19 开始进行倒计时,倒计时为0 时,发出一个高电平信号报警。

3.3 顶层电路的仿真

抢答器顶层电路波形仿真如图6 所示。从图中可看出,A 组最先抢答,系统正确判断出了第一抢答者的组号,并显示A 组的LED 灯亮。

图6 抢答器顶层电路仿真波形

4 小结

本文通过集成开发环境QUARTUSII9.0 和硬件描述语言VHDL 设计并实现了八人四组抢答器。首先采用硬件描述语言程序设计各模块并生成逻辑符号图,然后按照抢答器的工作原理,将逻辑符号图级联构成抢答器的顶层电路,最后通过仿真、下载验证目标文件。实验结果表明,该抢答器运行效果良好,可在各类竞赛性质的场合推广应用,能够消除人眼误差、正确判断最先抢答者。