晶振引发的EMC辐射发射超标分析及整改方案设计概述

大连云动力科技有限公司 辽宁 大连 116023

1 EMC辐射实验现象描述

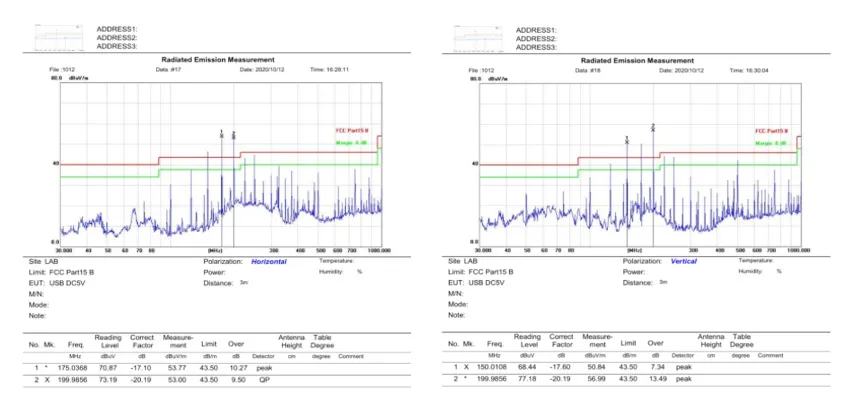

某产品进行EMC辐射发射测试,产品采用DC5V供电,该产品的辐射发射水平和垂直两种测试的频谱如下图所示,在150M、175M、199M处严重超标,不符合认证要求。

图1 发射水平和垂直两种测试的频谱

2 辐射发射超标原因分析

根据实验报告可知,测试超标的频点大致为25的倍数,有很强的规律性,为寻找发射源提供了很好的线索。进一步分析可知,PCB上刚好有25M无源晶振作为W5500的外置晶振,所以极有可能是此处引起的超标。EMC三要素是干扰源,被干扰对象和干扰路径。结合本次实验报告显示出的频点的周期性,本次整改可以从源头修正,即优化晶振的布局和走线[1]。

图2 PCB双面板

图2这一版本PCB是双面板,晶振与其对应的芯片W5500不在一个层面,XIN和XOUT两个引脚引出后打了过孔,晶振时钟走线过于曲折,与芯片距离比较远,可能会产生很多不必要的高次谐波,甚至形成发射天线。尽管PCB形状和大小都有限制,但是晶振作为时钟,属于关键信号线,在布局上一定要从优安排。

另外此版本晶振的位置离PCB板边缘很近,晶振放在电路板边缘,则会造成晶振的回流地面积不够充裕,从而引发EMC问题。

3 EMC整改措施

优化晶振的走线,降低干扰,通常有如下做法:

(1)晶振自身的屏蔽性能要好,晶振接地。

(2)晶振XIN和XOUT尽可能靠近IC引脚,走线尽可能短,与其他信号线保持一定距离,最好进行包地。

(3)晶振底下最好不要走线,尤其需要避免高速信号线。

本次整改首先从双面板改为四层板,四层板中的电源和地各自独立一层,完整的地平面作为参考平面,这样做有一定的屏蔽作用。对于高频、高速、时钟这类较为关键的信号线,它们与地线之间的距离仅为PCB板的层间距离,电流也会在信号线正下方的地线上流动,信号环路面积达到最小,从而减小辐射。

晶振和芯片放在同一层面,尽可能靠近芯片引脚,减小芯片XIN和XOUT引脚到晶振两个对应引脚的走线长度,并进行包地处理,以免将干扰耦合到其他信号线,晶振的地包围单点接到地层,详见图3。

5V进电端和5V转3.3V后的输出端加去耦电容和磁珠,使电源纹波控制在5%以内,增强电源的稳定性和抗干扰性,减少杂波。W5500芯片的VDD和AVDD与3.3V之间用120R的磁珠隔开,减小电源杂波对芯片的干扰。元器件更换为同参数的屏蔽性能更好的晶振。

图3 晶振走线示意图

4 整改后测试结果

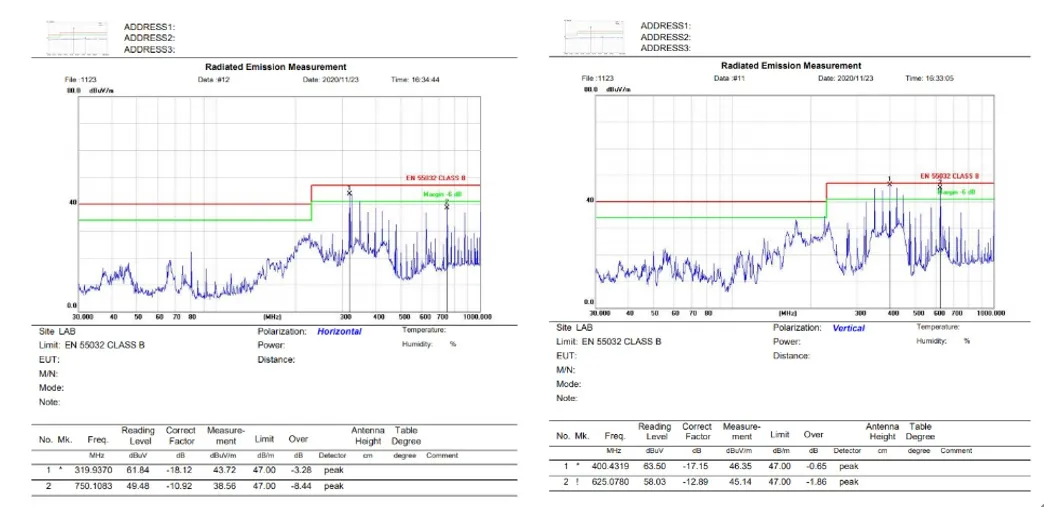

整改后产品测试结果如图4所示,最小余量为0.65,测试通过。

图4 整改后发射水平和垂直两种测试的频谱

5 加深研究与分析

PCB是元器件和电子电路的连接桥梁,PCB设计的好坏会直接影响产品的抗干扰能力。PCB尺寸确定后,特殊元器件应该优先排布,并进行合理的设计,避免产生诸多噪声进而引起EMC问题。

其次是地面完整性问题。辐射发射超标的双面板版本中,晶振并没有进行包地处理,PCB板元器件较多,元器件排布比较紧密,所以也没有条件形成完整的地平面,晶振的走线也没有达到最短,形成的噪声耦合到旁边的信号线也会通过连接器带出PCB,导致辐射超标。

最后就是晶振自身,在成本和电参数满足的前提下,尽可能使用上升时间长的时钟,因为上升时间短的时钟谐波能量高于上升时间长的时钟,上升时间长的时钟可以减少一些谐波的干扰。另外,频率低的时钟谐波成分低于频率高的时钟,在系统可以正常工作的前提下,尽可能选择频率低的时钟。

6 结束语

EMC辐射发射晶振倍频超标很难一次性处理好,所以项目前期需要格外重视晶振的布局、走线,并且尽可能的预留可以降干扰的元器件,以免出现问题后改板打样,浪费时间。其次选择合适的可靠的晶振也尤为重要,如果EMC要求很严格,在成本允许的前提下,尽可能选择大厂生产的晶振,并且了解晶振自身的检测报告。在条件允许的情况下,项目前期最好进行相关测试。

以上为本次晶振引发EMC辐射发射问题的分析与整改,通过更改PCB走线和布局,通过了产品的相关认证。