高速PCB版的电源布线设计

马秀梅 南京熊猫通信科技有限公司 纪雪岚 南京熊猫电子科技发展有限公司 黄玉玲 南京熊猫通信科技有限公司

当今电子技术发展日新月异,大规模超大规模集成电路越来越多地应用到通用系统中,一百兆赫兹以上的系统已随处可见,Die、BGA、MCM这些体积小、管脚数已达数百甚至上千的封装形式也已越来越多地应用到各类高速超高速电子系统中。这样就带来了一个问题,即电子设计的体积减小导致电路的布局布线密度变大,而信号的频率还在提高,使得如何处理高速信号问题成为一 个设计能否成功的关键因素。

文中介绍了 PCB板高速元器件的旁路电容布局及布线设计方案,同时阐述了高速信号线的线间距、分支走线长度、拐角规则等几个方面的优化设计方案。

1.高速元器件旁路电容布局布线设计

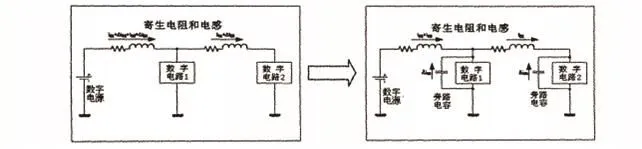

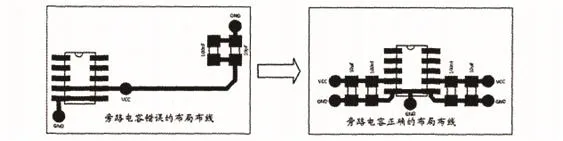

数字电路从电源获取的电流通常是不连续的,一般高频元器件消耗电流比较大。在 PCB布局布线时,如果把电源走线布的比较长,那么在峰值电流时比较容易引入高频 EMI噪声,高频噪声极有可能影响其他信号,从而造成整个系统不能可靠的工作。电源的布线线路自身存在一定的寄生电阻和电感,高频噪声易通过电源耦合进其他数字电路和模拟电路.通常,在进行理论上的分析和计算时,都是把电源进行理想化,即电源无内阻,也无寄生阻抗。如果用一个3.3V的电压源对PCB .上的元件共电,那么无论距离电源的远近,各个元件都应工作在3.3V,且没有噪声。然而在实际的设计工作中,由于PCB.上的IC和输入人输出的信号都工作在高频下,电场和磁场的相互转化,必不可免的给电源引人了噪声,如图1、图2所示。同时由于PCB板上的走线非常的细,又产生了由于线路阻抗引起的压降,使远离电压源的器件工作电压小于电源电压。此外,寄生电感会减少PCB线条所能承载的最大电流,造成电压到达电路时产生一定的压降。因此有必要在数字电路的电压输入引脚放置一定数量和特定容值的旁路电容,以减小压降,增加电源线路所能承载的最大电流。加旁路电容前和加旁路电容后电路工作模型参见图 1。

添加旁路电流前和添加旁路电流后电路的工作模型

尽可能在每个集成电路的每个电源引脚处放置独立的旁路电容,如果电源引脚比较集中,可以共享一个或-簇旁路电容。旁路电容尽可能靠近电源引脚,且应该尽可能的增加走线的宽度,并缩短走线长度,电流的流向也应该考虑。通常靠近电源走线放置-一个过孔,该过孔应该满足能够通过峰值电流的要求,地平面也应放置合适数量的过孔。旁路电容布局和布线参见图2。通常放置一大一小两个电容(例如100nF + 10μF) ,在布局时小容量电容应更靠近电路的电源引脚。

2.高速信号线设计

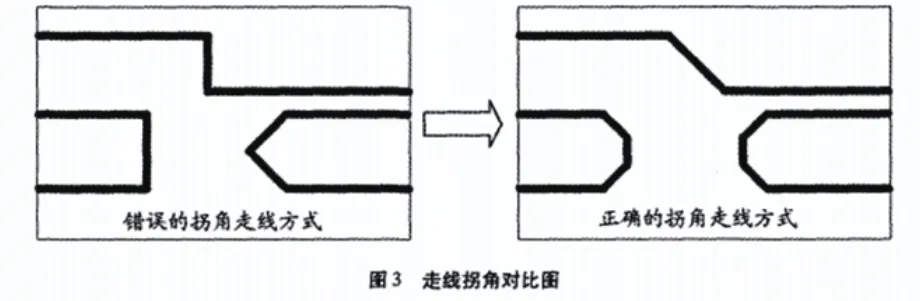

2.1 走线拐角

在高速电路布线时,走线的拐角非常关键,通常使用1350并非90°或45°,参见图3。直角走线- -般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理,上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不仅是直角走线,钝角锐角走线都可能造成阻抗变化。直角走线对信号的影响主要体现在三个方面:一是拐角等效为传输线上的容性负载,减缓上升时间;二是阻抗不连续会造成信号的反射”;三是直角尖端产生的EMI。

蛇形走线时除了要关注线宽,更要注意走线之间的间距,具体间距要求和拐角要求参见图4。

平行走线间距至少要4倍线宽,拐角各线段至少要1.5倍线宽。这些规则在很多CAD软件中是不做DRCs检查的.因此需要布线时严格检查。

2.2 走线间距

串扰是指两条信号线之间的耦合、信号线之间的互感和互容引起线上噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有-定的影响。串扰可能是数据进行高速传输中最重要的一个因素。它是一个信号对另外-一个信号耦合所产生的一种不受欢迎的能量值,这个能量值可能会导致数据传输的丢失和传输的错误。

在高速走线间,适当增加线问距十分必要,将很大程度上减少串扰(2。若因为机械结构或者元器件布局的影响,无法全程保持合适的线间距,也应让瓶颈影响最小,图5所示为一个线间距布线策略。

2.3 走线分支

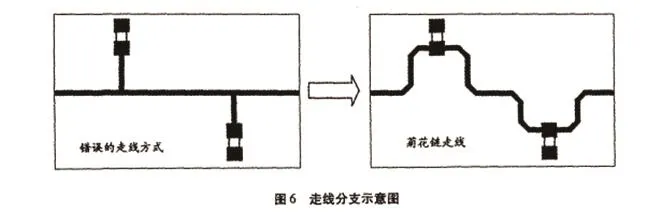

分支走线通常扮演一个天线的角色,会产生发射,因此布线时必须严格遵守EMC准则,以免对信号完整性产生影响。通常在高速信号走线上加_上拉或下拉电阻,应根据不同的连接方式选择不同的分支走线策略,如图6所示为菊花链型走线示意图(3。通常分支走线长度应小于波长的1/10。

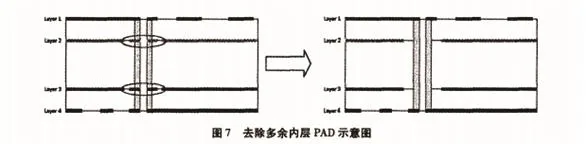

过孔也可以看作信号的一个分支,比如在一个六层板的布线中,信号从第一层过渡到第三层,因为是通孔,相当于存在一个贯穿六层的分支走线。解决因为过孔产生影响的唯一办法是减少过孔的数量。尤其是连通地、电源平面的过孔,在无法避免的情况下,应删除无连接层的PAD,具体示意可参见图7。

在设计高速PCB板时,对电源布局布线的处理应尽量遵循下面一- 些规则:

(1)有条件的情况下,尽量采用单独的电源层和地层进行供电。采用电源网络总线时,网孔越多越好,形成许多嵌套的网孔,同时总线要尽量的宽,以达到均衡电流,降低噪声的目的;

(2)电源的走线不能中间细两头粗,以免在上面产生过大的压降。走线不能突然拐弯,拐弯要采用大于90%的钝角,最好采用圆弧形走线,电源的过孔要比普通的大些。有条件的话,在过孔处加滤波电容;

(3)对于那些特别容易产生 声的部分用地线包围起来,以免产生的噪声耦合人电压。

3.去耦电容的选取与放置

PCB设计的常规做法之一是在电路板的各个关键部位配置适当的去耦电容。

去耦电容的一般配置原则是:

1)电源输入端跨接10~ 100uf的电解电容。如有可能,接一百微伏以上的更好。

2)电路板_上每个集成电路的电源端都要对地并接一个a01μF~Q1uF高频电容,以减小集成电路对电源的影响,如遇电路板空隙不够,可每4~8个集成电路布置一个1~10pF的电容。

3)对于抗干扰[6]能力弱关断时电流变化大的元件和存储元器件,应该在集成电路电源和地线之间接入去耦电容。

4)电容的引线不要太长,特别是高频旁路电容不能带引线。

结束语:经过多个产品验证,使用本文设计方案和优化方案有效提高了产品性能和可靠性,从而缩短了调试和研发周期,为产品的顺利生产带来了极大便利。