基于PPLN波导的全光普通4线2线编码器设计

童 艳

(沈阳城市建设学院 辽宁 沈阳 110167)

1 引言

随着各种宽带业务对网络速率和带宽的要求越来越高,通信网络需要采用一些技术来进一步提高网络的速率和带宽。光纤通信作为现代社会的主要网络,提供了大带宽和高速率的网络服务。而由于技术的限制,目前光网络某些网络节点处还需要将光信号转换成电信号,对电信号进行处理,再将电信号转换成光信号耦合进光纤,而正因为要进行电信号处理,所以目前光网络的这些节点的信号处理速度不会太快,从而影响了光网络的整体速率。而全光网的每个网络节点处都只存在光信号的处理,大大提高了处理速度,因此全光网是光网络的发现目标。

全光信号处理是实现全光网的关键技术,包括全光波长变换、全光开关、全光逻辑信号处理等等,其中全光逻辑信号处理是全光信号处理的很重要的技术。由于PPLN(周期性极化铌酸锂)波导这种非线性光学材料的优点,目前很多全光逻辑信号处理器都是用PPLN波导来实现的,比如基于PPLN波导的全光数据选择器[1]、全光译码器[2]、全光数值比较器[3]、全光4线-2线优先编码器[4]等,且这些器件通过仿真和数值分析,性能良好。虽然目前已实现的全光逻辑信号处理器件有不少,但要完全实现全光网,这些全光逻辑信号处理器远远不够,因此还需要继续研究新型全光逻辑信号处理器的设计及实现方案。本文就是要研究基于PPLN波导的新型全光逻辑信号处理器,提出新型全光逻辑信号处理器的设计及实现方案。

2 PPLN波导全光逻辑运算原理

基于PPLN波导的全光逻辑信号处理器需要根据PPLN波导的全光逻辑运算原理来进行设计。如图1所示为PPLN波导全光逻辑运算原理图,其中A、B为两路速率和峰值功率都相同的二进制输入脉冲信号光,P为连续抽运光,由于PPLN波导的和频+差频效应,A、B信号光会在PPLN波导中经历和频过程,产生的和频光又会与抽运光P进行差频过程,最终PPLN波导输出两路和频剩余光(分别是信号光A和B的和频剩余光波)和一路差频输出光。

图1 PPLN波导全光逻辑运算原理

下面分析一下PPLN波导的这三路输出光波的逻辑关系式。假设某一时隙内A、B信号光的逻辑分别为0、0或1、0或0、1,则A、B信号光在PPLN波导中不会发生和频效应,从而也不会有差频效应的产生,输出就不会有差频光波,此时PPLN波导的两路输出和频剩余光还是原来的A、B输入信号光。假设某一时隙内A、B信号光的逻辑都为1,那么A、B信号光会在PPLN波导中经历和频过程,产生的和频光再与抽运光P进行差频,输出差频光,一般在抽运光的差频作用下,和频过程能充分进行,因此此时PPLN波导的两路输出和频剩余光功率为零,输出存在差频光波。由以上描述可见,PPLN波导的输出光波中的A信号光的和频剩余光的逻辑表达式为AB-,PPLN波导的输出光波中的B信号光的和频剩余光的逻辑表达式为A-B,PPLN波导的输出光波中的差频光的逻辑表达式为AB。

3 全光普通4线-2线编码器设计方案

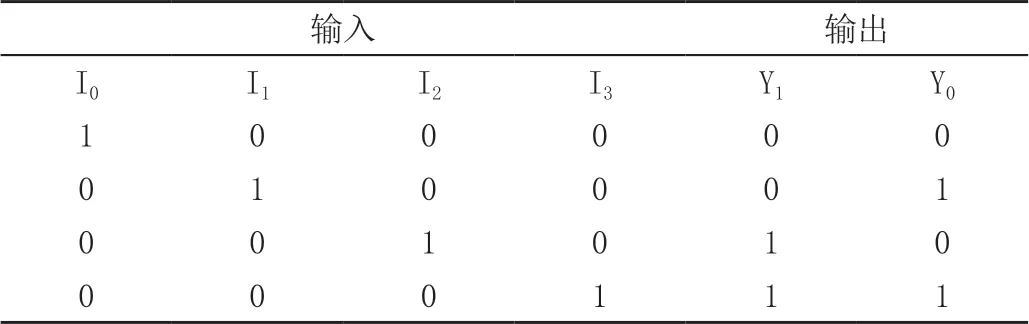

普通4线-2线编码器属于编码器的一种,有4路二进制输入信号,2路二进制输出信号。假设4路输入信号分别是I0、I1、I2、I3,2路输出信号分别是Y1、Y0,那么普通4线-2线编码器的真值表如表1所示,当I0、I1、I2、I3分别是1000时,Y1、Y0为00;当I0、I1、I2、I3分别是0100时,Y1、Y0为01,当I0、I1、I2、I3分别是0010时,Y1、Y0为10;当I0、I1、I2、I3分别是0001时,Y1、Y0为11。由普通4线-2线编码器的输入与输出之间的关系,可以得出Y1和Y0的逻辑表达式为:Y1=I2+I3,Y0=I1+I3。由图1所示的PPLN波导的全光逻辑运算原理,可知如果要用PPLN波导来实现Y1和Y0的逻辑表达式,就必须将Y1和Y0的逻辑表达式的形式变换为与非、或者与非或的形式,经过分析,将Y1和Y0的逻辑表达式变换为:此表达式只含有与非逻辑运算。

表1 普通4线-2线编码器真值表

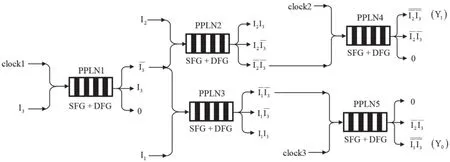

由Y1和Y0的逻辑表达式的变换形式,可知只利用单个PPLN波导是不能实现Y1和Y0的逻辑表达式的。由申静、秦晋在2018年5月发表的“基于PPLN波导的全光数据选择器的设计与研究”期刊论文中的图3可知,Y1和Y0的逻辑表达式中的输入信号I1、I2、I3的非运算可以利用PPLN波导作逻辑“非”运算的基本原理来实现。因为Y1和Y0的逻辑表达式中都有输入信号I3,所以可以先利用PPLN波导作逻辑“非”运算的原理来实现然后再利用PPLN波导级联的方式进一步实现Y1和Y0的逻辑表达式。在利用PPLN波导级联的方式来实现普通4线-2线编码器的逻辑表达式时,需要考虑PPLN波导级联的条件,即各级PPLN波导的输入信号的速率和峰值功率都必须相同,在这种条件下,利用PPLN波导级联实现Y1和Y0的逻辑表达式的设计方案如图2所示。

图2 基于PPLN波导的全光普通4线-2线编码器的设计方案

图2基于PPLN波导的全光普通4线-2线编码器的设计方案,一共采用了5个PPLN波导,为了简略,图中省略了每个PPLN波导的抽运光。图中clock1、clock2、clock3均为速率和峰值功率与I1、I2、I3相同的全1脉冲信号。其中用PPLN1实现逻辑,输入速率和峰值功率都相同的clock1和I3二进制脉冲信号,由PPLN1波导的逻辑运算原理,其输出为、I3、0。由于是输入信号clock1的和频剩余光波因此它与I1、I2的速率和峰值功率相同,可以作为PPLN2和PPLN3的输入信号。PPLN2输入I2和,其的和频剩余光波由于速率与峰值功率与clock2相同,因此可以继续作为PPLN4的输入信号。PPLN3输入I1和,其的和频剩余光波由于速率与峰值功率与clock3相同,因此可以继续作为PPLN5的输入信号。PPLN4输入clock2和,其clock2的和频剩余光波即为普通4线-2线编码器的输出Y1的逻辑表达式。PPLN5输入clock3和其clock3的和频剩余光波即为普通4线-2线编码器的输出Y0的逻辑表达式。因此图2所示的PPLN1、PPLN2、PPLN4三个波导级联能实现普通4线-2线编码器的输出Y1的逻辑表达式,PPLN1、PPLN3、PPLN5三个波导级联能实现普通4线-2线编码器的输出Y0的逻辑表达式。

3 结语

本文提出了基于PPLN波导的全光普通4线-2线编码器的设计方案。首先在单个PPLN波导逻辑运算原理的基础上,分析并得出了普通4线-2线编码器的两个输出的只含有与非的逻辑表达式。然后根据两个输出的逻辑表达式,分析出了要实现这样的逻辑表达式,就需要利用PPLN波导作逻辑非运算的原理以及利用多个PPLN波导级联的方式。最后一共用5个PPLN波导实现了普通4线-2线编码器的两个输出的逻辑表达式,其中用PPLN1、PPLN2和PPLN4实现了普通4线-2线编码器的高位输出的逻辑表达式,用PPLN1、PPLN3和PPLN5实现了普通4线-2线编码器的低位输出的逻辑表达式。此设计方案满足PPLN波导的级联条件,能实现普通4线-2线编码器的逻辑功能,且所有信号处理均在光域上进行,实现了全光的普通4线-2线编码器。此设计方案能为基于PPLN波导的全光普通4线-2线编码器以及其他全光逻辑信号处理器件的研发提供参考。后续将对此设计方案进行MATLAB数值计算及仿真,分析该方案的性能。