CAN总线载波侦听点位测量方法研究

肖彬

(航空工业北京长城计量测试技术研究所,北京 100095)

0 引言

CAN数据总线是国际上应用最广泛的现场总线之一,得益于其高可靠性、高容错性以及强实时性等优势,在要求严苛的航空、航天、汽车与工业现场等领域已得到大量应用[1-3]。该总线具备空闲侦听、冲突检测与逐位仲裁等核心功能,可以实现多主节点组网,并大幅度提升传输效率及容错性,同时也使高优先级消息无延时占用总线传输[4-7]。

目前,CAN总线的上述核心功能均以“载波侦听”技术为基础,该技术的可靠性会直接影响各节点对总线信号的判断与处理,从而关系到整个网络系统的可靠性。载波侦听采样点(以下简称“采样点”)的位置由不同供应商根据不同的应用场景进行设定[8],在高可靠性要求的应用领域中,采样点的位置设置不当可能导致节点对总线信号误判,造成通讯实时性降低或节点失效,甚至使整个网络系统瘫痪[9-10]。各领域规范中,对采样点位提出了要求或建议,并指出网络中各节点的采样点位容差越小,网络的最大可能长度越长,网络传输越稳定。

汽车及飞机机载系统中电磁环境非常恶劣,网络系统会受到高强辐射场(HIRF)、单粒子效应以及逆变器、电动机、充电机等大功率设备的电磁辐射[9-10],网络信号质量会受到不同程度的影响。

如图1所示,由逆变器干扰测试数据可以看出,失真或畸变的差分信号在电平跳变时刻的信号干扰最为严重,随着电平的状态保持而趋于稳定。在干扰信号传输中,如果采样点位靠近跳变边沿,则很可能采集到失真波形,造成对传输信号的错误判断,导致数据传输失败。

图1 逆变器对CAN数据总线信号的干扰Fig.1 Interference of inverter to CAN bus signal

因此,在节点接入总线网络前,有必要对其采样点位进行测试,利用测试数据对其采样点位进行修正,修正后的节点接入总线网络可大幅度提高网络系统可靠性与安全性。

1 测量原理

1.1 载波侦听采样点

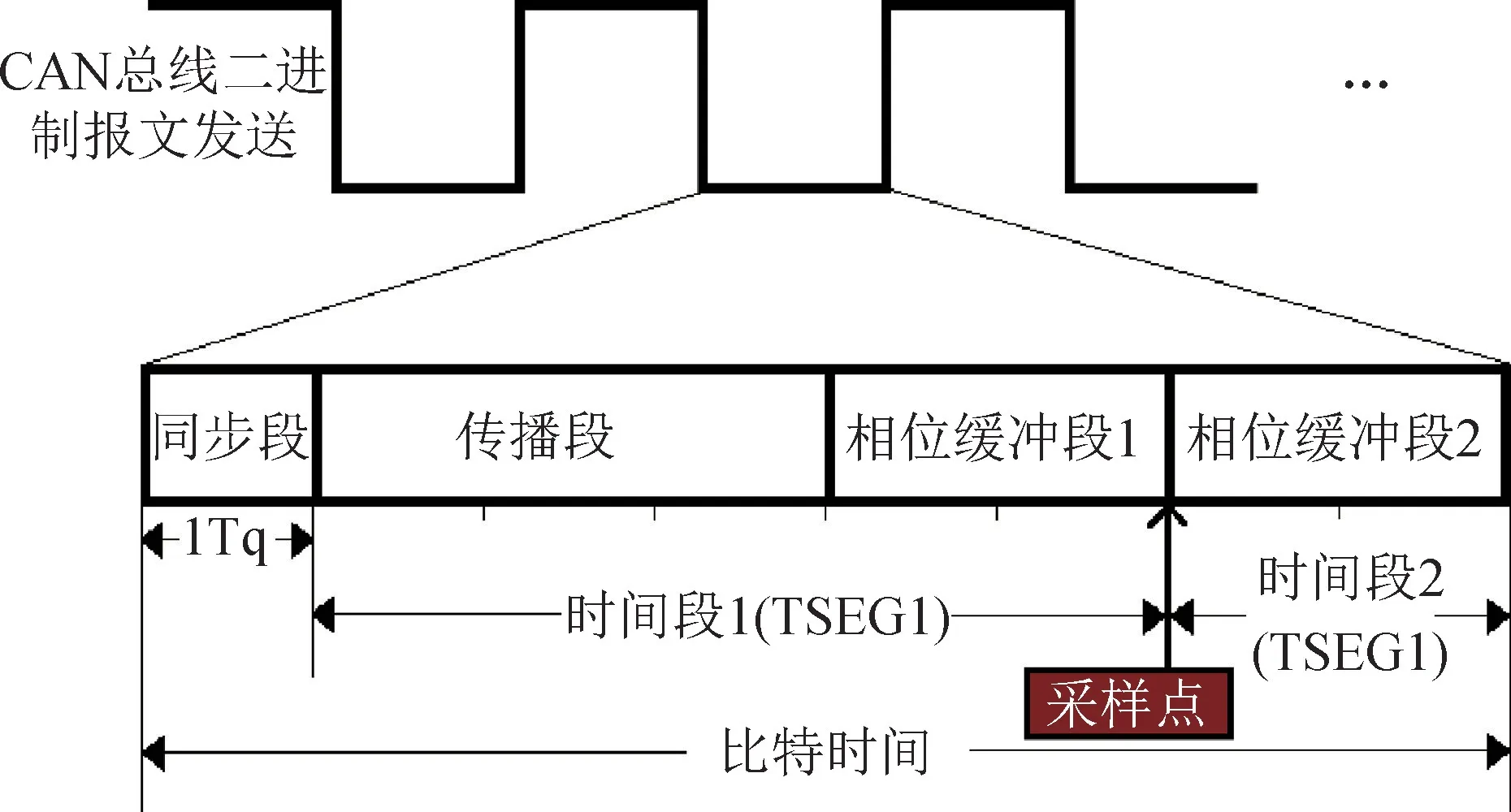

CAN节点控制器在发送数据过程中为每比特时间设立一个载波侦听采样点,如图2所示,对传输网络物理层信号进行采样确认,如果采集帧听状态与自身输出状态不一致,表示该节点与总线上其他节点的传输发生冲突,该节点将执行相应处理措施[11]。

图2 比特时间组成及采样点定义Fig.2 Bit time composition and sampling point definition

CAN协议定义一个“比特时间”分为同步段、传播段、相位缓冲段1和相位缓冲段2,采样点位于相位缓冲段1末端,各段以不同数量的Tq构成[11]。由于各段位包含的Tq数量可按协议规定范围调整,因此载波侦听采样点位置也会随之变化。

1.2 错误检测机制

在CAN总线协议中,数据帧传输过程伴有五种错误检测机制,包括:位错误、ACK错误、填充错误、CRC错误与格式错误[11],如表1所示。

表1 CAN协议数据帧错误检测机制及作用范围Tab.1 Error detection mechanism and scope of CAN protocol data frame

在节点发送端或接收端检测到错误后,各节点会以发送“错误帧(连续6比特相同信号状态)”的方式通知总线上其他节点,并且发送端在错误界定结束后将重新发送数据帧。

1.3 错误注入

采样点位的测试方法将以错误注入的形式进行,在CAN总线错误注入类型选取时,对错误处理判断的复杂程度以及被测设备配置的难易度进行综合考虑[11-14],最终选择利用CRC校验错误及相关处理机制对采样点位进行测试试验。

在CAN总线物理层协议特性中,逻辑状态“0”优先级高于逻辑“1”,因此在总线网络中,如果有任何节点将总线电平转变为逻辑“0”时,其他节点将无法改变总线状态[11]。

图3(a)是一个正确数据的传输过程,节点1和节点2在同一个网络中,节点1发送一帧正确数据,并且在ACK槽位保留逻辑“1”电平(如蓝色发送信号),节点2监测到总线网络中到来的数据信号,判断数据帧正确后,在该数据的ACK槽位向总线网络中发送一个逻辑“0”的反馈信号(如绿色发送信号与红色总线网络信号),同时节点1从总线网络中帧听到ACK槽位的反馈信号(如蓝色接收信号),则节点1认为数据发送成功。如图3(b)所示,如果节点1发送含有CRC错误的数据帧,节点2在ACK槽位将不会做出反馈。

图3 CAN数据帧ACK槽位信号交互示意图Fig.3 CAN frame ACK slot signal interaction diagram

利用以上特性及处理机制,如图4所示,向被测节点连续发送同一数据帧,并在此数据帧中注入错误信号,该错误信号物理波形在该比特时间的占空比每帧递增0.1%,直至完全填充该位,并且在数据帧CRC校验段保持不变的正确数据帧CRC校验值。

图4 比特时间占空比错误注入示意图Fig.4 Schematic of bit time duty cycle error injection

连续发送比特时间占空比逐帧递增的错误信号,在注入的错误信号未触及被测端采样点位置时,被测端依然采集到正确的信号电平并给予反馈信号,当错误信号波形触及采样点位置时,被测端采样点采集到错误电平并记录错误的逻辑数据。错误数据处于CRC作用域中,计算得到的CRC校验值将与数据帧内正确的CRC校验值不符,造成CRC校验错误,从而导致ACK槽位无反馈消息发出。利用对ACK槽位电平状态的判断,可以确定被测端是否接收到正确数据,并通过正确发送的数据帧数量得到采样点在比特时间中的位置占比。

1.4 测试点选取

由于CAN协议中每一数据帧起始(SOF)时,都将进行信号的“硬同步”,即所有CAN节点都将在此时统一各自的信号起始时基[15],在数据帧的随后位中,每当数据波形由逻辑“1”向逻辑“0”跳变,并且该跳变落在同步段之外,就会引起一次“重同步”[16]。如图2所示,CAN节点会通过延长“TSEG1”或缩短“TESG2”使后续的位数据获得同步[17-18],而相位缓冲段的改变,会使采样点位也随之改变。如果测试时选择的数据位经过“重同步”处理,测试结果将不是采样点的实际设置值。因此通过向起始位(SOF)后一位注入错误帧的方式进行测试,可以有效避免CAN协议中“重同步”带来的影响。

2 测量方法

2.1 依据及指标

CAN总线在航空领域遵循[12],其中明确指出采样点位不应小于比特时间的75%。汽车工业[13-14]也对采样点位提出建议(建议其尽量接近比特时间的87.5%且不超过90%),并且相关标准注明“网络中各节点的采样点位容差越小,网络的最大可能长度越长,网络传输越稳定”[11-14]。相关规范中采样点位范围及建议值如表2所示。

表2 采样点位范围及建议值Tab.2 Sampling point range and recommended value

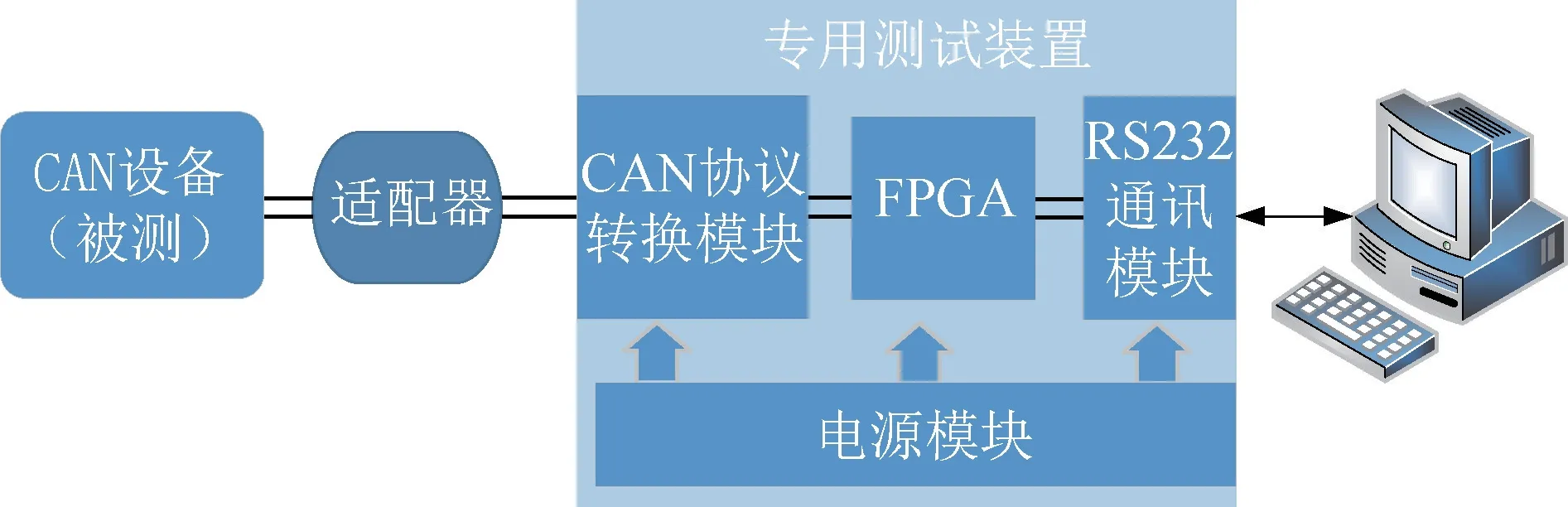

2.2 测试总体方案

研制的CAN总线载波侦听采样点位专用测试装置(以下简称“装置”)如图5所示,其通过上位机进行CAN总线数据帧的设定,随后发送至装置,装置内FPGA生成正确的CAN协议信号波形,并在该正确波形的基础上进行错误注入。而后通过CAN协议电平转换模块将TTL电平信号转换为CAN协议差分信号输出,并监测发出信号ACK槽位的反馈信号,在测试结束后将结果返回至上位机显示并记录。

图5 测试系统组成示意图Fig.5 Schematic diagram of test system composition

CAN协议中规定,在总线网络中,除发送节点外,任何节点在接收到正确数据帧时,都将向总线网络发出反馈信号。利用这一特性,被测节点无需发送任何数据,只需启动后配置相应的传输速率即可完成测试试验。该方法可大幅度减少测试人员的工作量,提高测试的效率。

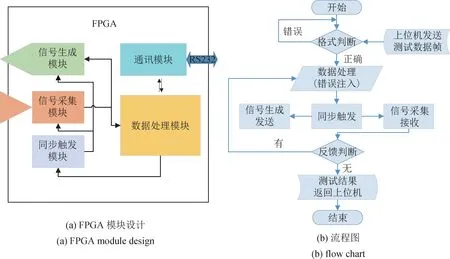

2.3 专用测试装置设计

如图6所示,专用测试装置基于FPGA硬件进行设计研制,采用模块化设计,由信号生成、信号采集、同步触发、数据处理以及通讯接口等模块组成。专用测试装置的工作流程为:通过上位机设置CAN数据帧,并通过串行接口下发至FPGA;利用数据处理模块将数据帧转换为高速输出端口数据队列,并向队列中的每个数据帧注入错误信号,信号生成模块根据数据队列内容发送信号;同时由同步信号触发采集模块进行采集,根据数据帧ACK槽位采集到的反馈信号判断是否发送成功,若成功则继续提高注入错误的占空比并再次发送,若失败则证明已测试到被测CAN设备采样点;完成测试后上传测试数据至上位机并结束测试。

图6 FPGA模块设计及流程图Fig.6 FPGA module design and flow chart

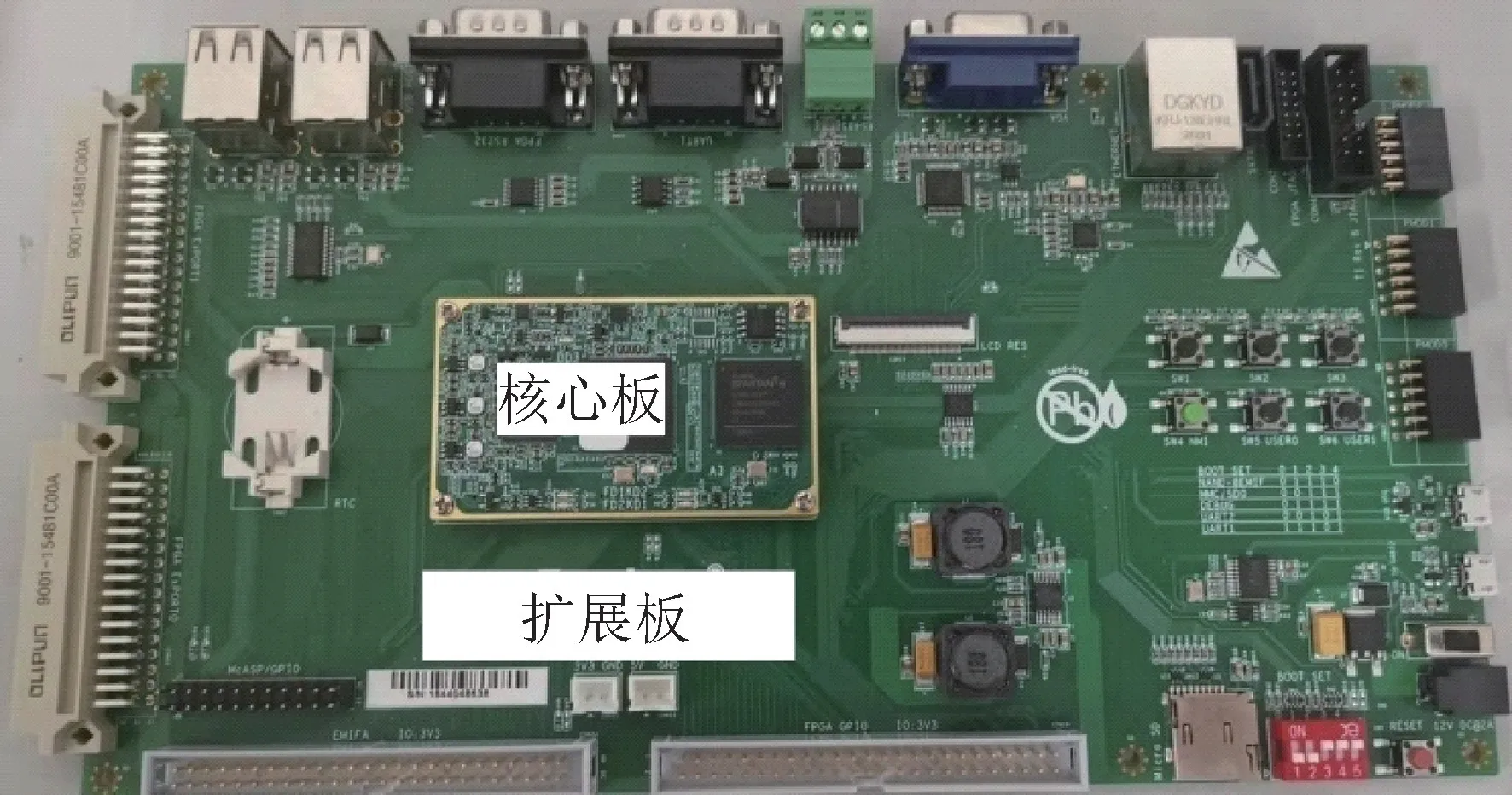

由于在CAN数据总线传输速率为1 Mb/s时,比 特时间占空比分辨力达到0.1%,需要控制准确度优于1 ns,因此需要选用IO控制频率优于1 GHz的主控器件。如图7所示,装置核心部件采用XILINX Spartan-6系列核心板及扩展板进行设计研制,使用高达1050 Mb/s输出频率的高速差分端口,可满足控制准确度设计需求。使用扩展板进行外围电路的设计研制,包括RS232电平转换模块、CAN协议电平转换模块以及电源模块等。

图7 装置核心板及扩展板实物图Fig.7 Core board and expansion board of the device

2.4 装置验证试验

装置的验证试验原理如图8所示,其利用经过校准的标准数字存储示波器,通过标准表法对装置进行验证测试。

图8 测试装置验证原理图Fig.8 Test device validation schematic

验证装置的指标包括输出控制分辨力及输出脉宽准确度。对装置分辨力的要求参考了规范中提出的建议值(即比特时间的87.5%)。因为建议值达到千分位,所以装置控制分辨力应达到0.1%。CAN总线最高传输速率为1 Mb/s时,比特时间为1μs,协议中规定每比特时间的最大Tq数量为25个,因此Tq时间最小为40 ns。因为采样点位于某两个Tq之间,要测量采样点的位置,需要装置输出准确度相对于最小Tq时间满足1/4量传关系,所以要求装置输出准确度优于±5 ns。

验证环境及测试波形如图9所示,测试装置以最高传输速率(1 Mb/s)输出特定数据帧,测试起始位(SOF)与错误注入波形间的脉冲宽度,通过计算得出错误注入波形在该位的占空比。

图9 验证环境与实测波形Fig.9 Verification environment and measured waveform

将装置与被测设备设置为相同传输速率,将被测设备设置为接收状态(不发送数据),并开始采样点位测试,通过示波器测量装置输出信号脉宽,按式(1)进行占空比换算,得到测试结果如表3所示。

表3 验证测试数据结果Tab.3 Verification test data results

式中:Di为设置值i%时的占空比测量值;Ti(μs)为设置值i%时的脉宽测量值;T0(μs)为设置值0%时的脉宽测量值;T100(μs)为设置值100%时的脉宽测量值。

装置输出准确度要求优于±5 ns,在传输速率为1 Mb/s时,可按占空比换算为±0.5%,测试结果表明,实际测试值的最大误差为±0.02%,满足输出准确度要求。并且从前两项数据可以看出,装置满足0.1%的控制分辨力要求,证明专用测试装置的指标均满足测试要求。

2.5 测试试验

利用装置对被测CAN节点设备在特征负载条件下进行采样点位测试,网络负载条件选取为典型状态条件下的负载取值,开展包括网络开路状态、单节点负载(120Ω)与实际组网应用中多节点网络负载(60Ω)条件下的测试试验[4]。将装置与被测设备设置为相同的传输速率,并开始采样点位测试,测试原理如图5所示,测试环境及错误注入信号如图10所示,测试结果如表4所示。

表4 采样点位测试结果Tab.4 Sampling point test results

图10 实测环境及信号波形生成Fig.10 Measurement environment and signal waveform generation

测试结果显示,被测设备采样点位仅在传输速率为1000 kbps与800 kbps时满足要求,其他测试结果不符合建议范围要求。

2.6 负载条件

如图11所示,利用示波器对不同网络负载条件的数据波形进行分析,匹配负载较小时,数据波形传输抖动较大,会导致被测CAN设备在“硬同步”时出现随机偏差,装置与被测设备出现较大的时钟同步误差,因此在实际测试试验中应当匹配的网络负载为60Ω,这样测试数据的可靠性较高。

图11 信号波形边沿余晖对比Fig.11 Comparision of signal waveform edge afterglow

3 结论

通过分析测试试验的结果得出,并非所有CAN总线设备都是按照规范建议值设计研制的,当应用于可靠性需求较高的复杂系统组网时,较大差别的采样点位必然会缩短网络最大理论长度,从而降低整个系统的传输可靠性。随着电子通讯技术的发展,通讯系统网络的复杂程度日益提高,传输可靠性应从各层面不断完善,而首先应在底层建立良好的基础。通过在系统组网前进行采样点位测试,利用测试值调整和统一系统各节点的采样点位,可以使总线物理链路层一致性得到充分保障,也可以使整个系统传输的可靠性更上一个台阶。