一种基于Brokaw 带隙基准上电复位电路的设计

宋爱武, 李富华, 黄祥林, 孙 波

(1.苏州大学, 江苏 苏州 215000; 2.坤元微电子有限公司, 江苏 苏州 215000)

1 引言

上电复位电路是部分数字和混合信号集成电路的重要组成部分,它可以用于控制和初始化模拟和数字电路中的各种节点。 通常在电源斜坡上升期间,输出的POR 信号保持低电平,当电源达到阈值,输出的POR 信号翻转为高电平,电源的阈值可通过特定电路来控制[1-2]。 文献[3]使用一种新结构的POR 电路,利用带隙基准电路的电流动态特性和外加比较器的电路结构设计了性能良好的POR 电路。为了减小电路面积和功耗,提高电路的可靠性和简易性,本文通过改进文献[3]的电路,设计了一种基于Brokaw 带隙基准、无比较器结构、 性能良好且带迟滞功能的上电复位电路。

2 传统上电复位电路的结构和问题

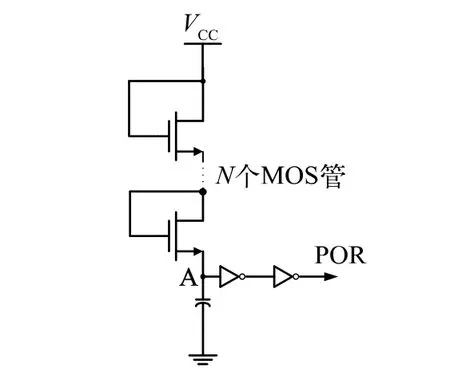

传统简单结构的上电复位电路如图1 所示。 该电路由N 个二极管连接的NMOS 管作为充电钳位电路,在上电过程中,当电源电压低于N 个NMOS 管的阈值电压,POR 信号为低电平,不能产生复位信号;当电源电压高于N 个NMOS 管的阈值电压,NMOS 管都导通, 电容开始充电,A 点电压升高到反相器的翻转电压,POR 信号翻转为高电平,上电复位结束。 传统带比较器的上电复位电路如图2 所示, 采用2 个电阻分压的方法对电源电压采样,用比较器对采样电压和基准电压进行比较, 采样电压大于基准电压,POR 信号翻转为高电平,实现了精准复位的功能。

图1 传统简单结构的上电复位电路

图2 传统带比较器结构的上电复位电路

采用图1 传统简单结构的上电复位电路,NMOS管的阈值电压受到温度和工艺的影响很大,电路不能精确判断复位点的电源电压。多个NMOS 级联使得电路不适合在低压下工作,如果电源电压过低则不能产生复位信号。 采用图2 传统带比较器结构的上电复位电路,比较器模块会增大电路的面积,产生一定的功耗。 综合2 种传统电路的优缺点,本设计基于Brokaw带隙基准产生受温度影响较小的基准电压,用此电压作为电路的复位判断电压,使用电阻对电源电压进行采样,本文无需使用比较器对采样电压和基准电压进行比较, 采用了带隙基准电路的电流动态特性比较2种电压,实现了电路的精确复位。

3 电路设计与分析

3.1 带隙基准电路的电流动态特性分析

Brokaw 带隙基准电路如图3 所示,PMOS 管M1、M2构成电流镜,镜像电流比值为1,NPN 三级管Q1、Q2和电阻R6、R7组成Brokaw 带隙基准的基础结构,VD为Q1、Q2的基极电压, 流过Q1、Q2的集电极电流分别为I1、I2,所以:

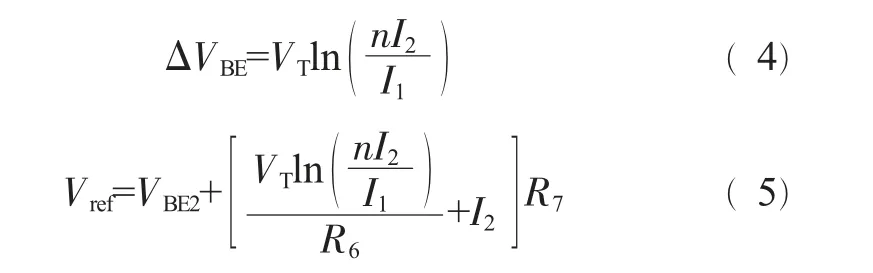

其中IS1、IS2为反向饱和电流,VBE1、VBE2为NPN 三极管Q1、Q2的导通电压, 热电压在室温下为26 mV。使用不同比例并联的NPN 管Q1、Q2在R6上产生压降,由式(1)、(2)得到:

设Q1:Q2=n,则IS1:IS2=n,所以:

由式(5)、(6)可知,当VD=Vref时,Q1、Q2所在支路上的电流相等。

当Vbe<VD<Vref且在电路刚导通时,电流I1较小,在R6上的压降可 忽略不 计,Q1、Q2构成电流镜, 且有I1=8I2, 随着电路启动过程中形成正反馈的电流镜,使得电路能够正常启动,且电流I1、I2随着电路启动而增大,当电流上升到R6上的压降不可忽略时,Q1和R6构成射跟随器,等效跨导小于Q2的跨导,Q1上的电流相比Q2上的电流上升逐渐变缓, 使得VD上升到VD=Vref时,Q1上的电流和Q2上的电流有交点,即I1=I2。 当VD上升到VD>Vref时,由于Q1上的电流相比Q2上的电流上升缓慢使得I1<I2。本电路以基准电压为比较点,通过比较VD和Vref的大小产生不同的电流信号。

图3 Brokaw 带隙基准

3.2 整体电路设计

基于Brokaw 带隙基准电路做了部分改进并增加了采样电路、电流比较电路和电平转换电路。 POR 整体电路如图4 所示,为了提高电流复制的精度,本文采用了自偏置的电流镜结构,当VD上升到VD=Vref,M2所在支路电流I2镜像M1所在支路电流I1,M7所在支路电流I3镜像M1所在支路电流I1,所以当VD=Vref时有:

带隙基准电路增加了M7管所在支路, 经整理可得基准电压:

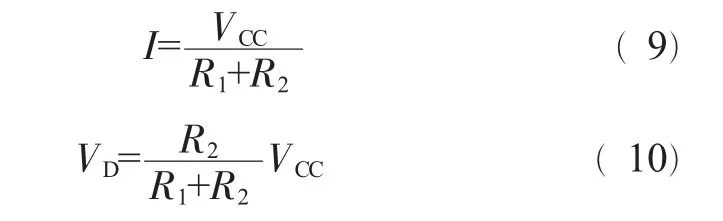

将带隙基准模块中的NPN 管的基极连接到采样电路中,采样电路由2 个电阻构成,利用电阻分压可得到采样电压VD。 在采样电路中为了降低电路的静态电流、减小功耗,应选择阻值较大的电阻,采样电路的静态电流和采样电压分别为:

其中采样电路中电阻阻值比R1∶R2=2∶1.2, 电源电压为5 V,由式(10)可知电源阈值为3.2 V,Vref为电源电压达到阈值时的采样电压,当VD>Vref时,产生高电平的POR 信号。

图4 POR 整体电路

在电源电压上电过程中,VD会随电源电压升高而升高, 当VD>Vref时,NPN 管Q2上的电流变化比Q1上的电流变化快,I2由I1按相同比例镜像所得,电流变化快的趋势发生在I3,即I3变化得比I1快,带隙基准产生不同的电流信号通过电流镜等比例镜像到电流比较电路。

M10~M19构成电流比较电路,在上电过程中,VC的初始逻辑电平为高电平,VCC上升到阈值时,I3>I1,此时唯一让电路平衡的方法就是M16、M18进入线性区,使得电压VC降低变为低电平, 电流I3无法等比例复制到M16、M18所在支路。 电流比较电路中,I1和I3产生微小的差值,VC就会发生翻转,提高了复位电压的精度。

M20~M23和INV2 构成电平转换电路,结构为2 个交叉耦合PMOS 和2 个互补下拉NMOS。VE为输入电压、输入为低电平时,M22截止,M23导通,M22漏端处的电压稳定在VCC,M21截止,POR 输出低电平。输入高电平时,M22导通,M23截止,M22的漏端电压 为低 电平,M21导通,POR 输出低电平。本文中采用电平转换电路的目的是将一个高电平转换为随VCC变化的高电平,即POR 信号在达到高电平时会随着VCC升高而升高。

为了提高POR 电路的抗噪声特性,在采样电路中增加了一个电阻R3和开关MOS 管M24组成迟滞电路, 当VD上升到Vref时,VC翻转为低电平,M24断开,VD瞬间分得更多的电压,防止因为电源电压抖动影响复位信号的判断。

4 仿真结果

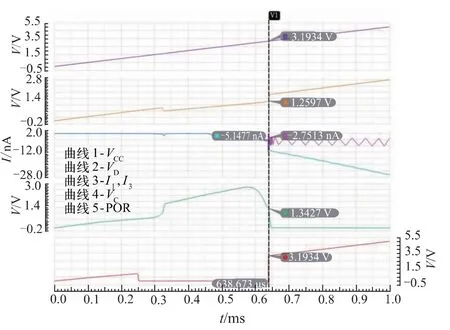

本文设计的上电复位电路采用的是0.5 μm CMOS 工艺设计, 电路工作在5 V 电源电压、TT 工艺和27 ℃的室温环境下。 仿真设置电源上电时间为1 ms,图5 为上电复位电路仿真曲线图。图5 从上至下第一条曲线是理想条件下的电源电压,电源电压呈斜坡式上升, 在1 ms 时达到5 V, 电源电压阈值是3.1934 V。 第二条曲线是采样电压VD, 可知在VD=1.2597 V 时,产生高电平POR 信号,由于此时迟滞电路中开关管M24断开,VD分得更多电压,VD电压会被快速抬高0.4 V, 减小电源抖动对复位信号的影响。第三条曲线是电流比较电路2 条支路电流, 电流大小分别为2.7513 nA 和5.1477 nA,电流比较电路会在支路电流产生一定的电流差使得VC翻转。 第四条曲线为电流比较电路输出电压VC,经电流I1、I3比较之后发生翻转,变为低电平。第五条曲线是POR 信号,可以明显看出POR 信号在电源电压上升到阈值、采样电压上升到基准电压、电流出现差值时变为高电平,满足系统对复位信号的要求。

图5 POR 电路仿真图

本文在-40 ℃、27 ℃、85 ℃3 种温度、TT、SS、FF、SF、FS 5 种MOS 管工艺角的情况下,经不同组合后得到的仿真结果显示,该上电复位电路具有良好的复位功能。 表1 给出不同温度和不同MOS 工艺角上电复位电路产生的电源阈值和基准电压的仿真结果,其中电源阈值用VCC_TH表示。

表1 上电复位电路电源阈值和基准采样电压的仿真结果

本文中通过计算不同工艺和温度下电源阈值与理论结果的误差率表示不同工艺和温度对电源阈值的影响。 表2 给出了不同工艺和温度下电源阈值与理论结果的误差率,其中误差率用ε 表示。

表2 不同工艺和温度下电源阈值与理论结果的误差率

通过表2 可知, 电源阈值在不同工艺和温度下误差率为0.31%~4.90%,误差范围较小,受工艺和温度影响较小,且在TT 工艺、27 ℃室温下影响最小,误差率为0.31%。

5 结论

设计了一种基于Brokaw 带隙基准的上电复位电路,利用带隙基准电路的动态特性产生不同的电流信号,将电流信号传输到电流比较电路中进行比较判断得到低电平信号,再经电平转换电路得到一个跟随电源电压变化的上电复位信号,增加迟滞电路减小电源噪声对电路的影响,从而实现了一种受温度和工艺影响较小、复位性能良好的上电复位电路。