基于FPGA 定时刷新控制单元的应用技术研究

孙洁朋, 陈波寅, 晏慧强, 丛红艳, 何小飞

(无锡中微亿芯有限公司, 江苏 无锡 214072)

1 引言

近年来,SRAM 型的FPGA 因其编程速度快、开发周期短等优点, 被大量应用在复杂的电子设计中,在航空航天领域的应用也越来越广泛。 然而,在宇宙环境中,存在着大量的高能粒子,此工艺的FPGA 极易受到空间高能粒子的影响,发生单粒子翻转(SEU)[1]。SEU 效应通常会导致FPGA 中的存储单元发生位翻转(即内容由0 变为1,或由1 变为0),随之带来的后果可能是计算结果错误、程序执行序列错误,工作异常,甚至是系统的永久失效、烧毁等[2-3],因此必须对FPGA 器件进行抗单粒子翻转加固设计, 最大限度地预防和阻止空间辐射效应的影响,提高航天器任务的可靠性。

提高FPGA 抗单粒子翻转的方法随着科学技术的发展也在不断地优化和更新。 目前主要有以下几种方法:①采用三模冗余,利用3 个功能相同的冗余模块和多数表决器来避免错误; ②回读配置区的数据帧,与初始配置数据进行对比,对出错帧或是整个配置帧进行刷新[4];③配置反熔丝PROM,通过编程定时刷新FPGA[5]。 三模冗余不会对出错配置信息进行修复,当错误累积到一定程度,器件就会失效。 回读刷新则一般采用反熔丝FPGA 器件控制芯片刷新,其软硬件设计较为复杂[1]。

本文给出了一种抗辐照的低成本解决方案,该控制单元采用三模冗余加定时刷新的方法来及时修正已出现的错误,提高抗SEU 的能力,并通过RTL 代码应用仿真验证,证明该方案的各项功能满足设计要求。

2 整体方案设计

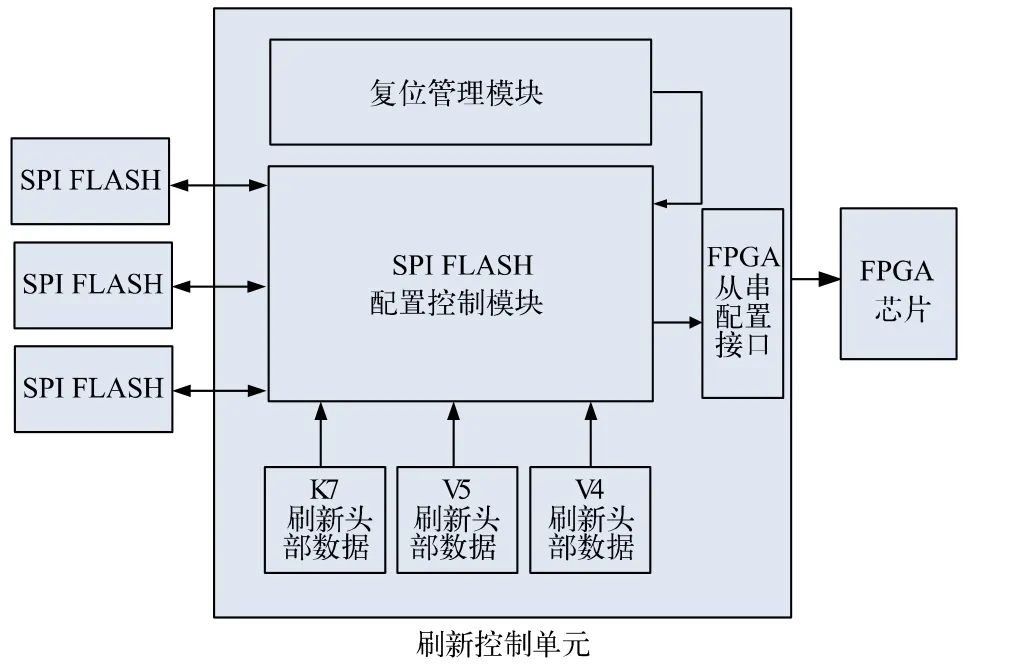

依据前面所介绍的设计需求,本文基于FPGA 定时刷新控制单元的整体设计方案如图1 所示。

图1 刷新电路整体设计框图

由图1 可知,该电路需要外接3 片SPI FLASH,工作时会对3 片SPI FLASH 中的数据进行单比特校验,采用表决通过的数据作为正确配置信息,具有单比特纠错的三模校验功能, 然后通过串行端口, 配置V4、V5 和K7 类型的FPGA, 并且在配置完成后对FPGA的逻辑部分进行定时刷新[6],纠正逻辑部分因为翻转产生的错误,从而达到抗辐照的目的。

市面上带有刷新控制的芯片有不少,例如中国自主研制的BSV2 定时刷新芯片和ACTEL 公司的抗辐射反熔丝FPGA A54SX32A 芯片, 这两款芯片都有定时刷新控制,但没有三模冗余的功能,支持的芯片为Xilinx 公司的Virtex II,而Virtex II 系列芯片可利用的逻辑单元较少,已不能适应未来航天的发展需求。 本文中的设计采用3 片SPI FLASH 存储配置信息,有三模冗余和定时刷新功能,同时兼容V4、V5 和K7 类型的多款FPGA 芯片, 可以满足航天领域对抗辐照型FPGA 的使用需求。

Xilinx 公司的FPGA 芯片配置访问接口有JTAG、SelectMap(从串)以及ICAP 3 种,本文中设计的定时刷新器件利用FPGA 的SelectMap 接口完成配置与刷新。

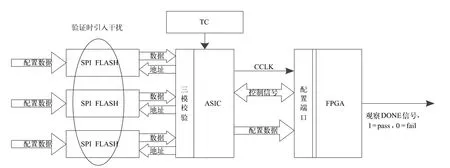

3 系统设计

本文中的定时刷新控制单元,是基于SPI FLASH设计实现的。SPI FLASH 容量为128 Mbit,电路设计的最高工作时钟频率为25 MHz,串行配置速率在1 MHz左右,刷新时间间隔可以选择连续刷新、10 min、20 min、30 min 4 种模式。基于SPI FLASH 的抗辐射系统如图2 所示。

FPGA 配置数据存储在3 片SPI FLASH 芯片中,与FPGA 之间通过抗辐照定时刷新单元连接,刷新电路起到数据交换的桥梁作用, 如图2 所示。 定时刷新电路有两种工作模式:配置模式和刷新模式。 系统初始上电时, 定时刷新电路处于配置模式, 通过SelectMap 模式配置FPGA,系统正常工作后,刷新电路进入定时刷新模式, 按设定的时间周期性地将SPI FLASH 中的逻辑信息配置到FPGA 中,完成刷新。

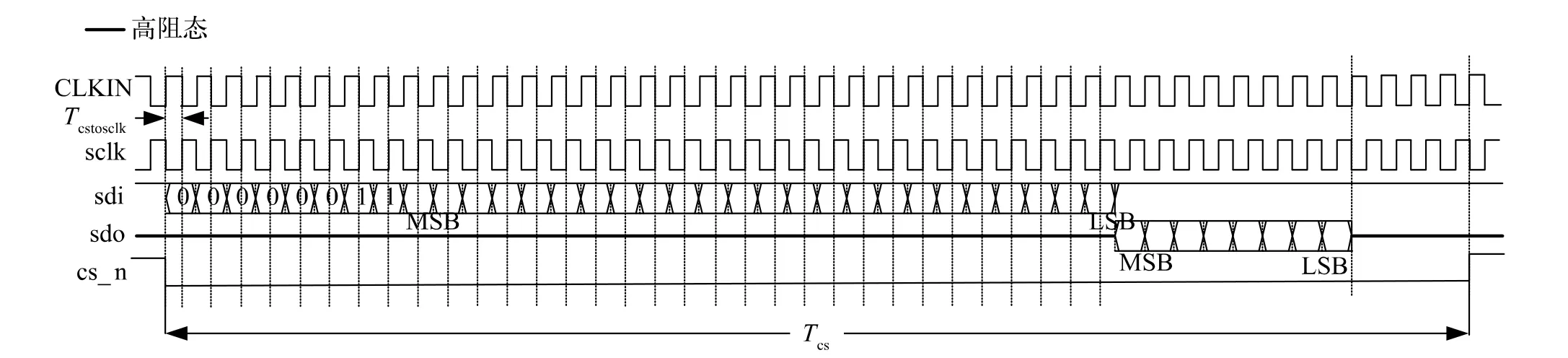

SelectMap 模式的连接方式如图2 所示,M0、M1、M2 接电源(VCC),用于设置FPGA 的配置模式为从串模式, 即CCLK 的来源是外部。 PROGRAM_B 和INIT_B 需接4.7 kΩ 的上拉电阻,DONE 信号需接330 Ω 的上拉电阻。 对FPGA 的从串配置时序[7]如图3所示。

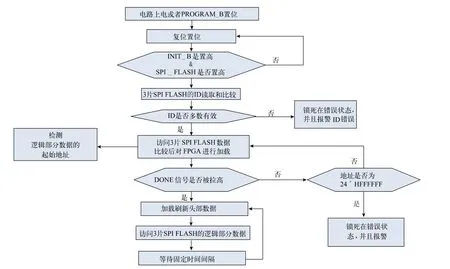

定时刷新控制电路通过检测FPGA 芯片的DONE 信号来决定进入配置模式还是刷新模式。 配置和刷新的工作流程如图4 所示。

由图4 可知, 定时刷新控制单元在工作过程中主要完成以下4 个功能:

1)FPGA 及刷新电路上电配置。 初始化的FPGA上电后, 将PROGRAM_B 信号至少拉低300 ns 后置高,INIT_B 会自动产生0 到1 的跳变, 若INIT_B 为高,指示FPGA 内部初始化完成,进入数据下载过程,同时等待刷新电路内部复位完成, 之后开始正常工作,若INIT_B 为低,则一直检测该信号,直到变为高电平为止。

图2 基于SPI FLASH 的抗辐射系统

图3 FPGA 串行配置时序

2)ID 检测。 刷新单元在复位完成后,首先工作是检测3 片FLASH 的ID 信息,ID 检测有效后开始访问SPI FLASH 中的数据,进行后续配置下载,否则锁死在读ID 状态并报警。

3) 配置FPGA 芯片。 ID 检测有效后, 开始配置FPGA, 设置的FPGA 专用配置模式管脚M0~M2 为000,进入从串模式下载,刷新电路发送CCLK 同步时钟给FPGA 芯片, 并将3 片FLASH 中存储的码流信息进行单比特校验, 以25 MHz 为例,V4 大概需要10 ms,V5 需要45 ms,K7 需要115 ms,来完成所有配置信息的对比,然后将表决通过的数据经过DIN 引脚配置到FPGA 芯片中,图5 为SPI 的数据读取操作。

4)检测DONE 状态。 进入配置状态后,电路会持续检测DONE 信号,一旦超过预计完成配置的时间却还未拉高,则意味着配置失败,会自动在该FPGA 芯片的INIT_B 端施加复位脉冲,进行重新配置;

5)定时刷新。 当检测到DONE 信号变高电平后,刷新控制电路会自动启动刷新模式,按用户需求加载不同型号芯片的头部数据,先刷新一次,然后按选择的时间周期性地刷新SPI FLASH 中的逻辑数据。

本文中的抗辐照定时刷新控制单元,最高工作时钟为25 MHz 时, 支持Xilinx 公司Virtex4 系列的XC4VLX25,Virtex5 系列 的XC5VSX95T 和K7 系 列的XC7K325T,刷新时间间隔也有4 种可选,能够满足不同用户的应用需求。

图4 SPI FLASH 配置和刷新工作流程

图5 SPI FLASH 数据读取操作

4 应用验证

本文中的定时刷新控制单元旨在给出一种低成本的抗辐照解决方案,为了检验本方案能否满足设计需求,这里给出了RTL 代码的验证,对定时刷新控制单元在工作过程中主要完成的4 个功能进行重点验证,并通过应用验证来说明该设计能够通过三模冗余及定时刷新措施以提高抗单粒子翻转, 满足应用需求。 下面以Xilinx 公司的Virtex5 系列的XC5VSX95T为例,进行刷新电路的RTL 代码的应用验证。 定时刷新控制单元的验证方案如图6 所示。 利用搭建好的FPGA 芯片配置环境进行本方案中的RTL 代码验证,通过验证模拟实现刷新电路工作时的各种状态,确保设计能达到预期目标。

刷新电路复位管理模块仿真如图7 所示。 首先是上电后,刷新电路复位管理模块的正常启动,通过上电后FPGA 的PROGRAM_B 和INIT_B 两个信号共同作用来控制电路的全局复位工作。

FLASH 的ID 检测仿真如图8 所示。 电路的全局复位正常启动后,开始检测FLASH 的ID,读ID 通过,则开始访问FLASH 中的数据,否则一直在锁死状态。

3 片FLASH 数据单比特校验及FPGA 配置仿真如图9 所示。 ID 检测通过后, 开始接收存储在3 片SPI FLASH 中的数据,经过单比特校验后,将表决通过的数据配置给FPGA,通过观察DONE 信号是否拉高来判断配置是否正确, 超过预估时间未检测到DONE 信号变化, 说明配置信息错误,INIT_B 信号会复位一次,重新配置FPGA。在验证中加入了不同形式的干扰信息,来模拟空间环境。 flash_data_state 为3 片FLASH 数据表决状态信号,根据这个信号可以判断是哪片FLASH 配置信息出现问题。

图6 定时刷新控制单元的验证方案

图7 刷新电路复位管理模块仿真

图8 FLASH 的ID 检测仿真

图9 3 片FLASH 数据单比特校验及FPGA 配置仿真

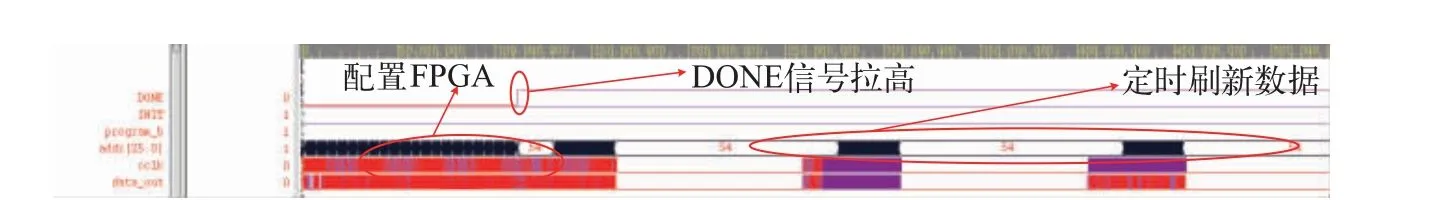

芯片刷新过程如图10 所示。 完成FPGA 配置后,刷新电路会执行立即刷新操作,然后按设计的时间周期性刷新芯片。

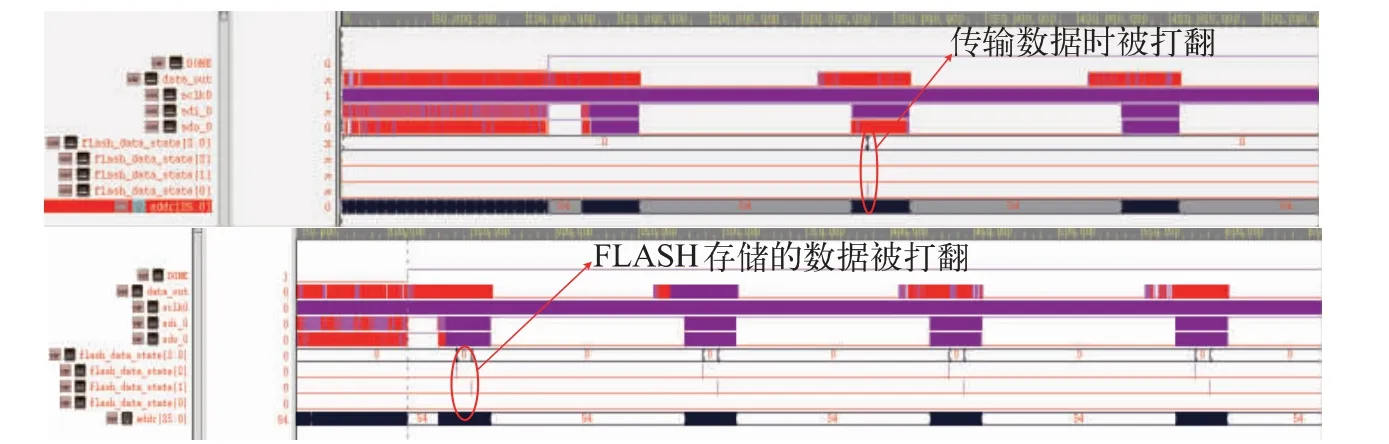

有粒子干扰时的刷新仿真如图11 所示。 在电路定时刷新的过程中,会受到高能粒子干扰,配置信息会有概率性地发生翻转,翻转的类型有多种,这里给出了其中两种, 一个是FLASH 将配置信息发送到控制单元时发生翻转, 一个是FLASH 存储的信息发生翻转。

图10 芯片刷新仿真验证

图11 外部干扰时芯片刷新仿真验证

刷新电路将受干扰的配置信息进行三模冗余,然后配置到芯片中,因为是单比特检验,可以提高抗干扰的能力,但随着使用时间的增长,错误信息累积越来越多,会在某个时刻将校验通过的错误信息发送到FPGA 芯片中,从而导致功能异常,电路失效。 本文给出的方案可以延缓这个时刻的到来,增加装备的使用寿命。 后续的技术改进可以把这个问题作为研究方向,一种方法是将FPGA 断电,重新对FLASH 烧写正确的码流信息,然后上电,完成配置与刷新,其他方法有待未来进一步研究。

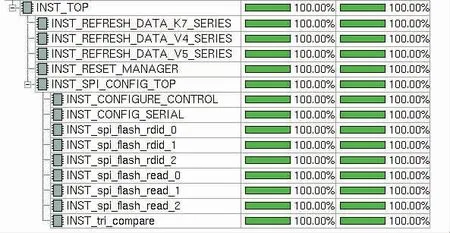

针对本方案设计所有功能验证点,进行了如图12所示的覆盖率收集,所有验证用例功能正确,覆盖率达到100%。

上述验证结果表明,本文提出的基于FPGA 定时刷新控制单元的设计切实可行,所设计的功能达到预期目标, 通过三模冗余与定时刷新的功能来提高抗SEU 的能力,能够满足应用需求。

图12 刷新电路功能覆盖率收集

5 结论

本文给出了一种基于抗辐照型FPGA 芯片的定时刷新控制单元的可行性设计方案,通过采用三模冗余加定时刷新相结合的加固技术, 可以有效解决SRAM 型FPGA 在空间环境应用中遇到的单粒子翻转问题。 后续还有一些问题需要解决,比如粒子翻转过多、影响芯片功能时,可以采用对FLASH 重新烧写正确码流的方法来解决这一问题,从而更好地满足航天领域对抗辐照型FPGA 的使用需求。