高速接口电路发送器的设计*

吕新为

(西安邮电大学电子工程学院 西安 710121)

1 引言

随 着 高 速 模/数 转 换 器(Analog-to-Digital,ADC)和数/模转换器(Digital-to-Analog,DAC)分辨率和采样率的不断提高,对数据转换器接口的性能要求不断提高[1]。多路并行传输方式由于码间干扰[2]、信号偏移等问题限制了应用速度和传输距离[3],并且还增加芯片引脚设计和板级布线与系统互联的硬件开销,直接增加系统成本[4]。而串行传输节约设计成本与空间、应用更灵活等优势使得高速串行接口电路成为高速转换器接口电路的首选,用于解决高速转换器与FPGA之间的传输问题。不仅可以克服并行数据传输带来的性能下降问题,同时可支持更高速数据传输。此外还降低了I/O需求及封装尺寸,降低静态功耗节省系统成本。

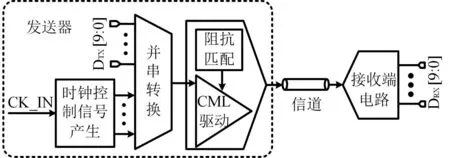

本文主要针对高速接口电路发送器[5]进行研究,高速接口电路发送器主要实现并行数据到高速串行数据的转换与传输,并解决高频信号传输时所带来的信号完整性问题[6]。发送器包含并串转换电路、CML驱动电路[7]及阻抗匹配电路三个模块。并串转换电路实现10∶1数据串化,串行数据最高位速率可达3.125Gbps,CML驱动电路将串化后的信号以差分信号传输到片外,阻抗匹配电路实现单端50Ω电阻匹配。本文采用SMIC 0.18μm工艺实现完整的高正高速接口发送端电路并进行电路功能的仿真验证。

2 发送器的设计

高速接口电路包含发送器和接收器,发送器将多路并行的数字信号转换为适合信道传输的串行模拟信号并将其传输到信道上,而接收器将信道传输过来的数据进行处理重新恢复成多路并行数据。图1所示为高速接口电路发送器结构示意图,发送器包含时钟控制信号产生、并串转换电路、CML驱动电路及阻抗匹配电路。时钟控制信号产生与并串转换电路实现并行数据到串行数据的转换[8],CML驱动电路将串化后的数据以差分信号形式按照要求传输到信道上,阻抗匹配电路解决高频信号传输时由于阻抗不匹配而产生的信号完整性问题。

图1 高速接口电路发送器结构示意图

2.1 并串转换电路的设计

本文设计的并串转换电路是将位速率为312.5Mbps的10路并行数据转换为3.125Gbps的1路10位串行数据,图2所示并串转换电路整体结构,包含控制信号产生模块及并串转换模块。控制信号模块是对输入时钟信号进行分频,实现10:1并串转换的时钟,包含二分频与五分频电路;并串转换模块则是实现10路数据1路数据的串化过程,包含5∶1并串转换和2∶1并串转换。

图2 10∶1并串转换电路结构框图

时钟信号CK_IN通过二分频电路产生一对反相的时钟信号CK_A与CK_B,其频率f=781.25MHz,用于产生五分频时钟信号以及控制实现2∶1并串转换;时钟控制信号CK_A与CK_B通过五分频电路产生两组控制信号:占空比均匀的CK_D、占空比为1∶4的5对反相的时钟控制信号CK_i_M/CK_i_N(i=1~5),控制电路实现5∶1并串转换。

并串转换模块包含5∶1并串转换和2∶1并串转换,输入数据信号为10路并行数据D0~D9,其位速率为312.5Mbps。将输入数据分为两组通过5∶1并串转换模块得到输出信号Data1和Data2,其中Data1与Data2的位速率为1.5625Gbps;Data1与Data2再通过2∶1并串转换电路实现并串转换,得到的信号为OUT1、OUT2,并且OUT2是OUT1的反相信号,此时完成了传输数据的10∶1并串转换,数据的位速率为3.125Gbps。

图3 时钟控制信号时序图

图3 为时钟控制信号时序图,输入时钟信号CK_IN的周期为T=640ps,其通过二分频后得到CK_A与CK_B反相且周期为T=1.28ns,通过五分频电路得到的时钟信号CK_D、CK_i_M/CK_i_N(i=1~5)其周期均为T=6.4ns,但是CK_D信号占空比均匀,CK_i_M/CK_i_N信号占空比为1∶4,CK_i_N与CK_i_M波形对应且反相,并且一组信号从CK_1_M到CK_5_M其上升沿逐次延迟640ps。

2.2 CML驱动电路的设计

CML驱动电路在高速接口电路中负责将片内数据传输到片外介质上,并保证数据具有一定的驱动能力。

本文设计的CML驱动电路以差分对形式为基础,多级锥形级联的形式增强驱动能力[9]。图4为单级电路结构,为保证电路能够工作在较高的速度,差分对管M1至M4均应工作在饱和区,尾电流源ISS为电路提供了一个独立于输入的偏置。单级电路要实现最好的性能则尾电流需处于全切换状态[10],尾电流处在全切换状态时电路输出的差分摆幅仅是负载电阻和尾电流的函数。

图4 单级电路结构

图5 输入输出特性

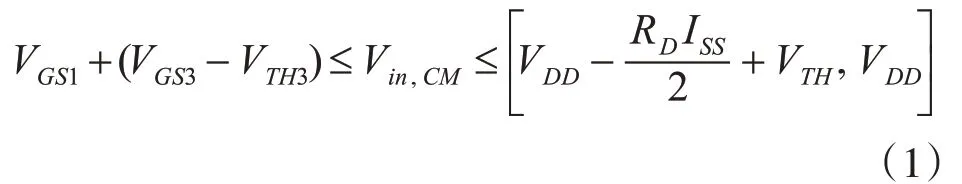

为保证电路能够工作在较高的速度,CML buffer的差分对管、均应工作在饱和区,且尾管也应保持在饱和区,这样将得到输入共模电平的范围:

其中VGS为晶体管的栅源电压,VTH为晶体管阈值电压。图5为差分电路的输入输出特性曲线,差分输出摆幅受MOS阈值电压的限制[11],最大差分输出摆幅为

在级联时,上一级的输出摆幅即为下一级的输入摆幅。此处要注意的是,在主驱动电路的最后一级考虑阻抗匹配[12]其电阻R=50Ω,由于本设计中对输出摆幅要求为500mV,因此所选MOS管器件的阈值电压VTH≥500mV。

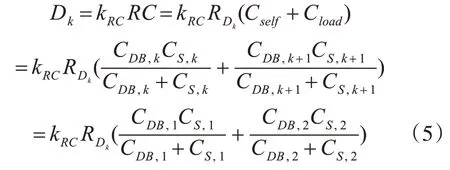

为了增大电路的驱动能力,同时使电路的延时达到最小,本文中采用多级级联的方式,将总的延时平均分到每一级上,这样每一级管子的尺寸和电流都是以一个相同的比例u来逐级增大的。本文采用数字电路中常用的计算延时的RC延迟模型[13],确定电路的级数N和比例常数u。其延时Delay如式(3)

其中,kRC是对数项,R为等效电阻,C为等效电容。对于CML电路来说,其延时同样可以用该模型来计算:

在CML电路中每一级的等效电容为本级的寄生电容Cself与负载电容Cload之和。据此计算出电路总的延时,从而确定电路的级数N以及比例常数u。图6所示为第k级与第k+1级的两级级联电路。

图6 两级级联的CML电路

由上图可得第k级电路的延时为

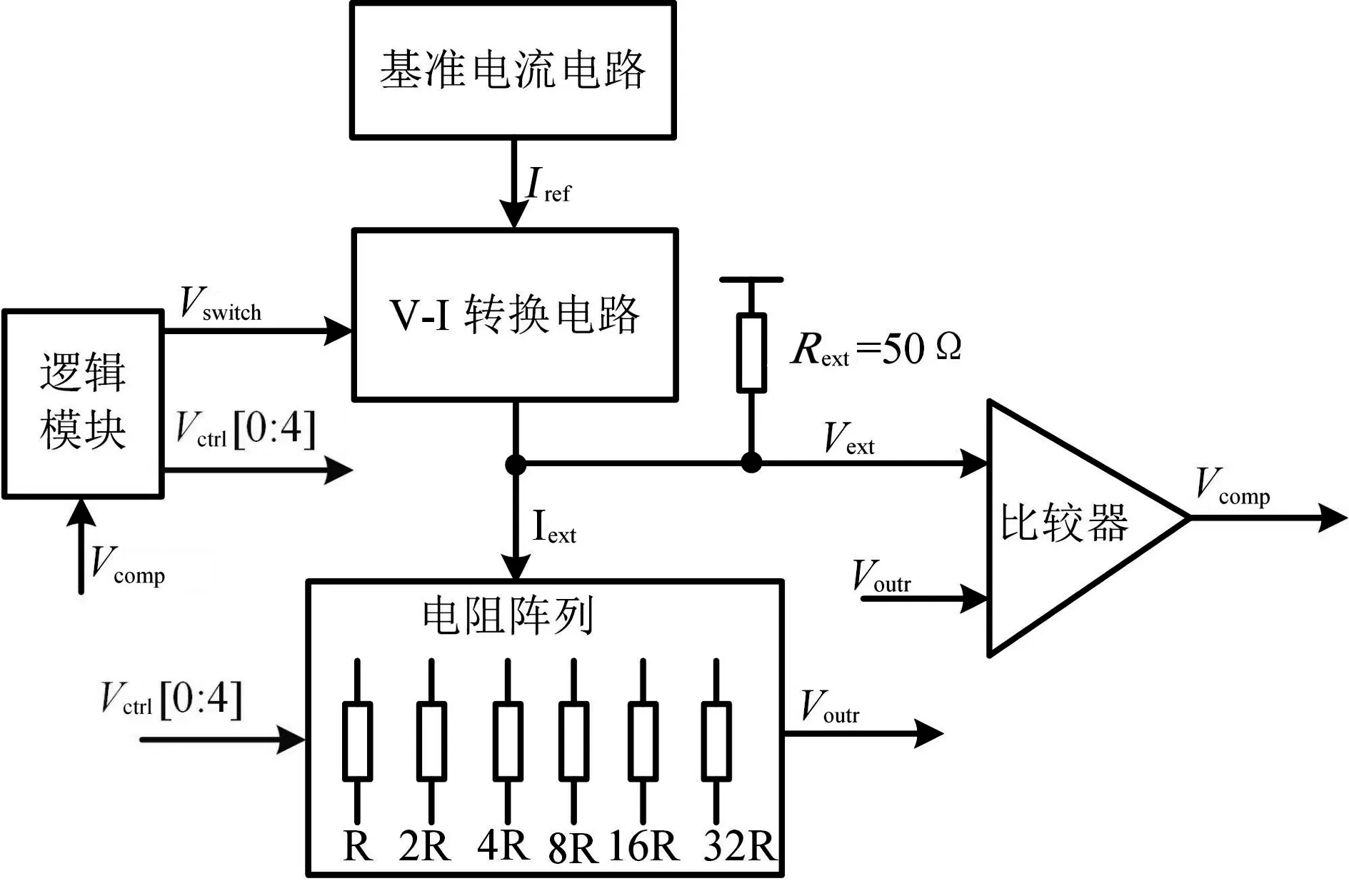

当CDB< 其中: 可以根据电路的具体参数来得到λ,从而求得Nopt和u。本文据此优化后确定电路结构为4级级联,MOS管尺寸比例为2倍。 在高频信号传输过程中,与传输线特征阻抗不匹配会带来一系列的信号完整性问题,如传输线上信号反射、串扰、驻波[14]等,会严重影响信号或能量的传输质量,进而影响后级电路的性能。为此,本文设计了自适应阻抗匹配电路,以实现精准度较高的电阻。 本文所设计的自适应阻抗匹配电路结构如图7所示,包含逻辑模块、基准电流电路[15~16]、V-I转换电路、电阻阵列及比较器[17]。根据所需电阻值的大小确定电阻阵列中各阻值的设定,并按照一定算法设计控制信号Vctrl[0:4]的变化,进而控制电阻阵列阻值的变化;通过基准电流源与V-I转换电路产生精准电流Iext,精准电流分别与片外50Ω电阻及片内电阻阵列产生两个电压信号Vext与Vreal,两个电压通过比较器得到的信号Vcomp又设计为逻辑模块的控制信号,使得比较出正确的结果后逻辑模块可保持所需的序列。当Voutr达到所需的电压值时的电阻阵列的阻值即为符合要求的阻值。 图7 自适应阻抗匹配电路结构框图 本文基于SMIC 0.18μm CMOS工艺完成了电路设计及仿真验证,主要验证发送器电路的三个主要模块功能的实现:10∶1并串转换的实现、CML驱动电路的输出以及阻抗匹配电路。下面将对整体电路进行仿真验证与分析。 图8 整体电路仿真结果 图8 为整体电路前仿真结果,输入信号是为10路并行输入数据D0~D9,位速率为312.5Mbps。输出是两组差分信号,第一组是实现10∶1并串转换后的串行数据OUT1及反相信号OUT2,并串转换后的数据位速率为3.125Gbps;第二组是并串转换后的数据通过CML驱动电路后的差分输出,其保持了串行数据的波形与速率并且CML驱动电路的输出摆幅为762mV。图8中以显示两组数据为例表明10∶1并串转换的实现与传输。 图9 自适应阻抗匹配电路仿真结果 图9 是自适应阻抗匹配电路仿真结果,其中固定电平Vref=1.3V是参考电压,阻抗匹配电路的输出信号Voutr从1.205V开始阶升,直到Voutr≥Vref时开始保持不变,此时电压为1.31V,同时所测电流值为9.79mA,则电阻值为R=(VDD-Voutr)/I,R=50.05Ω,偏差仅为0.1%。同时Vref与Voutr是比较器的输入信号,比较器的输出是Vcomp。当Vref大于Voutr时Vcomp为高电平,当Vref小于Voutr时,Vcomp跳变为低电平。同时Vcomp是逻辑模块的控制信号,Vcomp为低电平时逻辑模块的输出状态锁定,则使得Voutr保持不变。表1为不同工艺角下阻抗匹配电路仿真结果。 表1 不同工艺角下阻抗匹配电路仿真结果 本文基于SMIC 0.18μm CMOS工艺完成了电路版图设计,图10所示为整体电路版图。图中左边为添加I/O与PAD之后的整体电路版图,右边为整体电路IP核版图。整体电路IP核版图中主要包含10∶1并串转换电路、CML驱动电路、阻抗匹配电路以及电阻阵列四大模块,其中电阻阵列是由两组阻抗匹配电路中的电阻阵列模块组成,由于CML驱动电路的结构需要两个50Ω电阻,为保证该部分电路的匹配性而添加单独的电阻阵列。整体电路IP核的版图长*宽为220.14μm*197.5μm。 图10 整体电路版图 本文设计了一种高速接口发送器电路,包含10:1并串转换、CML驱动电路、阻抗匹配电路,实现了高速数据转换与传输,并实现传输终端的阻抗匹匹配。整个电路采用SMIC 0.18μm CMOS工艺,仿真结果表明,电路实现了位速率为312.5Mbps的并行数据到位速率为3.125Gbps的串行数据的转换,CML驱动电路实现了串行数据的传输功能,输出摆幅为762mV,阻抗匹配电路实现的高精度电阻50.05Ω,偏差仅为0.1%。

2.3 自适应阻抗匹配电路的设计

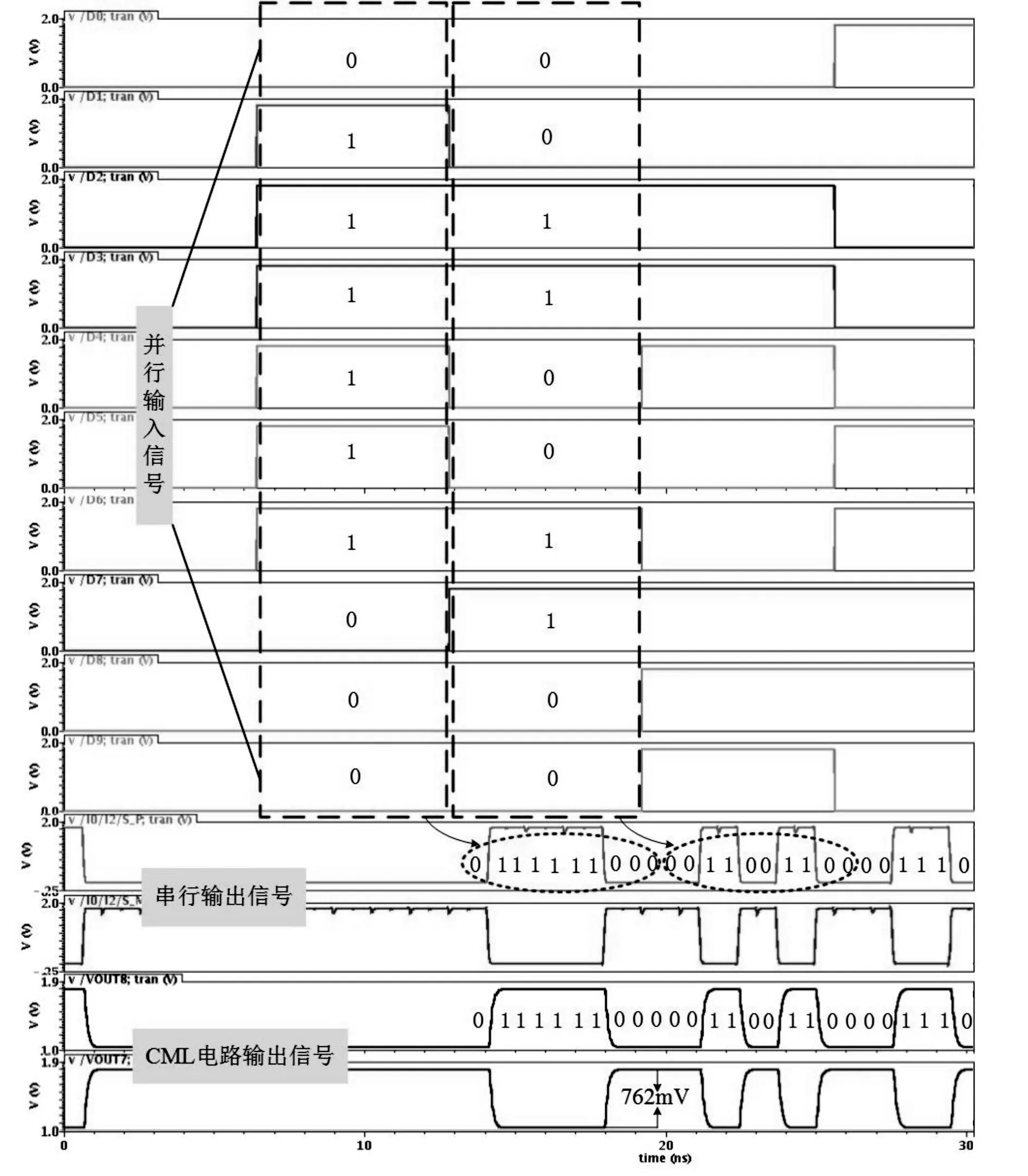

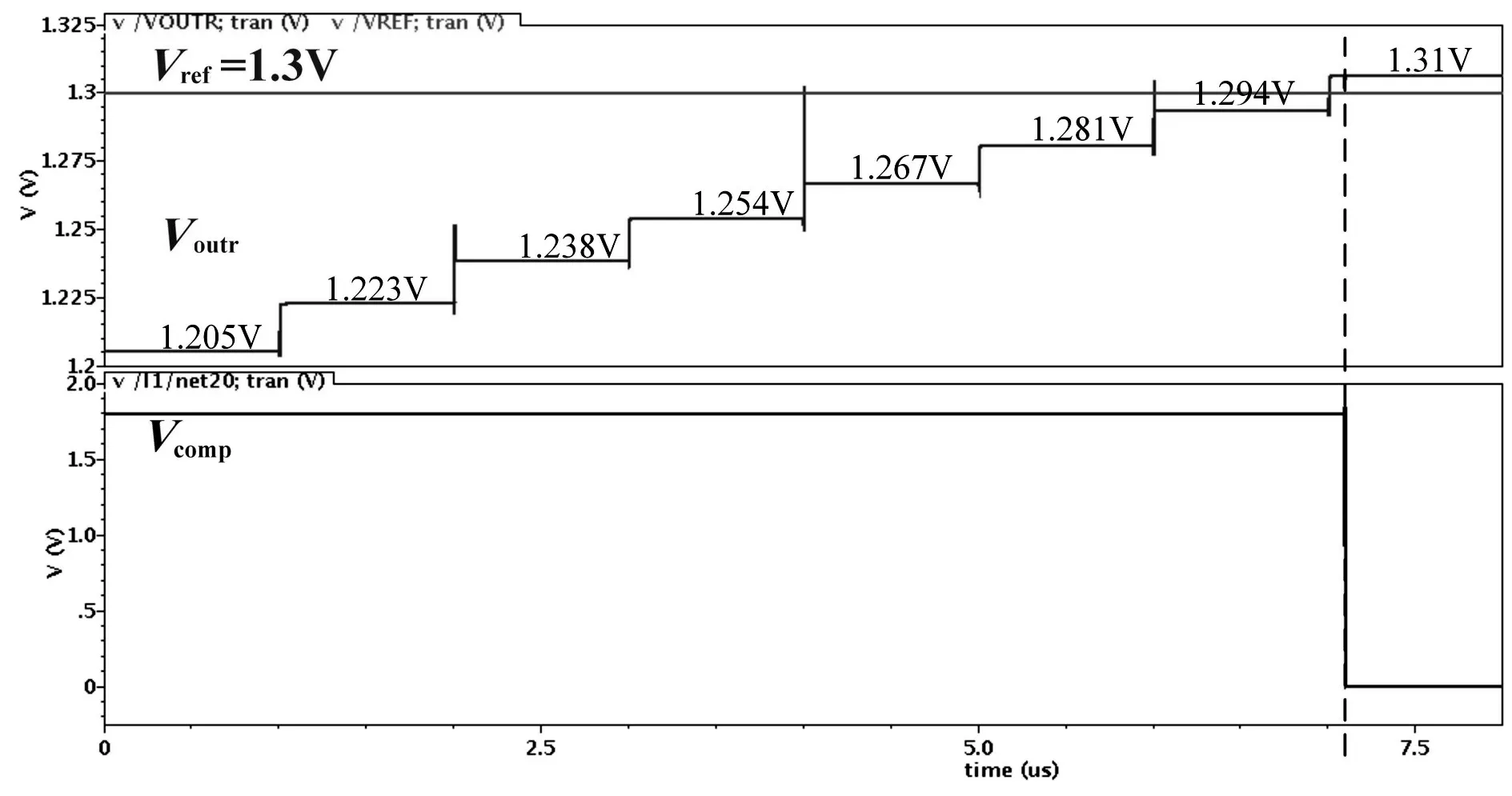

3 仿真结果及分析

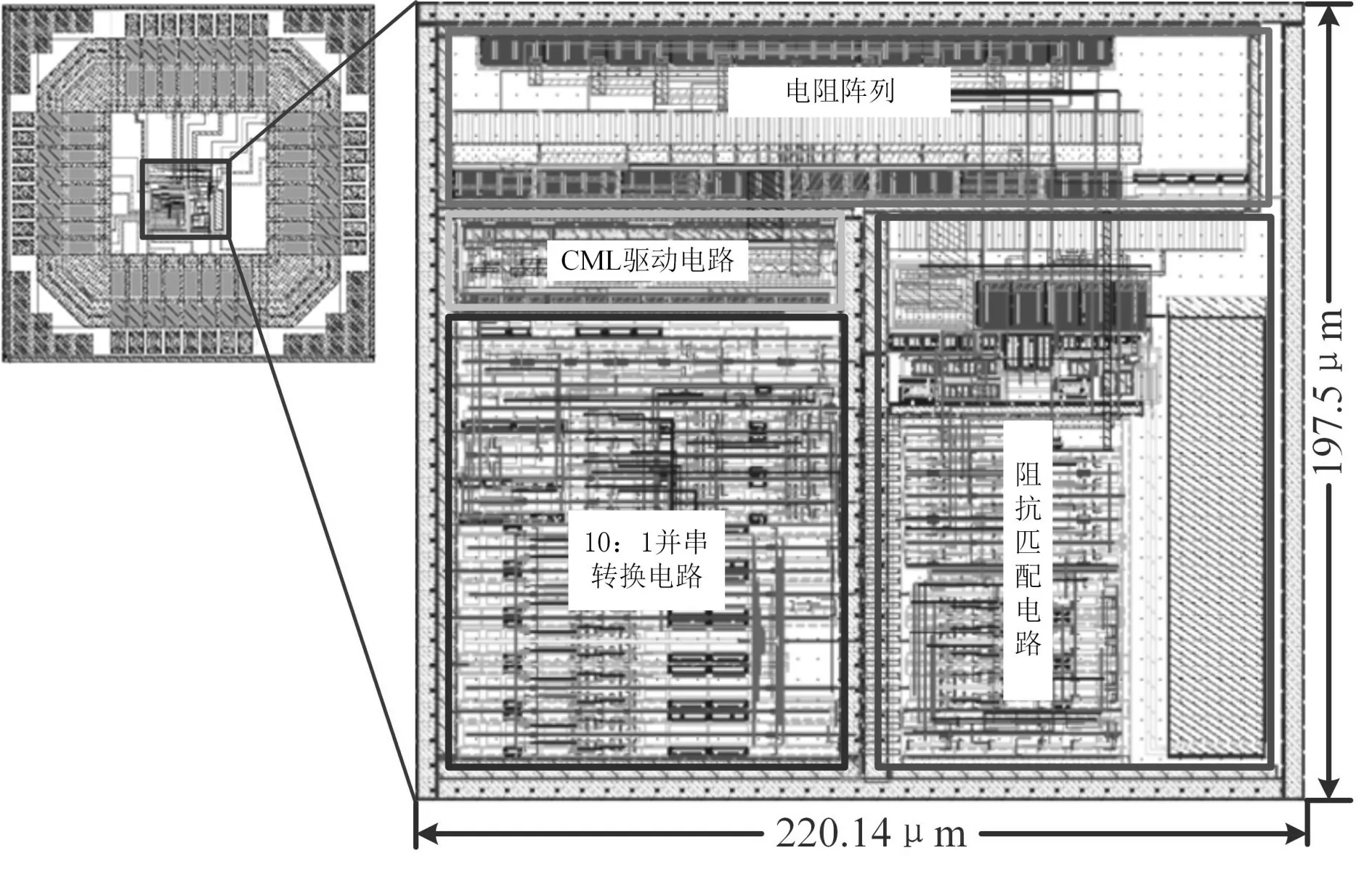

4 版图设计

5 结语