网络传输后信号再生和相位同步的设计

刘星宇, 张翠翠,b, 张鹏辉,b, 杨锦程, 李 啸

(西安交通大学a.信息与通信工程学院;b.通信与信息系统国家级虚拟仿真实验教学中心,西安710049)

0 引 言

全国大学生电子设计竞赛涉及专业有电力电子、电子信息、自动控制、机械工程等。它是一场大学生的科技活动盛事,自1994 年开赛至今,在全国高等学府中影响深远。2019 年全国共有1 109 所学校、17 313支代表队、52 000 名学生参赛。

比赛以命题式、半封闭的形式进行。要求学生3人一组从给定的题目中选择一个题目,在4 天3 夜里设计出一个完整的电路系统,最后由专家组进行现场测评,根据各项指标打分。队伍之间比拼的是谁的指标好、谁的功夫硬,竞争非常激烈。不少高校对获得国家一等奖的学生提供免试保研资格,还有部分高校对于指导学生获国奖的老师给予职称晋升优先资格。

本文针对电子设计竞赛题目中的“数据采集和传输类题目”,以2019 年的E 题为例,进行分析设计。随着电子技术的发展,此类题目对采集速率、存储资源和传输带宽要求越来越高,必须在方法和策略上有所创新有所突破,才能在有限的存储和带宽资源下完成系统的各项性能指标要求。针对此,本文设计了非实时传输和自适应存储策略,可有效节约网络带宽和存储空间,并且超额完成系统指标要求。实测结果证明了该策略是一种可行且较优的解决方案。

1 需求分析和核心思路方法

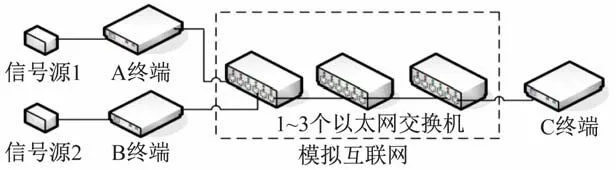

2019年全国大学生电子设计竞赛的E题“基于互联网的信号传输系统”结构图如图1 所示。A 终端和B终端采集信号源发出的周期信号并经交换机网络后传输到C终端,要求C终端对信号源发出的信号重建并补偿因网络延时带来的相位延迟,实现再生信号与原信号的相位同步。要求再生信号与原信号的幅度误差不大于5%,周期误差不大于10%。相位同步误差不大于10 μs,响应时间不大于5 s。要求对信号源的采样率不低于10 MSa/s,采样位宽不低于8 位。对该题目分析,可得两个关键指标需求:①对网络带宽的需求分析。千兆网传输除去网络协议开销,实际有效传输速率约为(1 000 ×0.7)/8 =87.5 MSa/s,即在全速的情况下,最多每秒可传输87.5 M个样点。对于百兆网,则为8.75 M/s个样点。千兆网虽有大的余量,但当采样率提高以后仍然会出现带宽不够的情况。②对存储空间的需求分析。由于接收端要补偿网络延时,所以需要至少存储一个周期的信号波形。在10 M 采样率下,对于低频信号(如0.2 Hz,题目中要求响应时间不大于5 s,推算最低频率为0.2 Hz),则需要10 ×5×8 =400 M位的存储空间。

图1 基于互联网的信号传输系统

针对带宽不足和存储过大的问题,设计了自适应存储策略,并结合非实时传输,可有效降低传输带宽和减少存储空间。此外,设计了交织传输策略提高系统的传输可靠性,设计了延时补偿策略超额完成系统对同步的指标要求。

1.1 自适应存储策略

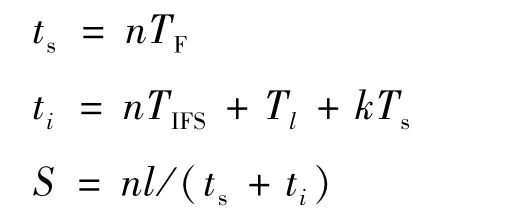

该策略中首先以10 MHz采样率对信号进行实时采样,并据此测量信号周期;4 KB 存储空间根据信号周期对信号进行存储,在保证信号波形数据尽量丰富的情况下充分利用存储空间。

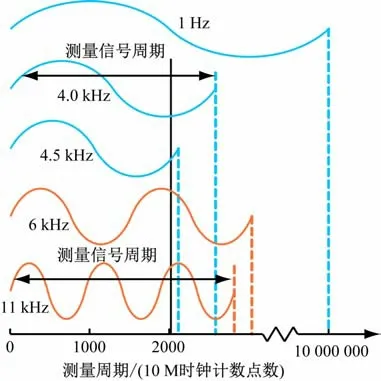

图2 不同频率信号的采样存储策略

对低频信号,使用抽样存储来减少因ADC量化位数限制而导致的采样点数值重复冗余。这不仅节约了波形数据的存储空间,而且减少了数据发送量。对于高频信号而言,受限于ADC 采样速率,其一个周期含有的采样点数很少,由样点重建的波形相位噪声明显,且高频信号周期测量误差大,以上两点导致接收端的相位同步精度降低。为改善这个问题,高频时将多个高频信号周期看作一个低频信号周期,即多周期降频法存储和处理,有效利用存储空间,降低相位噪声、提高周期测量精度,进而提高相位同步精度。

在4 KB 的存储空间中,采用“低频信号抽样存储、高频信号多周期存储”的策略,使存储器在信号低频时不撑满、高频时不空半,充分利用存储空间,为信号高精度时延补偿(即相位同步)提供数据支撑。

该自适应存储策略依赖于高精度的周期测量算法。

1.1.1 信号周期测量

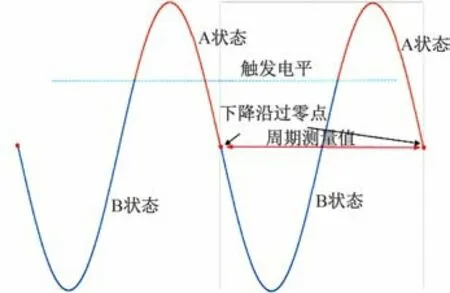

设计中使用迟滞比较+过零检测相结合的方式,有效降低了因噪声引起过零点抖动导致的信号周期测量误差。具体方法如图3 所示。

图3 迟滞比较+过零检测周期测量法

图3 中,FPGA设置一个触发电平,当信号大于该触发电平时,进入状态A。在A状态的情况下,如果检测到电平由正转为负(即检测过零点),则进入状态B,记录此刻过零点位置。在B状态时,当信号再次大于触发电平时,进入到A状态。只有在A状态下过零点位置才被记录。两个相邻过零点位置相减,即为信号周期。这避免了过零点附近的信号上下抖动出现的多零点情况。

在FPGA中使用10 MHz的时钟fclk(该时钟同时为采样时钟)为基准,采用脉冲计数法。这种测量方法的最大误差等于时基信号的周期,分辨率为时基信号的周期[1]。该方法测量精度取决于被测信号的周期和计时精度[2],相对误差会随着待测信号的频率升高而变大。在10 kHz 附近时,为0.1%;在1 MHz 附近时,为10%。

设计中将高于5 kHz的信号使用多周期存储合并为一个低频信号,即保证了周期测量误差小于0.05%。

1.1.2 低频信号的抽样存储策略

考虑到FPGA中的有限存储资源,设计中对于低频信号在10 MHz的采样率下获得的数据进行抽样存储。根据选定的FPGA 芯片型号中的存储资源大小,设定存储空间为4 096 ×8 bit 即4 KB,即最大可存储4 096个样点。由10 M/4 096 =2.5 K,对2.5 kHz以下的信号,按照跳点存储,即每间隔X 个样点存储一个点。设信号的周期为M(在fclk基准下的一个周期的样点数为M),则X =M/4 096,即M右移12 位得到X。

1.1.3 高频信号的多周期存储策略

对于频率在2.5 ~4.9 kHz之间的信号,存储一个完整周期;大于4.9 kHz的信号,采取存储多个周期的策略。具体实现方法为:在fclk基准下,每到一个过零点时,检测存储器中的数据是否超过2 048,若没有超过,继续写入;若超过,停止写入,等待数据被读出后的第1 个过零点时继续开始写入。

以上实现方法的理论分析为:存储器中对于高频信号存储的Y 个周期的计算公式为:Y =2048 ÷ T ÷0.000 000 1 +1(T为信号周期)。举例:频率在4.9 ~9.7 kHz之间,存储2 个周期认为是一个周期信号,频率为原频率的1/2;频率在9.7 ~14.6 kHz之间,存储3 个周期认为是一个周期信号,频率为原频率的1/3。

综上,自适应存储策略的示意图如图2 所示,周期更正如图4 所示。在低频(f <2.441 kHz)时下抽样存储;在中频(2.441 kHz <f <4.882 kHz)时逐点存储;在高频(f >4.88 kHz)多周期存储,并将高频时存储的多周期信号看成一个信号周期对测得的信号周期更正。采样存储的时钟与网络发送的时钟不同,用双口RAM来存储数据,其具有两个独立的读写端口,但对于一读一写的情况可能会产生错误,用“Read After Writer”的模式进行操作[3]。

图4 周期更正

1.2 交织传输策略

交织从其本质上来说是一种实现最大限度改变信息结构而不改变信息内容的技术[4]。

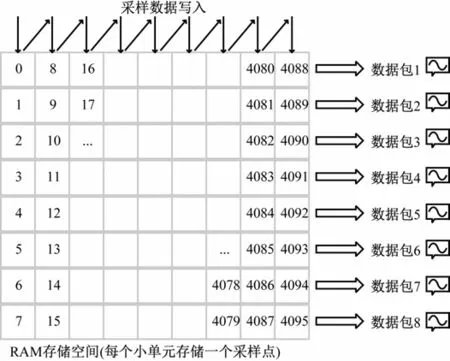

设计中,发送端在存储器采集完成一个周期信号后开始发送UDP 包。由于不同周期信号的样点数不同(在2 048 ~4 096 之间),UDP包的有效数据个数按理也应不同。但为了简化网络收发逻辑,UDP 发送协议每次固定发送4 096 个数据(将ram中的4 096 个数据全部发出,由接收端根据信号周期接收有效数据、丢弃无效数据),分为8 个UDP包发送,每个包设为固定512 B,并且8 个包加标识标记包的顺序。

UDP在传输数据时不会对数据的完整性进行验证,在数据丢失或数据出错时也不会要求重新传输[5]。为了降低因丢包导致的重建波形的失真度,设计了交织传输策略,具体如图5 所示。

图5 交织传输

图5 中,将存储器中的第0,8,…(即8 的倍数位序)位置处的数据组织到UDP 数据包1 中发送,将第1,9,…(即(8 的倍数+1)位序)位置处的数据组织到UDP数据包2 中发送,其他类同。具体计算公式为

其中Address为存储器的地址,取值从0 到4 095;N为UDP数据包的编号(N 取值为1 ~8);M 为UDP 数据包中的数据位置(M取值0 ~511)。

交织的好处是即便有丢包,波形数据的完整性依然没有破坏。如图6 所示,假设1 号数据包丢失,不交织传输的情况下则有波形的前1/8 个数据丢失,波形完整性破坏明显;交织传输的情况下丢掉的512 个数据点均匀散落在波形的一个周期内,波形依然是完整的,且经过滤波可完全恢复原波形。

图6 不交织/交织传输效果对比

1.3 延时补偿策略

网路延时补偿策略如图7 所示。图中,发送端向接收端发送两种类型的包,延时补偿包和波形数据包(IP包头的Identification 字段分类标识),其中延时补偿包包含信号周期信息和网络延时信息、波形数据包则为信号的样点数据。接收端需要对延时补偿包进行响应,即向发送端回发延时补偿响应包,发送端据此来计算网络延时并更新。接收端接收发送端发来的波形数据包并存入存储器中,根据延时补偿包中的周期和网络延时信息计算需要补偿的相位,决定从存储器的合适位置读取数据输出给DAC 完成波与发端相位同步的波形重建。

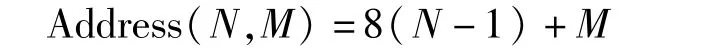

延时补偿包在每次的信号下降沿过零点位置发出,在收到接收端发来的响应包后发送波形数据包。从图7 可以看到,仅有部分波形数据被传输。该策略中,平均的数据传输速率(即网络传输速率)可以用以下公式进行计算:

式中:S 为平均数据传输速率;n =8 为发送一组数据包的个数;TF=556/125 M 为发送一个数据帧需要的时间;TIFS=2 ms为帧间隔时间等于固定间隔时间;Tl为网络响应时间;Ts为信号周期;k∈(0,1),kTs表示等待下一个信号下降沿过零点的时间;l =512 为有效数据的字节大小。其中,2 ms的帧间隔保证UDP包传输稳定。经计算可得平均传输速率最大时为270 KB/s(对应的5 kHz输入信号)。

图7 发送端延时补偿策略

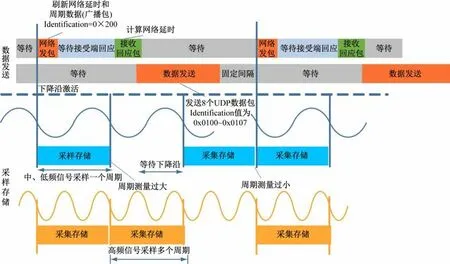

2 系统搭建验证和结论分析

系统搭建框图如图8 所示,收发系统实物如图9所示。发送端由ADC、FPGA、GPHY 组成;接收端由GPHY、FPGA、DAC组成。信号源输出信号,经发送端处理后经交换机网络传输到接收端,接收端补偿时延后重建波形经DAC 输出到示波器显示。示波器两路同时显示信号源发出的信号和经过接收端重建的信号。

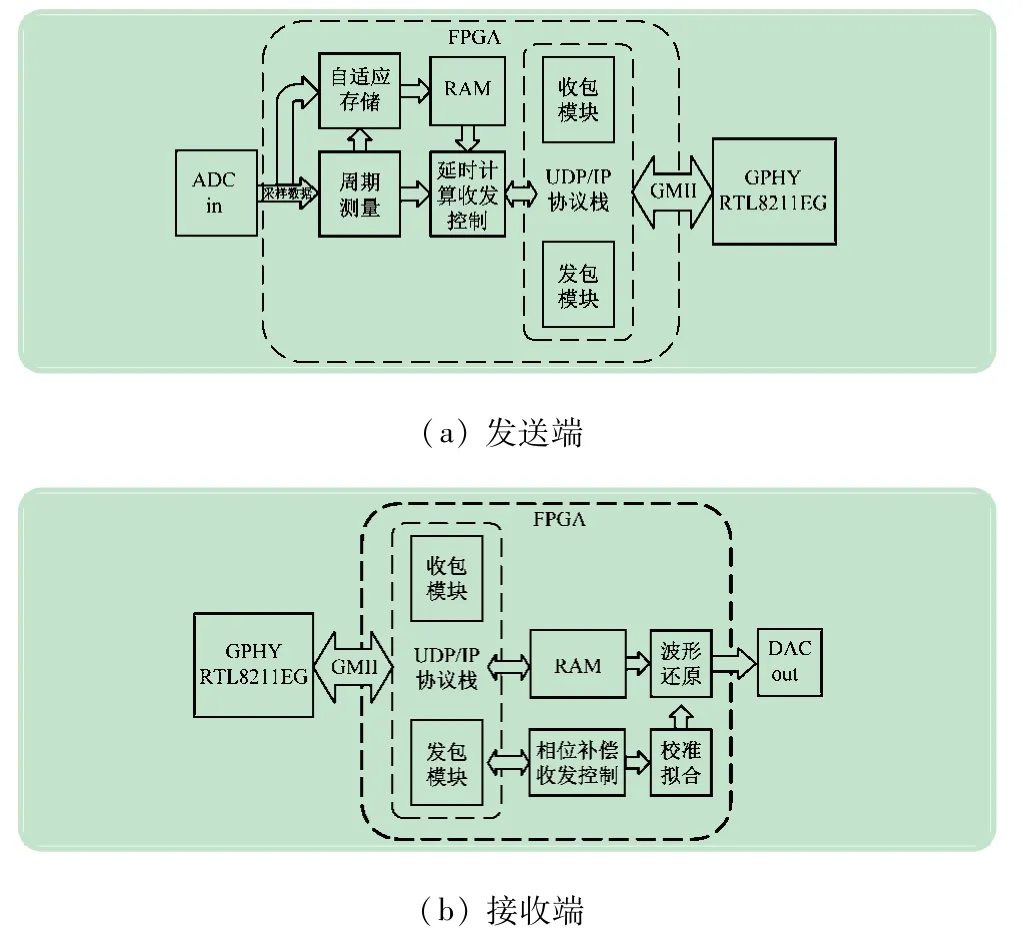

发送端FPGA 程序设计如图10(a)所示,主要包括模拟信号采集、周期测量、自适应存储、延时计算及收发控制、UDP/IP协议栈[6]。接收端FPGA的程序设计如图10(b)所示,包括UDP/IP 协议栈、相位补偿及收发控制、校准拟合、波形重建。

图8 系统搭建框图

图9 收发系统实物图

图10 FPGA程序设计框图

使用以太网交换机模拟互联网,实际测试结果如下:

(1)UDP丢包情况。当UDP发包过密时,丢包会较严重,出现过8 个包丢3 或4 个情况。当发包间隔大于2 ms时,8 个数据包丢包在1 个及以下。

(2)网络延时测量及误差分析。发送64 byte 的UDP数据包,在网络负载为1%的情况下经过一个交换机的网络延时为22 μs;经过两个交换机的网络延时为43 μs,有±0.3 μs的波动。随着UDP 发包间隔的增大,网络延时的抖动会明显减小。

(3)再生信号的周期误差。再生信号的周期误差来源于发送端对信号周期的测量误差(测量方法本身的误差和叠加在信号上的噪声的影响)和收发两端的FPGA时钟源,接下来主要分析后者。时钟源有准确度、稳定度两个技术指标,准确度反映实际频率值和标称频率值的相对偏差,稳定度表示给定的时钟源的频率在一段时间内相对于平均频率偏差或波动的统计描述[7],时钟源的时钟周期为Tclk(约为0.1 μs)表示为Tclk=Tfix+TΔ。其中:Tfix为固定的部分,由准确度决定;TΔ为时变部分,取值范围由稳定度决定。收发两端时钟源的时钟周期差使得再生信号的两个相邻样点间的时间间隔与发端的采样时间间隔不一致,导致重建信号与原信号之间的周期误差。周期越大,测量的点数越多,周期误差的绝对误差越大。虽然题目仅要求周期的相对误差在10%以内,但是再生信号的绝对周期误差的累计会导致相位误差。

再生信号的周期误差理论分析如下:

设发送端FPGA的基准时钟为fclk_t,周期为Tclk_t;接收端FPGA的基准时钟为fclk_r,周期为Tclk_r。当信号源输出的信号频率为f,周期为T时,发送端测得的该信号在fclk_t下一个周期的点数为T/Tclk_t,记为M;接收端收到后以Tclk_r间隔给DAC,再生的信号周期为Tclk_r(T/Tclk_t)。因此,再生信号的周期误差为Tclk_r(T/Tclk_t)- T,误差最大值为T(Tclk_r/Tclk_t- 1)+Tclk_r。

(4)再生信号相位同步误差分析。题目要求再生信号与原信号的相位延时小于10 μs。再生信号与原信号的相位差主要取决于两个因素:①再生信号与原信号的周期误差的累积;②网络延时导致的相位差。

受收发两端FPGA 时钟源的影响,时延补偿误差分析如下:

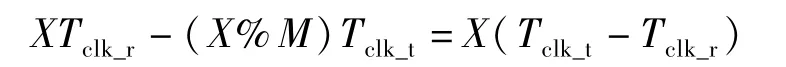

发送端计算的时延为X 个Tclk_t,接收端计算相位补偿公式为X%M,即补偿的延时为(X%M)Tclk_r,则时延补偿误差为

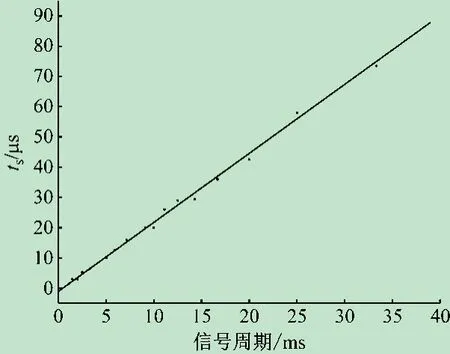

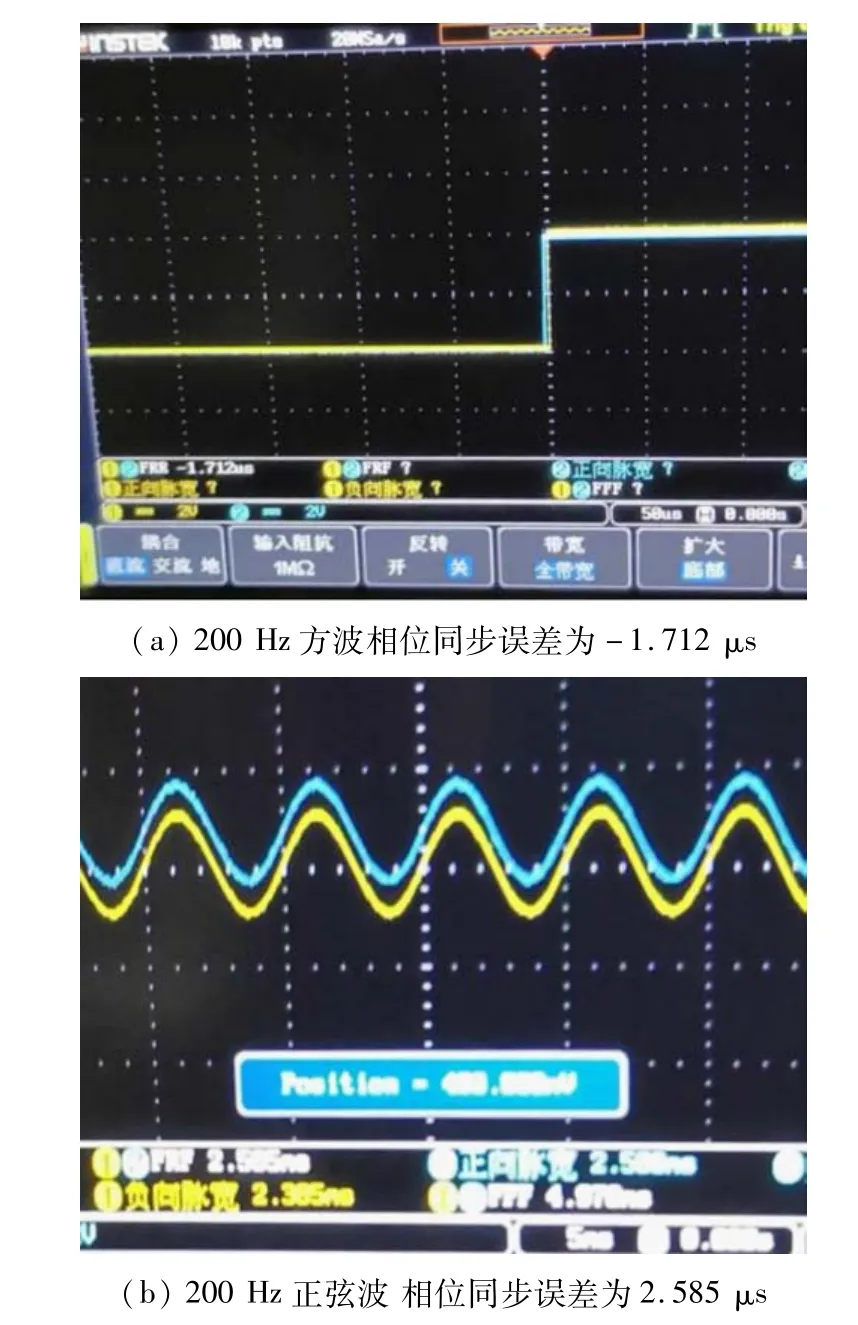

再生信号的周期误差为T(Tclk_r/Tclk_t-1)+Tclk_r,与时延补偿误差相比,周期误差在低频时更显著,成为再生信号与原信号相位差的主要因素。网络延时补偿后的实测结果如图11 所示。可以看到,收发信号的相位差和信号周期呈近似线性关系,与理论分析相符。针对此,设计中进行了校准拟合,最终使得收发信号之间的相位误差降低在3 μs 以下,最终结果如图12 所示。图12(a)误差为1.7 μs,方波周期为5 ms,图12(b)误差为2.585 μs,正弦波周期为5 ms,蓝色波形带有400 mV的偏置显示。

图11 仅补偿网络延时情况下的再生信号与原信号的相位差

图12 校准拟合后相位延时结果图

3 结 语

本文主要描述了在使用FPGA进行信号采集和信号经过以太网传输后的再生及相位同步问题的相关研究。设计中,为使系统能处理更宽的信号频率范围,采用了自适应存储策略,节省了存储空间和网络传输带宽;同时为应对网络丢包导致的波形数据失真,采用了交织传输策略。最终对系统进行了实际搭建和验证,并对实测结果进行了理论上的深入分析,具体分析了误差的产生来源和计算方法,并采用校准拟合的方式降低了信号同步误差。

整个工程使用Verilog 语言编写实现,采用PC 端与FPGA调试两者统筹兼顾的方式对模块的功能进行了实际的验证。通过测试输入输出信号,实现了8 位宽度数据,10 M采样时钟,可以几乎无失真地传输两路0.2 Hz ~2 MHz的矩形、正弦、三角波周期信号,收发信号相位同步误差在3 μs以内。