一种微机电封装中粘接层间剥离应力计算方法

封宝柱,戴 强,罗钧文

(西南科技大学制造科学与工程学院制造过程测试技术—省部共建教育部重点实验室,四川 绵阳 621000)

1 引言

近年来,微纳机电系统成为了研究热点。然而,在微纳机电系统的封装中,由于衬底—封装胶—芯片力学与热学参数的失配,在芯片工作时,随着温度的改变,会在衬底—封装胶—芯片各层间引起应力,而较大的应力会在封装胶层引起裂纹和脱层[1]。关于封装胶层应力的研究,文献[2]最早提出了两层具有不同力、热材料属性且紧密结合的双金属片理论,文献[3]基于以上理论,提出了多层的圆形基板和芯片胶粘结合的应力计算方法,文献[4-6]的理论方法,使用结构分析的方法计算封装胶层间的应力获得了闭合形式解。文献[7-9]中剪切柔量的计算进行了改进,取得了理想的结果。基于以上研究,发展了一种新的剥离应力计算方法。

2 粘接层界面应力模型

2.1 剪切应力

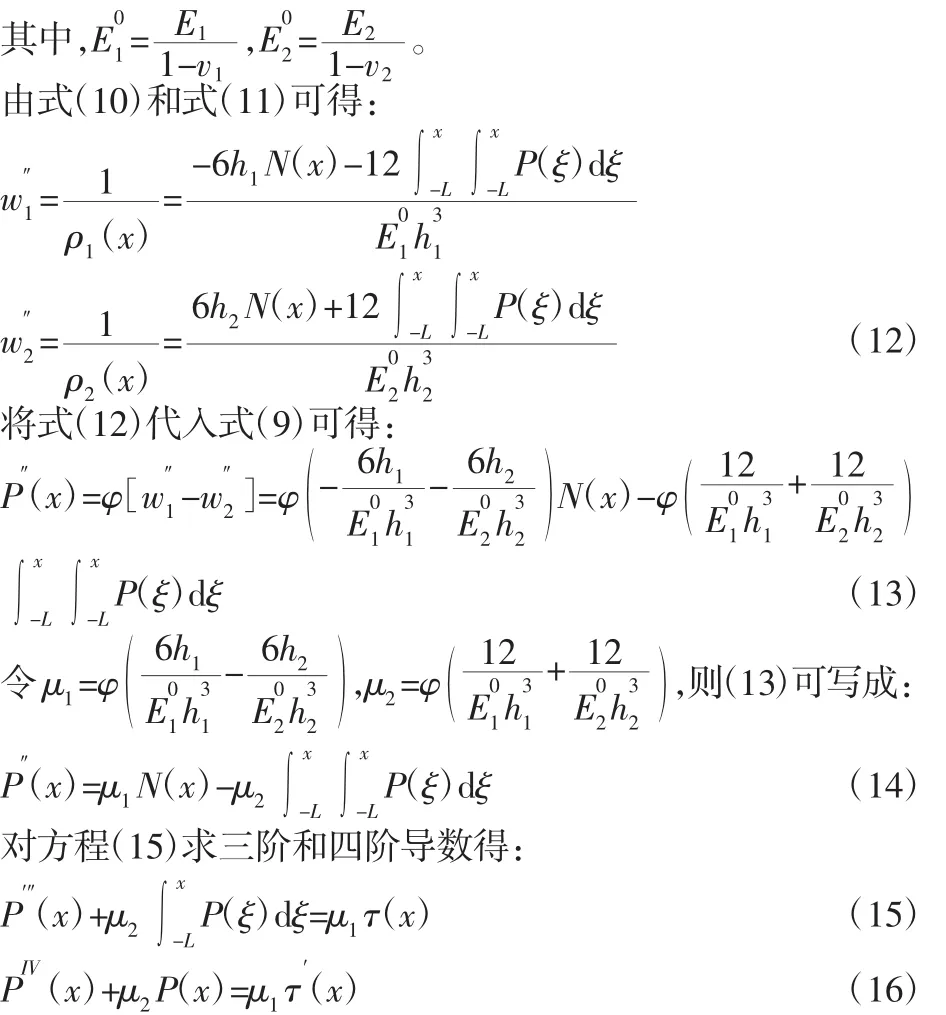

因电子封装中各材料的热膨胀系数(CTE)和弯曲刚度不同,所以在加载不同的温度时,基底、芯片和粘接层会相对于中心产生膨胀、收缩或者弯曲,导致界面之间会产生平行于界面的剪切应力τ和垂直于界面的剥离应力P,同时芯片和基板截面上受到温度变化时产生的热应力Ni作用,如图1所示。由于封装粘接层的厚度与芯片和基板的厚度相比非常的薄,所以在下面的计算分析中忽略了粘接层对界面应力的影响。

图1 基板-粘结层-芯片应力分布图Fig.1 Internal Forces and Strain in Trilayer Assembly

在均匀变化的温度ΔT作用下基底和芯片沿x方向位移由四部分组成:(1)温度变化产生的变形位移 αiΔTx;(2)热应力产生的位移剪切应力产生的剪切位移 κiτ(x);(4)弯曲变形产生的位移式中:αi—材料的热膨胀系数—材料的拉伸柔量;E—材料的杨氏i模量;vi—材料的泊松比;hi—芯片、基板和粘接层厚度;—材料的剪切柔量—材料的剪切模量—芯片和基板的挠度函数,i=0,1,2。

所以芯片和基板沿x方向的总位移为:

方程(6)的通解为:

式中:C1,C3—常数。

根据边界条件x=L 处 N(L)=0,x=0 处 τ(0)=0 可得:

2.2 剥离应力

因为剥离应力是由各种材料之间变形时不同的偏转所引起的,所以我们认为剥离应力与芯片与基板的挠度相关即:

可以求出微分方程(16)的一个特解为:

在连续弹性基础上的梁理论中方程(16)的常系数齐次线性微分方程的通解为:

由方程(17)和(18)可得方程(16)的通解为:

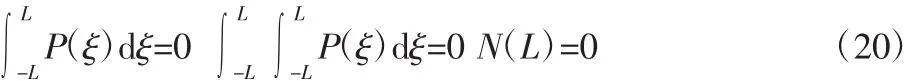

因为剥离应力 P(x),N(x)必须相对于原点对称,并且 P(x)满足于侧向力和弯矩的平衡条件所以:

弹性分析中,剪切应力在不同连接材料的几何边界处会出现应力奇异性[11],所以:

3 有限元仿真

3.1 三维有限元模型

为了验证以上模型,采用ANSYS Workbench有限元仿真软件进行仿真。由于模型具有对称性所以仿真时采用四分之一模型,如图2所示。

图2 模型Fig.2 Model

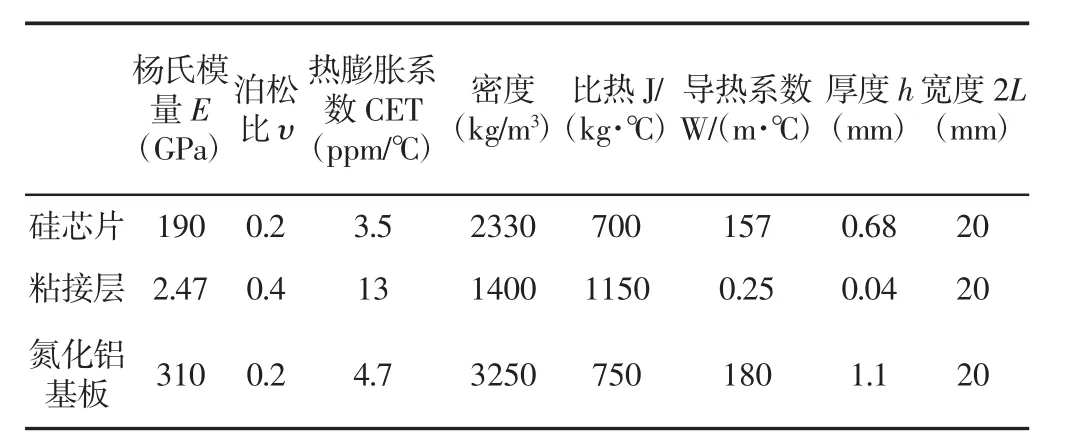

在热应力仿真过程中,粘接层间界面处的对应点相互耦合,各材料的弹性模量、热膨胀系数、泊松比以及热传导系数等均是其固有特性,如表1所示。

表1 材料属性Tab.1 Material Properties

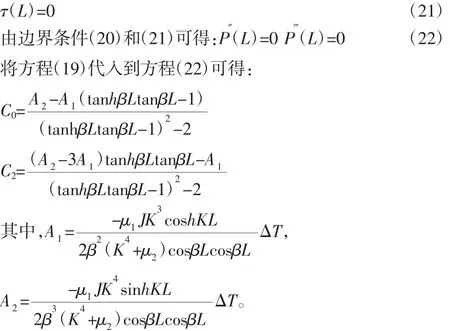

根据要求选用了软件中的热结构耦合模块,单元采用了Solid90单元,网格划分后整个结构共70574个单元,334512个节点。网格划分结果,如图3所示。

图3 有限元网格Fig.3 Meshing

3.2 加载条件

在有限元模型计算中将基板底部平面即Z=-h2平面作为热源,如图2所示。通过对基板底部加载温度使模型达到热稳定状态。将20℃作为结构的应力应变零点,室温设置为20℃。由于是采用四分之一模型仿真,所以将模型的XZ平面和YZ平面设置为对称约束,同时为了防止在热应力仿真过程中模型移动,将基板底部中心点(X=0,Y=0,Z=-h2)设置成固定约束。

3.3 结果分析与讨论

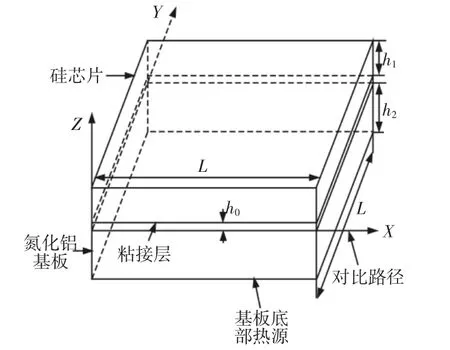

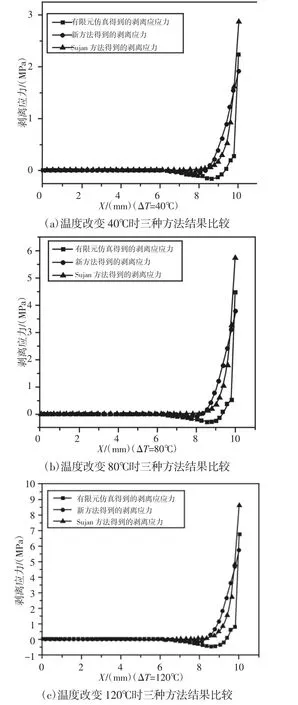

为对比方法、Sujan方法以及有限元仿真这三种方法结果,取封装胶与基板界面层的剥离应力进行比较,路径为x轴方向,如图2所示。计算与仿真时,温度分别从室温变化到60℃、100℃和140℃,即温度变化ΔT分别为40℃、80℃和120℃,结果如图4所示。由图4可知,当温度变化从40℃到120℃时,沿路径从对称中心到整个结构的(60~70)%处,Sujan方法、这里方法与有限元方法三种方法结果比较接近,并且剥离应力均接近于0,如图2所示。在大于70%后,即接近封装结构末端,出现了应力集中。因此,此处为器件损坏和剥离的关键区域。

图4 剥离应力分布Fig.4 Peel Stress

今对比三种方法在应力集中区的结果,在封装结构末端,即(6~10)mm 处进行了放大,发现:(1)随着温度升高,剥离应力也相应增大,当温度分别变化40℃、80℃和120℃,由于材料失配引起的最大剥离应力分别约(2~3)MPa,(4~6)MPa 和(6~9)MPa。(2)这里方法与有限元方法趋势更为接近,这里方法与有限元方法均有先从压应力再到拉应力的过程,而Sujan方法没有;(3)这里方法与有限元仿真最大剥离应力更为接近,当温度分别变化40℃、80℃和120℃时,这里方法与有限元差值分别为0.34MPa,0.67MPa和1MPa,而Sujan方法与有限元差值分别为0.64MPa,1.26MPa和1.9MPa。进一步对比三种方法的最大剥离应力结果,如图5(a)所示。三种方法不同温度差下的最大剥离应力。由图可知,随着温度升高,最大剥离应力也随之增加,由Sujan方法得到的剥离应力最大,有限元方法次之,这里方法最小。

为比较这里方法与Sujan方法相对有限元仿真的差异程度,作如下处理:相对偏差

式中:i=1,2—Sujan方法和这里方法得到的最大剥离应力,结果,如图 5(b)所示。

从图中可以看出,在不同的ΔT下,Sujan方法得到的最大剥离应力相对于有限元仿真的结果的相对偏差在28%左右,新方法得到的最大剥离应力相对于有限元仿真的结果的相对偏差在15%左右。与有限元仿真结果相比较,新方法的结果相对偏差比Sujan方法减小了约13%。

图5 不同温度下的最大剥离应力及相对偏差Fig.5 The Maximum Peel Stress and Deviation at Different Temperatures

图中:PM—有限元得到的最大剥离应力;P1M—Sujan方法得到的最大剥离应力;P2M—这里方法得到的最大剥离应力。

4 结论

得到了一种计算剥离应力的方法。此方法具有以下特点:(1)剥离应力在封装结构中部趋于0,在封装结构末端出现应力集中;(2)在应力集中处,新方法相较经典Sujan方法,与有限元仿真结果更为接近,最大应力相对偏差比Sujan方法减小约13%。该方法提供了一种更为准确的剥离应力计算途径,可兹为预测电子封装内由温度变化产生的剥离应力的大小和分布提供参考。