一种28 Gb/s无电感限幅放大器设计

徐晓宇,林福江

(中国科学技术大学 微电子学院,安徽 合肥 230026)

0 引言

随着物联网和云计算的发展,数据中心的带宽迅速增长。为了承载巨大的数据流量,光链路在数据中心的应用也越来越广泛。作为光链路中光接收机的重要组成部分,限幅放大器接收到跨阻放大器的小摆幅电压信号,放大后传递给时钟恢复电路,确保时钟恢复电路能正常工作。同时为了保证信号传输质量,减少限幅放大器引入的码间干扰,限幅放大器的带宽要足够大[1]。拓展电路带宽的方案有Cherry-Hooper结构、电感峰化技术、有源负反馈等。文献[2]在传统的Cherry-Hooper结构的基础上,调整了反馈电阻的位置,引入一个低频零点,抵消实数极点,使得共轭复数极点成为主极点,拓展电路的带宽。但Cherry-Hooper结构对电源电压要求较高。文献[3]中使用的电感峰化技术会使得芯片的面积很大。文献[4]采用的有源负反馈结构会增加电路的复杂度和功耗。限幅放大器通常采用级联结构满足高增益和大带宽的要求。这种级联结构会累加并放大因器件失配产生的直流失调电压。过大的直流失调电压会影响差分放大器的静态工作点,进而影响差分信号的正常放大,导致输出信号脉冲宽度失真。为了衰减限幅放大器的直流失调电压,电路中会加入由低通滤波器构成的负反馈环路[5]。

本文提出的限幅放大器采用四级三阶级联结构,利用改进的交织有源负反馈拓展带宽。直流失调电压消除电路由低通滤波器和二级运放组成。基于TSMC 40 nm CMOS工艺,提出了一种28 Gb/s无电感器限幅放大器设计。

1 限幅放大器原理

限幅放大器采用级联结构。输入信号经过前几级放大单元之后,信号幅度变大,使得后几级放大单元会进入非线性放大状态,输出信号的幅度由输出共模电平决定,实现限幅功能。限幅放大器采用直流耦合方式。这种级联结构会增大系统的直流失调电压。利用低通负反馈环路降低电路的低频增益,在不影响高频信号放大的前提下,可以有效衰减电路的直流失调电压。

2 总体分析

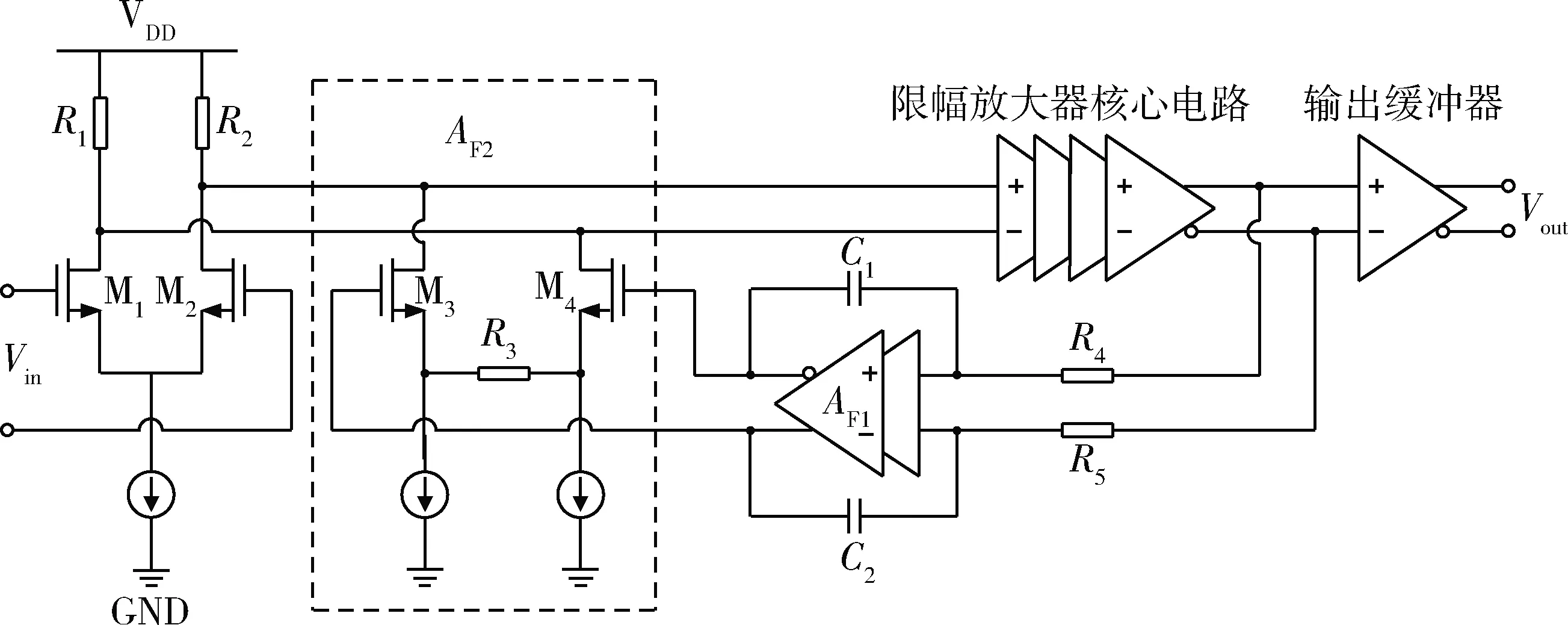

本文提出的限幅放大器应用于28 Gb/s光接收机中,其整体架构如图1所示。对于典型的光接收机,接收光功率为-18 dBm,光电二极管的响应度为0.75 A/W,跨阻放大器的增益为1 000 Ω,限幅放大器接收到的输入信号幅度就是12 mV[3]。为了保证后级时钟恢复电路的正常工作,限幅放大器的增益需要达到40 dB。同时,为了避免引入过大的码间干扰,限幅放大器的带宽需要达到至少26 GHz。直流失调电压消除电路的设计需要考虑到信号传输过程中会出现长“0”信号或者长“1”信号的情况,此时信号的频率较低,低通负反馈环路引入的低频截止频率需要保证在几十kHz才能避免长信号传输过程中出现明显的电平下降[1]。

图1 本文提出的无电感限幅放大器的架构

2.1 限幅放大器放大单元设计

本文提出的限幅放大器在多级多阶级联结构的基础上,采用一种改进的交织有源反馈技术进一步拓展带宽,如图2所示。在有源负反馈环路中的晶体管的栅极插入电阻。例如M11和M12,电阻限制晶体管M11和M12栅极电容对信号通路的影响,提高限幅放大器的带宽。但插入电阻的阻值过大会增加限幅放大器在滚降频率附近的过量增益。

文献[6]和文献[7]讨论了多级多阶级联结构。假设限幅放大器的核心电路由n个相同的m阶具有巴特沃斯频率响应的放大单元级联构成,则限幅放大器的带宽为:

(1)

式中,BWcell表示m阶放大器的带宽。根据式(1),每个m阶放大器的增益带宽积可表示为:

(2)

式中,Atot表示限幅放大器的中频增益。本次设计指标中增益为40 dB,带宽为26 GHz。在实际设计中,限幅放大器采用四级三阶级联结构,由式(2)可知,每级三阶放大器的增益带宽积为108 GHz。TSMC 40 nm CMOS工艺的fT大约为340 GHz,每级三阶放大器的增益带宽积的设计目标小于fT的三分之一,理论上可以实现设计目标。实际设计得到的三阶放大器的增益带宽积为106.4 GHz。

文献[4]和[7]对交织有源负反馈技术在多级多阶级联电路中的应用进行了稳定性分析。一个采用交织有源负反馈技术的四级三阶限幅放大器可以被拆分成4个拥有不同极点的带有源负反馈的三阶放大器。为了保证限幅放大器整体的稳定性,这4个三阶放大器中的最右侧的极点必须位于复平面的左半平面。最右侧极点需要满足的条件为:

(3)

式中,A0是三阶放大器信号通路中差分对的增益;A1是三阶放大器中反馈网络的增益。分析不等式可得三阶放大器的环路增益必须小于2.3才能保证限幅放大器的稳定性。本次设计的每级放大器信号通路中差分对增益为2.3,反馈网络增益为0.38,环路增益约为2。

图2 应用改进交织有源负反馈技术的放大器核心电路

2.2 直流失调电压消除电路的设计

传统的低通负反馈网络由电阻和电容构成。为了使低频截止频率点达到几十kHz,反馈网络中的电容的容值需要达到0.1 μF数量级,这会大大增加芯片面积。文献[5]将运放和低通滤波器组合,大大减少了所需电容的容值。本文设计的低通反馈网络由低通滤波器、二级运放和一级带有源负反馈的放大器组成,如图1所示。假设限幅放大器为带宽无限大的理想放大器,反馈网络为单极点系统,可以得到简化系统的传输函数为:

(4)

式中,Atot是限幅放大器的中频增益;AF1是二级运放的低频增益;AF2是反馈网络第二级放大器的低频增益;R是低通滤波器中所用电阻的阻值;C是低通滤波器中所用电容的容值。由式(4)可知,系统的低频增益近似为:

(5)

低频截止频率近似为:

(6)

根据式(5)、(6)可知,为了降低低频截止频率点,减小低通滤波器中电容的容值,设计电路时需要降低AF2。但因为第二级放大器的负载电阻较小,为保证第二级放大器的输出摆幅,增大直流失调电压衰减范围,第二级放大器的工作电流较大。所以本文采用源极退化降低第二级放大器的低频增益。同时增大二级运放的低频增益AF1以保证反馈网络对直流失调电压的衰减作用。二级运放为带共模反馈的两级全差分放大器。实际设计中失调电压消除反馈网络采用的电容为160 pF,系统的低频截止频率为42.5 kHz。

2.3 输出缓冲器的分析和设计

输出缓冲器采用fT倍增器结构,以减少输出缓冲器的输入电容对放大器核心电路的影响[3]。限幅放大器的输出信号摆幅设计指标为300 mVpp~400 mVpp,所以输出缓冲器的尾电流源设计成5 mA,负载电阻为75 Ω。

3 仿真结果与分析

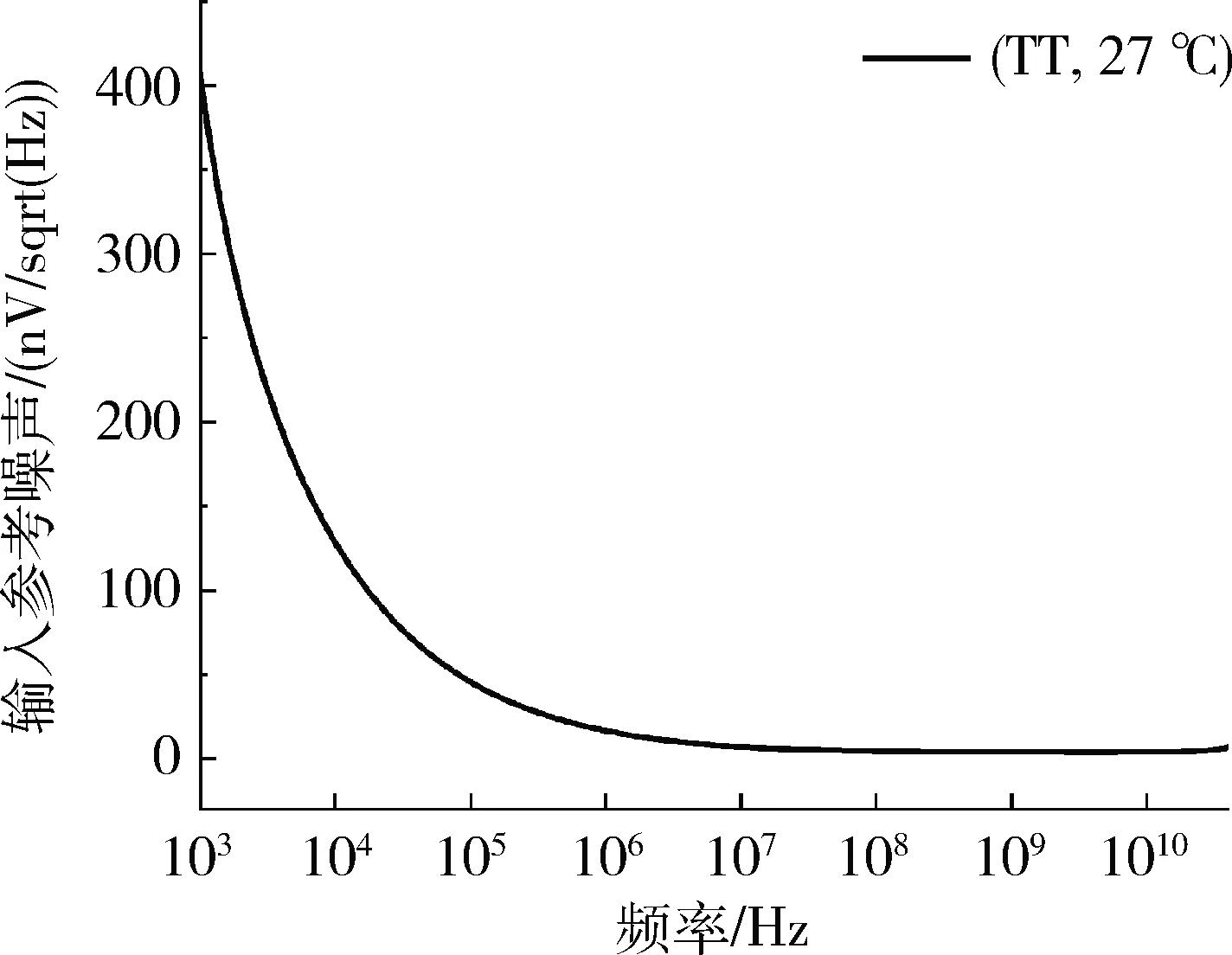

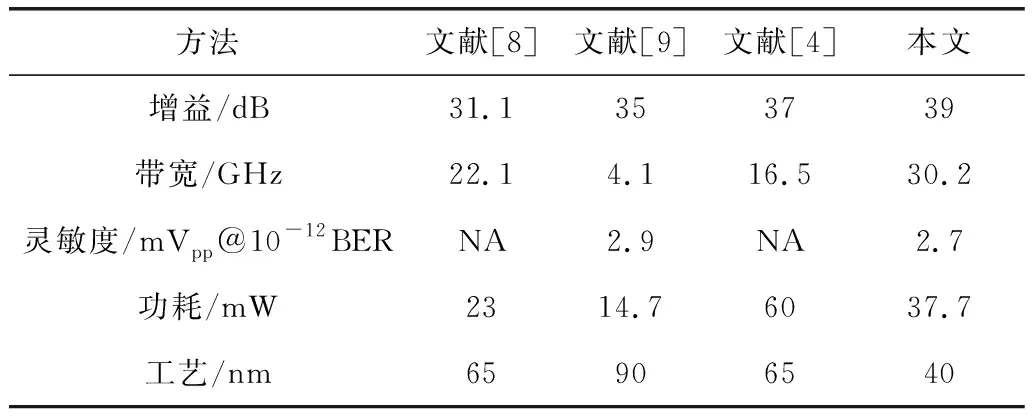

基于TSMC 40 nm CMOS工艺,本文提出了一种28 Gb/s无电感器限幅放大器设计。图3给出了限幅放大器闭环幅频特性曲线。在TT工艺角和27 ℃的仿真条件下,系统的增益为39 dB,带宽为30.2 GHz,低频截止频率为42.5 kHz。图4给出了限幅放大器的等效输入噪声曲线。等效输入参考噪声1 kHz~40 GHz的积分为0.19 mV。根据文献[1],在比特出错概率(Bit Error Ratio,BER)为10-12的条件下,限幅放大器的灵敏度为2.7 mVpp。输入信号源为28 Gb/s的27-1伪随机比特序列(Pseudo-Random Bit Sequence,PRBS)信号,当输入信号幅度分别是10 mVpp和100 mVpp时,输出信号的眼图如5所示。图6给出了限幅放大器输出直流失调电压蒙特卡洛仿真结果。输出端的直流失调电压均值为200.1 μV,标准差为5.8 mV。

图3 限幅放大器的闭环幅频特性曲线

本文设计的限幅放大器与其他文献所设计性能对比如表1所示。

4 结论

图4 限幅放大器的输入参考噪声曲线

图5 输入信号分别为10 mVpp和100 mVpp时的输出信号眼图

本文基于TSMC 40 nm CMOS工艺,设计了一种应用改进交织有源反馈的无电感限幅放大器。在典型值条件下,该限幅放大器的增益为 39 dB, 带宽为30.2 GHz。输出端的直流失调电压均值为200.1 μV,标准差为5.8 mV。误码率为10-12时,输入灵敏度为2.7 mVpp。电源电压为1 V时,限幅放大器不包含输出缓冲器的功耗为37.7 mW。仿真结果表明该限幅放大器具有高增益、大带宽、高灵敏度的特点,适用于高速光接收机。无电感限幅放大器设计可以有效减小芯片面积,降低成本。

图6 限幅放大器输出失调电压蒙特卡洛仿真结果

表1 本设计与其他设计性能对比

方法文献[8]文献[9]文献[4]本文增益/dB31.1353739带宽/GHz22.14.116.530.2灵敏度/mVpp@10-12BERNA2.9NA2.7功耗/mW2314.76037.7工艺/nm65906540