一种26~28 Gb/s高能效低抖动Bang-bang CDR设计

蒋姝洁,林福江

(中国科学技术大学 微电子学院,安徽 合肥 230026)

0 引言

随着万物互连时代的到来,收发系统需要处理的数据流量信息的数量和速度迅速增长,100千兆以太网系统(100 GbE)正在逐渐取代10千兆以太网系统以满足数据流量增长的需要。一个典型的100千兆以太网系统需要4个25 Gb/s的链路[1],本文设计了一款26~28 Gb/s的CDR以满足100 GbE的数据中心需求。

高速串行通信芯片间集成了上百条线,高能效[2]低抖动的时钟数据恢复电路是串行接口速率提升的主要瓶颈。CDR设计的难点主要在以下两个方面:一是设计采用先进的40 nm CMOS工艺,该工艺的电源电压只有1 V,电路实现可用的电压摆幅比较小;与此同时,工艺角变化对器件有较大影响,设计需要覆盖宽的调谐范围。二是时钟产生电路需要驱动较大的鉴相器负载以在高数据速率下实现对时钟和数据的正确恢复。其缓冲电路的功耗是CDR功耗的重要来源之一。

1 CDR系统级分析与设计

1.1 电路整体设计

本文基于短距离高速数据通信应用背景,采用了基于相位跟踪反馈结构的基于锁相环的全速率Bang-bang CDR结构,电路基本结构如图1所示。该CDR环路主要由改进锁存器结构的全速率Bang-bang鉴相器(BBPD)电路、异或门电压电流转换电路(XOR_VI)、低通滤波(LPF)电路以及由电感电容压控振荡器(LC-VCO)电路和时钟缓冲电路构成的时钟产生电路4个模块组成。

图1 全速率时钟数据恢复电路

BBPD将时钟产生电路产生的时钟信号和输入数据的信号相位进行比较,输出相位误差信号通过V-I电路产生电流信号对LPF充放电,与LC-VCO的调谐控制端相连,改变LC-VCO的频率,实现相位锁定,同时用提取出的时钟信号对输入数据重定时,保障时钟信号可以在输入数据眼图的中点实现最佳采样。

1.2 环路系统级分析

CDR环路带宽可以表示为ω-3 dB≈2ζωn,其中:

(1)

(2)

(3)

抖动代表了时钟和数据偏离过零点的情况,是衡量CDR性能的一个重要参数。当输入数据不包含抖动的时候,CDR电路本身会产生抖动,抖动部分来自于LC-VCO的相位噪声及其控制电压上的纹波。这一纹波与压控振荡器的增益KVCO有关。当输入数据包含抖动,抖动容限则体现了CDR环路在不增加误码率的前提下能够容忍的最大输入抖动。根据文献[3]中Bang-bang CDR抖动模型的分析,最大抖动容限可以表示为:

(4)

其中,a=-0.5KVCOIP/CP,b=-KVCORPIP,ωP=1/TP,TP表示采样数据周期。

可以看到在CDR环路中有一个比较大的设计权衡:环路本身的抖动性能会随环路带宽的减小获得改善,但这意味着环路对输入数据中包含的抖动的处理能力也会相对变弱,尤其在面对高频输入抖动的时候。综合以上考量,经过仿真验证,本设计的环路带宽选择为11.3 MHz,IP=1 mA,RP=100 Ω,KVCO=708 MHz/V。

2 CDR环路模块设计

2.1 Bang-bang鉴相器设计

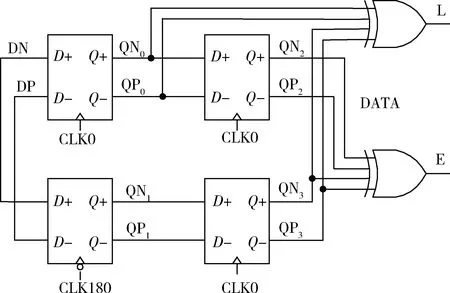

相比于非线性鉴相器电路,传统线性鉴相器电路量化噪声较小,恢复出的数据的抖动性能较好。然而随着CDR速度的提升,传统线性鉴相器会进入亚稳态,受带宽的限制,形成鉴相盲区等问题。在高数据速率通信应用背景下,本文采用输出不随输入数据和恢复出的时钟的相位差的大小变化,并且可以产生大且稳定输出的Bang-bang鉴相器。图2所示的亚历山大(Alexander)鉴相器结构是广泛采用的一种Bang-bang鉴相器结构。

该结构由4个D触发器(DFF)构成,其中每个DFF由两个反相偏置的伪差分电流模逻辑(CML)锁存器(latch)级联构成,由于在40 nm工艺下电源电压比较低为0.9 ~ 1 V,伪差分CML电路相比CML电路可以改善输出摆幅和电源低压之间的折中。其电路结构如图3所示。在触发器的输出路径上引入源极跟随器调整触发器输出的共模点。

图2 Alexander鉴相器

为了进一步优化时钟负载路径和鉴相器功耗以及采样输出的逻辑电平,通过对Bang-bang鉴相器工作状态的分析,本设计采用优化的由7个锁存器构成的BBPD结构,如图4所示。

图5分别表示了7-latch BBPD当时钟信号超前和滞后数据信号时相位比较的结果。相比亚历山大鉴相器,在不影响输出电平的情况下,优化了一个锁存器负载。

1.猪流行性腹泻(PED)。主要发生于冬末春秋的寒冷季节,以11月份至次年3月间多发,各年龄的猪均易感染,1~5日龄内仔猪感染率最高,症状严重,病死率也最高。病猪体温正常或稍微升高,精神沉郁,食欲降低,日龄较大的猪症状较轻,日龄较小的猪症状较重。仔猪病初常呕吐,排灰色或黄色粥样或水样稀便,恶臭。剖检病死猪可见小肠肠管胀满,充满黄色内容物,肠壁变薄,肠系膜呈树枝状充血,肠系膜淋巴结水肿。

图3 伪差分CML DFF

图4 7-latch BBPD

图5 改进Bang-bang鉴相器工作示意图

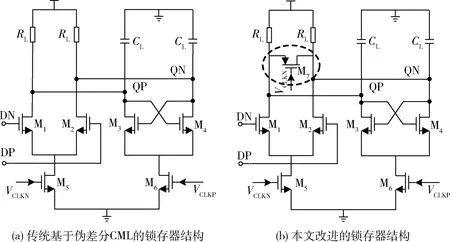

传统的基于伪差分CML的锁存器结构如图6 (a)所示。在采样和锁存阶段共用电阻负载,采样阶段差分对需要对输入数据放大直到达到锁存阶段可以实现正确锁存功能的最小电压,采样阶段的时间常数可以表示为τP=RLCL。锁存阶段需要将这一最小电压放大至CML电路的满摆幅电压ISSRL,锁存阶段的时间常数可以表示为τR=RLCL/(gmRL-1)。在负载电阻的选择上,负载电阻过大,τP增加,输入电压放大和放电的速度都会减慢,不利于高速数据采样;负载电阻过小则会降低直流放大增益和电源效率。本设计采用改进的锁存器结构如图6 (b) 所示。

图6 本设计采用的锁存器结构

该结构在差分输出之间引入一个PMOS开关M7[4],可以适度降低有效负载电阻,不至于在预充电的过程中电阻过小,M7的引入在不影响τR的情况下,减小了τP。这使得改进结构可以快速建立正确输出,防止在高数据速率下磁滞效应对数据恢复的影响。

改进结构的缺点是从PMOS开关控制端到输出的时钟馈通,与此同时,也会引入额外的时钟负载,因此改进CML结构只应用在图4所示的与输入数据直接相连的锁存器链的第一级。最终采用改进锁存器结构的BBPD电路在相同的输入信号条件下采样相同的数据速率,功耗减少了9%。

2.2 异或门和电压电流转换电路设计

异或门将鉴相器采样得到的高速信号进行比较,实现输入数据和时钟相位比较的功能。设计采用如图7 (a) 所示的CML异或门结构,该结构对称性好,在高数据速率下引入较小的静态相位失调。通过式(5)可知,异或门的结果通过输出电流IL产生。

(5)

出于电压摆幅的考虑,设计采用图7(b)所示的伪差分电压电流转换电路,二极管连接的MP1管作为负载与V-I电路构成电流镜,弥补了伪差分V-I电路电流不能精确控制的缺点,通过电流传输的方式提高了异或门和电压电流转换电路整体的工作速度[5]。

图7 异或门和电压电流转换电路

2.3 协同调谐时钟产生模块设计

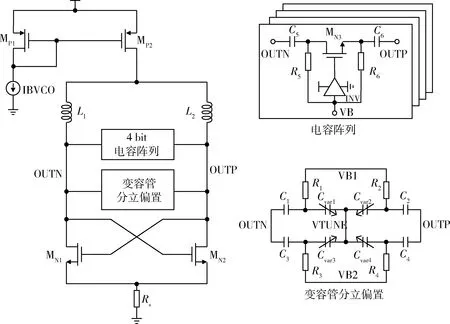

在输入数据无抖动的情况下,CDR主要的抖动产生来自于时钟产生电路。因此环路对VCO的相位噪声有较高要求,结合高数据速率的要求,本文采用相位噪声性能相对较优的LC-VCO。电路结构如图8所示。

图8 LC-VCO结构

设计采用NMOS互补交叉耦合、PMOS顶部电流偏置的LC-VCO结构,为覆盖工艺角和温度(PVT)变化需求,设计采用4 bit开关电容阵列粗调和变容管细调相结合的调谐方式在不恶化相位噪声的条件下覆盖较宽的调谐范围。其中,变容管分立偏置的方式可以改善调谐曲线的线性度,增加有效调谐范围,减小AM-PM噪声转换,提升相位噪声性能,从而改善CDR环路的抖动性能。本文设计的LC-VCO的相位噪声性能如图9所示,在1 MHz频偏下的相位噪声为-104.08 dBc/Hz。

图9 VCO相位噪声

时钟缓冲电路需要提供足够的驱动以保证Bang-bang鉴相器正确实现时钟和数据的恢复。经过后仿真,本设计至少需要驱动50 fF的电容,若采用传统电阻负载CML缓冲电路,该缓冲电路的带宽至少要达到26 GHz,为满足高速工作的需求,该负载电阻取值较小,在输出摆幅一定的情况下,需要较大的电流以实现缓冲电路对大的非线性鉴相器负载的驱动能力;通过缓冲器链将总的传输延时均分到每一级CML电路以获得最小的延时,达到拓展带宽的目的[6]。此过程功耗较大。

图10 电感峰化带宽拓展功能

在高速大负载要求下,为进一步降低功耗,本文创造性地采用压控振荡器和压控振荡器缓冲电路协同调谐的电路结构,在差分时钟缓冲电路中引入和压控振荡器相同的电容调谐阵列进行协同调谐。该缓冲电路结构及其幅频特性曲线如图11所示。通过协同调谐,缓冲电路在25~30 GHz的频率范围内提供了相对稳定的增益,保证缓冲电路对下级电路的驱动。在低电源电压的CML设计中,缓冲电路在较大的负载下很难同时兼顾输出摆幅、环路带宽以及数据速率的影响。根据设计指标要求,缓冲电路仅需要在特定频段实现所需增益而不必在整个带宽内均保持较大的增益特性。电感负载的CML电路可以满足上述需求,但是会面对单独电感负载随负载电容变化比较敏感的问题。协同调谐结构的电容阵列缓解了上述问题,使得缓冲电路有一定的频率变化范围,可以较好地跟踪VCO输出的时钟信号的变化,改善电感负载CML电路随电容变化敏感的同时弱化了大的电阻电容负载对带宽和缓冲电路增益的限制,充分利用了电感峰化特性在不额外增加较大功耗的情况下为下级鉴相器电路提供足够的驱动。

图11 时钟缓冲电路结构及其幅频特性

经过仿真,该缓冲电路消耗电流小于3.5 mA,功耗减小56%以上。

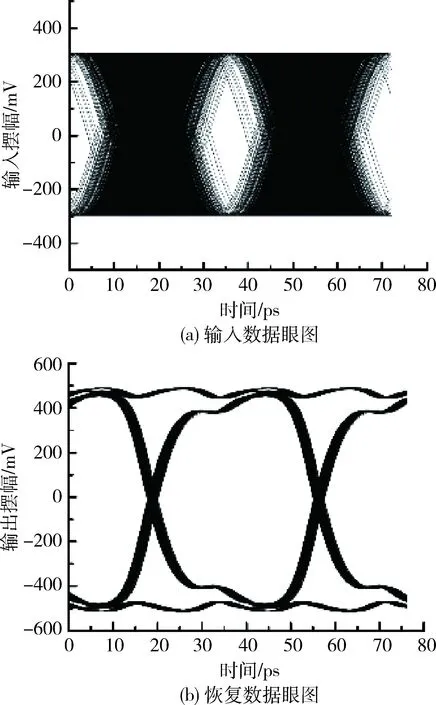

3 仿真结果

本设计基于TSMC 40 nm CMOS工艺,面积大约为0.4 mm×0.43 mm。采用Cadence Spectre对电路进行后仿真。CDR电路输入包含抖动的231-1 28 Gb/s的PRBS数据信号,通过图12可以看出,CDR可以从抖动较差的输入数据中恢复出眼图清晰的数据信号,可以有效抑制92.2%以上的抖动。叠加10 000个周期恢复出的时钟信号和数据信号的眼图如图13所示,恢复出的时钟信号的峰峰抖动为1.66 ps,恢复出的数据信号的峰峰抖动为1.81 ps。

图12 CDR从近乎闭合的输入数据眼图中恢复出眼图清晰的数据信号

图13 CDR后仿真结果

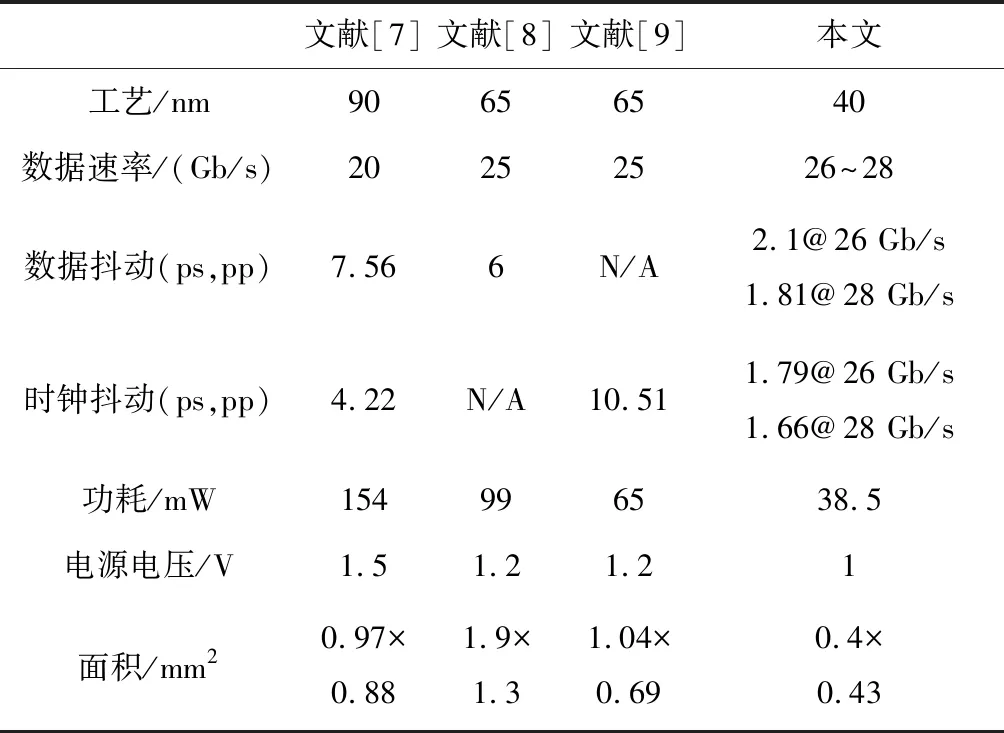

在注入4 MHz正弦抖动的情况下,抖动容限小于0.75 UIpp。在1 V电源电压下,CDR电路的功耗小于38.5 mW,能效可以达到1.375 mW/Gb/s。CDR电路设计指标与近年来的参考文献对比如表1所示。

表1 CDR性能对比

4 结论

本文基于TSMC 40 nm CMOS工艺,设计了一个覆盖26~28 Gb/s的高能效低抖动时钟数据恢复电路,通过仿真结果可以看出,本设计采用的改进结构锁存器的BBPD和协同调谐的时钟产生电路,在相对较低的功耗下恢复出了低抖动的时钟和数据信号。