射频功率放大芯片的静电测试失效研究*

郭 祥,范春帅,赵 雪,王继红,杨 晨,王 一

(1贵州大学 大数据与信息工程学院,贵州 贵阳 550025;2贵州航天计量测试技术研究所,贵州 贵阳 550025)

0 引言

现代社会是一个高度信息化的社会,信息技术几乎深入到了与人类生活相关的所有领域。特别是近20年来移动通信技术的飞速发展,当今社会人类的生产生活与移动通信密不可分,手机已经成为人们工作、沟通、生活、咨询、娱乐等活动的重要工具[1-4]。用于移动通信的射频芯片、处理器芯片、存储器芯片等高技术含量集成电路产品得到了飞速的发展。为了满足移动通信的需求,大量的集成电路芯片被用于制造移动通信设备。这些功能强大且结构复杂的集成电路芯片在制造、封装以及后续的电路组装、应用过程中都需要考虑它们可靠性的问题。其中静电放电(Electrostatic Discharge, ESD)对集成电路芯片的损伤是影响集成电路芯片可靠性的一个关键因素[5-6]。

在集成电路芯片制造、电路组装以及应用的过程中都有工程技术人员与机器设备的参与。然而人体以及机器长时间的活动与运转,在其表面会由于摩擦运动积累大量的电荷。当人体或机器接触到其他接地的物体时会形成一个放电的通路产生伴随着电火花的静电电荷释放现象。这种ESD产生的瞬时电压一般会达到数千伏特,这么高的电压如果被加载到集成电路芯片引脚传递到芯片内部,会对PN节或绝缘栅氧化层造成一定的损伤或破坏,从而影响到集成电路芯片的稳定性以及电子设备的可靠性[7]。因此,模拟人体与机器静电放电的特征测试集成电路芯片的ESD可靠性,研究集成电路芯片ESD失效机制具有重要的意义。本文针对一款国产射频功率放大芯片开展ESD测试研究,并提出相应的抗静电保护方法。

1 实验

基于人体放电模式(Human Body Model,HBM)与机器放电模式(Machine Model,MM)分别对拥有42个引脚的汉天下HS8443射频功率放大芯片进行ESD测试。测试环境温度为25 ℃,相对湿度为55%。将所用的引脚分为Vcc、Gnd、I/O这三类端口,采用I/O静电放电测试方法,对每一个I/O引脚与Vcc(Gnd)分别施加正负ESD电压且每次施加3次。HBM与MM模式分别测试3批次样品。

2 结果与讨论

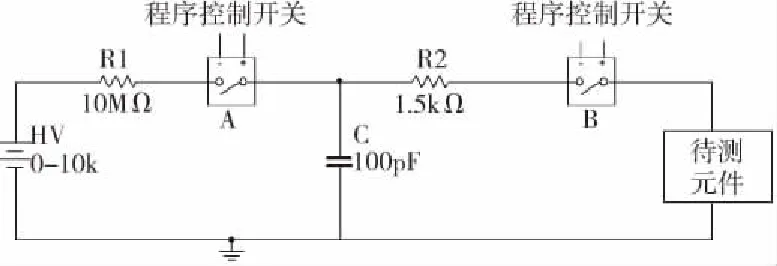

基于HBM测试芯片电路示意图如图1所示,高压静电释放由可编程多路开关控制器控制,两个互补高压继电器实现电路电容的互补充放电过程。当图1中高压干簧继电器A闭合,高压干簧继电器B则断开,高压电源对电容充电;当电容电压达到预定值,如果A断开,B立即导通,电容通过电阻R2对被测芯片放电。高压电源的电压设置范围为±500~±2000 V,每次调压±250 V进行测试。

图1 基于HBM测试芯片电路结构示意图Fig.1 Circuit structure of the test chip based on HBM

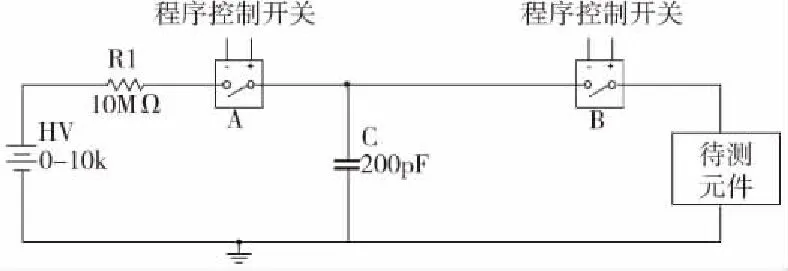

基于MM测试芯片电路示意图如图2所示,与HBM相比电路结构基本相似,区别在于MM的电容为200 pF且放电回路无电阻元件。高压干簧继电器A与B的控制方式与HBM相同,但MM测试高压电源的电压设置范围为±50~±200 V,每次调压±50 V。

在HBM与MM测试之前,对待测芯片的每一个待测引脚测试其I-V特性,以1 μA的输入电流为参考。在测试之后,又分别测试待测引脚进入芯片内部的I-V特性,对比静电损伤测试前后I-V特性,经过HBM或MM静电测试后如果在参考电流为1 μA时输入电压产生了30%的漂移则判定该引脚失效。通过对3组待测射频芯片进行HBM与MM测试发现:HBM测试后引脚TR1在+1750 V电压作用后失效;MM测试后引脚TR1、TR2在+150 V电压作用后失效。其他引脚在HBM测试电压±500~±2000 V以及MM测试电压±50~±200 V范围内均未失效,但是芯片的ESD测试通过电压以最低耐压引脚端为参考。可以看出,此款芯片基本符合行业标准(最低通过电压HBM测试1500 V、MM测试100 V)的ESD测试。

图2 基于MM测试芯片电路结构示意图Fig.2 Circuit structure of the test chip based on MM

测试芯片HBM与MM耐压有较大差异,主要是因为:HBM的放电是由一个RC回路构成,该RC网络有一个特征上升时间和衰减时间,上升时间一般为17~22 ns,衰减时间一般是150 ns;而MM的标准电路中只包含一个200 pF的电容,带电体与器件之间电弧放电,放电的特征上升时间快于HBM,且MM峰值电流显著的高于HBM。根据在3个物理尺度有较大差异平面器件热模型的物理模型(DFC模型)[8-9],器件失效功率Pf可以表示为:

其中,a、b、c为器件特征尺寸(假设c 对于HBM与MM静电释放测试均优先造成了芯片的射频信号收发引脚端失效,这可能与信号输入输出端的电阻特性有关。功率放大电路一般要求具有较小的输出电阻以保证其带负载的能力。基于化合物半导体GaAs工艺制备的4G射频芯片电阻结构有金属薄膜电阻和掺杂GaAs薄层电阻两种结构[9-10],这类电阻会用于射频放大电路的反馈网络、用于静态偏置、用于功率耦合等。当此类结构电阻用于输出功率耦合负载时,在承受较大的电流密度时容易导致电阻元件烧毁。而HBM与MM静电释放正是在极短的时间提供了极大的瞬态电流,静电作用的时间短可以近似为一个绝热的状态[9],短时间的大电流作用导致电阻元件失效。所以射频功率芯片的引脚失效首先发生在TR端,与输入输出耦合电阻的失效有关。 本文通过HBM与MM静电释放测试射频功率芯片,发现其耐压分别为1750 V和150 V,在射频芯片日常的包装、运输以及存储的过程中均有可能造成器件的失效,需要在这些环节做好防静电的措施。此外,相对而言由于射频芯片的TR端更容易产生失效,在芯片实际应用于系统时,要考虑保护TR引脚的在系统防静电措施,避免静电作用于TR引脚端。3 总结