基于FPGA 的信号发生器的设计与实现

李 岩 方 彬 靳自璇 赵勇彪 张红岭

(河北建筑工程学院电气工程学院,河北 张家口075000)

1 概述

现阶段,函数信号发生器已成为现代测试领域应用最为广泛的通用仪器之一。随着数字技术在仪器仪表和通信系统中的广泛使用,可从参考频率源产生多个频率的数字控制方法诞生了,即直接数字频率合成(DDS)。FPGA(现场可编程门阵列)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS 技术,极大地提高了函数信号发生器的性能,大大降低了电子系统的生产成本。

传统的信号发生器设计方案是采用模拟电路、单片机或DDS 专用芯片来实现,虽然有着广泛的应用,但仍然存在着许多缺陷,例如,设计方案成本高、输出波形的种类少、输出信号的频率控制不灵活、系统升级困难等。而且传统的信号发生器还有两个突出问题,一个是通过电位器的调节来实现输出频率的调节,很难将频率调到某一固定值;另一个是脉冲的占空比不可调节。

随着现代科学技术的飞速发展,用户对函数信号发生器提出了越来越高的要求,例如高分辨率、高输出频率等要求,传统的信号发生器已经无法满足这些要求。不论是在生产、实验还是在科研与教学上,信号发生器都是用于仿真实验的最佳工具。因此开发新型信号发生器具有重大意义。本文提出了一种新型的以FPGA 为核心的DDS 信号发生器设计,充分利用uc/GUI 控制方式灵活、FPGA 芯片运算处理速度快的优点,能够通过图形用户界面很好地实现频率、相位、幅度可调、波形变换并且输出信号质量和精确度高于直接模拟频率合成技术和锁相环式频率频率合成技术。弥补了传统信号发生器设计方案成本高、输出波形的种类少、输出信号的频率控制不灵活、系统升级困难等缺陷。

2 信号发生器设计原理

2.1 直接数字频率合成技术的基本原理

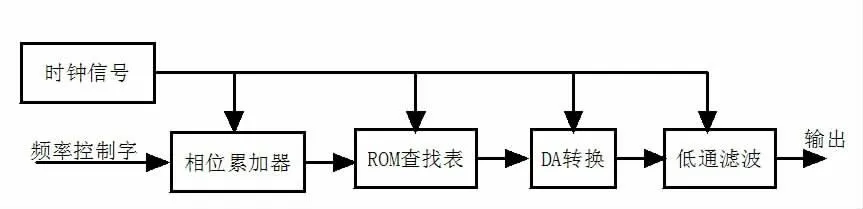

DDS 是一种用于通过单个固定频率的参考时钟信号生成任意波形的频率合成器,必须考虑所有与采样相关的问题,包括量化噪声、混叠、滤波等。DAC 输出频率的高阶谐波会折回奈奎斯特带宽,因而不可滤波,而基于PLL 的合成器的高阶谐波则可以滤波。系统的核心是相位累加器,其内容会在每个时钟周期更新。相位累加器每次更新时,存储在相位寄存器中的数字字就会累加至相位寄存器中的数字。系统在信号合成时,通过改变相位累加器的频率控制字改变相位增量,相位增量的不同将导致一个周期内取样点的不同,从而改变输出频率。在具体的DDS 实现中,通过在采样频率不变的情况下,改变相位累加器的频率控制字,将这种变化的相位、幅值量化的数字信号通过DA 变换及滤波,最后得到系统合成的模拟信号。直接数字频率合成技术主要由频率控制器、相位累加器、波形ROM、DAC 和低通滤波器组成,如图1 所示。

图1 DDS 的基本结构图

2.2 相位偏移控制

由相位累加器送出的相位(地址)经过查表进行从相位到幅度的转换就可以得到需要的正弦波。若在相位累加器的输出相位上加上一个小的数值,那么查表后得到的数据也会相应的超前,也就是说此时的输出波形的相位会相对于原来的波形超前。而且这个超前的相位值应该是和在相位加器输出相位上加的数值成正比的。

3 信号发生器的设计

3.1 信号发生器硬件设计

本文设计了一款uc/GUI 图形用户界面的低成本、扩展性强、易于人机交互的函数信号发生器,把DDS 的技术与FPGA 芯片运算处理速度快的优点相结合,运用适当的算法进行信号调整和电路保护。利用FPGA 更好地实现了处理数据量大、处理速度高的底层信号处理算法,同时更能保证在市场上的生命周期。FPGA 部分实现DDS 核心功能,NIOS II CPU 运行程序实现各种参数的设置和显示。实现一个触控的DDS 信号发生器,具体的输出信号的最高频率与DAC 的转换速率相关。

3.1.1 FPGA 芯片选型

FPGA 是产生函数信号和提供SOPC 系统的核心部分,结合实际需求本文选用的是Altera 公司的CycloneIV 系列EP4CE10F17C8N 型号FPGA 芯片,该芯片具有10320 个逻辑单元,270Kbits M9K 存储块,15 个18x18 乘法器,10 个时钟网络,2个PLL,因此该型号芯片可以适应各类数字信号系统的设计,同时拥有较灵活的时序设计资源。FPGA 是整个系统的核心部分,嵌入了IP 软核的SOPC 系统,能够用可编程逻辑搭建一个嵌入式软核,基于软件的思想利用嵌入式平台的通用性以缩短电子系统的开发周期,高效地实现了目标系统功能。Altera 的FPGA芯片是基于Quartus 平台开发,本文主要涉及函数信号的可编程逻辑设计、QSYS 嵌入式平台的搭建设计。基于FPGA 系统设计主要包括按键消抖设计和DDS 功能模块,根据频率控制字和相位控制字产生对应数据输出。QSYS 是建立在FPGA 芯片内的可编程逻辑上的,它是Altera 公司为其FPGA 上定制实现的SOPC 框架,其基于图形界面的片上系统定义和定制开发流程能大大缩短开发者的开发周期。QSYS 采用Avalon 总线接口实现系统的可扩展性,各种外设控制器如串口、通用输入输出口、存储器、定时器等通过Avalon 总线接口接入系统,此外,QSYS还支待用户开发自己的基于Avalon 总线规范的IP 核,IP 的逻辑由硬件描述语言直接实现,总线接口和总线时序都可由开发者自定义。它定义了一套标准化的接口,称为Avalon 接口,目的是适应各种各样的通信需求,用以连接FPGA 芯片内部的各个组件。将IO 外设的端口映射到接口信号并设置时序特性后,就可以整合到一个Avalon 系统中了。这些接口由互连结构实现,包括译码、多路选择、仲裁和时序逻辑。尽管这种结构通常被描述为共享实体,但是逻辑和路由结构可以利用FPGA 的可编程性以分布式方式构建。连接结构由QSYS 软件工具自动生成,自定义设计需要符合独立系统配置。这种方法消除了对集中资源的竞争,提高了的系统性能。

3.1.2 DA 模块设计

本文系统使用在模拟半导体领域久负盛名ADI 公司的AD9767 型DAC 芯片,该芯片有两个信号输出通道,分辨率为14 位,转换速率为125Msps,支持I、Q 输出模式。芯片输出形式为差分电流输出,输出电流满量程可设置范围为2~20mA。同时该芯片内部自带1.2V 的参考电压,因此芯片工作时无需外部提供参考源。

由于该芯片的输出为电流型,输出范围为2~20mA,而用户在实际使用时一般使用电压信号,因此需要将AD9767 芯片的输出电流转换为电压。对每一路输出都使用了两级运算放大电路,其中第一级完成电流到电压的转换,并执行了一定的放大,将DAC 输出电流转换并放大为-1V~+1V 的电压,第二级为放大电路,将-1V~+1V 的电压信号放大到高达-5V~+5V 范围内。具体信号放大的倍数可通过滑动变阻器调节。

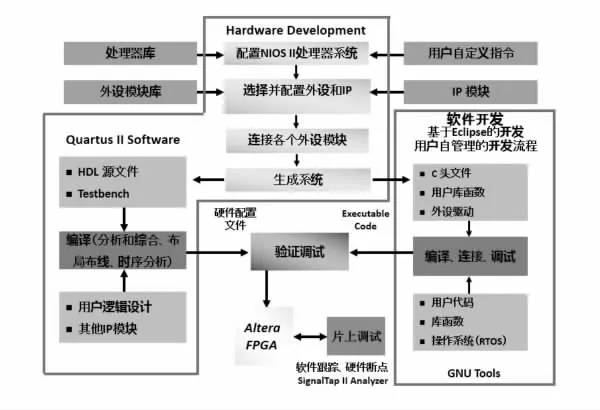

3.2 Nios SBT for Eclipse 软件平台设计

Quartus II 和QSYS 中进行的设计完成了硬件的控制与设备的驱动,这些驱动有的是需自行编写有的是可以直接调用IP核。而基于Nios II SBT for Eclipse 所完成的设计称之为软件设计或软件开发,这种软件开发类似于VC 中的设计,用行为级的设计语言去操作整个系统,而不用多关注硬件的细节,因此也可以称之为嵌入式应用程序开发。Nios II SBT for Eclipse 软硬件桥接工程结构如图2 所设示。

图2 系统软硬件桥接工程结构图

3.2.1 实时操作系统uC/OS II 的移植

uc/GUI 能够在uC/OS II 操作系统中有序的工作,uc/0S II 中多个任务调用uc/GUI 的函数,这样避免了软件造成的线程保护问题。通过uC/GUI 技术文集给出的资料以及官网给的uC/GUI源码开发包,移植uC/GUI 文件夹。

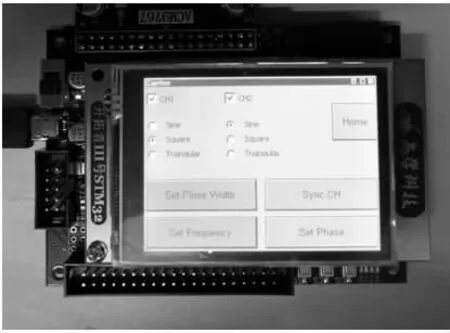

3.2.2 图形用户界面uc/GUI 的实现

在图形用户界面系统设计过程中,本文选用通用的嵌入式图形用户界面软件uc/GUI,可以实现其与uC/OS II 操作系统完美结合。uc/GUI 良好支持大多数的lcd 图像显示器,且消耗较少的系统资源, 占用的RAM 和ROM 空间很小。本系统采用uC/GUI 中一种特殊的控件,对话框控件。在uC/GUI 系统中,一个对话框就是一个窗口,在建立对话框时,必须为每个对话框指定一个资源表和一个回调函数,资源表指定了包含在对话框中所有控件的间接创建函数、控件ID、控件在对话框中的坐标,大多数消息被对话框自动处理了,其它传给了在建立对话框上指定的回调函数。本系统图形用户界面设计效果如图3 所示。

图3 图形用户界面设计

4 软硬件调试与验证

4.1 测试平台搭建

本文设计的信号发生器可以进行脱机操作,只需要一台测试仪就能搭建完整的测试平台。测试仪是一款普通的100M单踪道示波器,该示波器最高采样率是500MSa/s, 带宽为100MHz,存储深度为128kb。

4.2 波形测试结果

在开发环境下生成可执行程序,并通过下载电缆将可执行程序下载到电子系统上,用示波器观察两通道产生的信号波形。

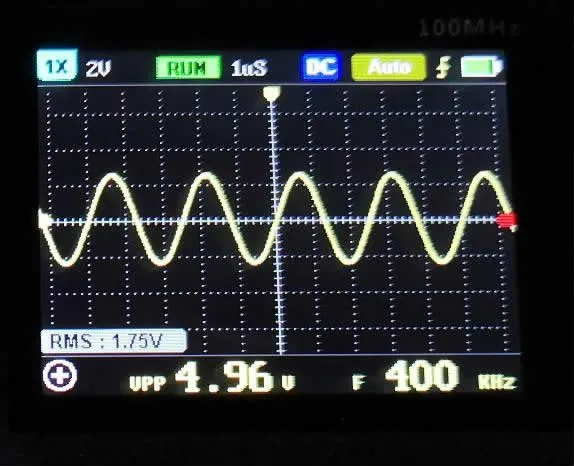

4.2.1 正弦波

对于常用正弦波信号的测试必不可少,设计的信号发生器最高达20MHz 无明显失真,可满足百分之八十的实验测试需求。测试正弦波Vpp 为4.96V,频率为400kHz,波形无失真,如图4 所示。

图4 正弦波信号波形

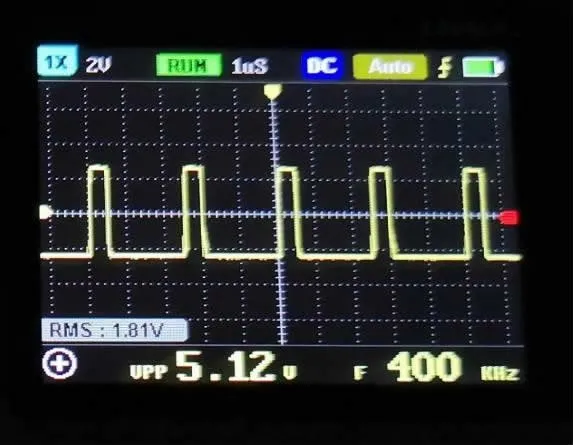

4.2.2 方波

本文设计的触控式信号发生器支持支持方波设定占空比,测试方波Vpp 为5.12V,频率为400kHz,无波形失真现象的出现,如图5 所示。

图5 方波信号波形

4.2.3 三角波

系统产生的三角波信号如图6 所示,可见线性度和对称性较好,无失真现象的出现。测试三角波Vpp 为5.08V,频率为400kHz,波形无失真,如图6 所示。

5 结论

本文基于uc/GUI 图形界面设计了一款低成本、可扩展性强、实现难度低、易于人机交互的信号发生器。整个系统在使用FPGA 的同时还充分利用FPGA 的内嵌资源搭建了一个Nios 软核作为系统控制,控制核心和算法都集成在一块FPGA 芯片上,相对于DSP+FPGA 或者ARM+FPGA 的系统更省功耗,进一步缩减系统板的面积以及缩短了产品开发的周期。

图6 三角波信号波形