一种高速串行信号灵敏放大采样触发器

胡 斌, 刘慧慧, 李玉亮, 欧阳金栋

(1.空军装备部上海局驻南昌地区军事代表室,南昌 330024; 2.江西洪都航空工业集团有限责任公司,南昌 330024)

随着电子信息技术的不断发展,信息传输速度不断提高,数据吞吐量越来越大,常常用到灵敏放大触发器(SAFF)作为采样器件。SAFF是一种由时钟控制的比较锁存器,能够快速地将输入微小摆幅的差分信号放大为全摆幅逻辑信号并锁存,直至下一个时钟跳变沿来临才改变输出,其最早用于高速处理的触发器设计[1]。对于高速串行信号接收器来说,需要在时钟跳变沿时刻对差分信号进行采样,这一特性与触发器类似,所以常采用差分信号灵敏放大触发器实现差分信号的采样。

随着集成电路工艺的不断提升,在SAFF设计的过程中也不断出现新的问题,比如降低功耗延迟比[2-3],解决工艺波动和偏差对参数失配的影响[4-5],以及进一步提升采样速度的研究[6-7],都是需要在新形势新应用环境下不断解决新的问题。另一个要考虑的问题是如何将微小差分摆幅的输入信号如100~400 mV在短时间内提升到电源电压。文献[8]采用多级预放大的方案首先将差分信号放大,再进行锁存。但是高速接口应用的接口供电电压有可能高达3.3 V,如何将微小的输入差分信号摆幅在短时间内提升到输出3.3 V,是一个非常艰巨的任务。在类似应用环境下,如何优化SAFF结构,提升采样速度一直是摆在研究者面前的一个问题。鉴于此,基于0.13 μm CMOS工艺,提出一种改进的SAFF结构,通过增加放电支路,进一步提升了信号采样速率。

1 灵敏放大触发器设计

1.1 传统的灵敏放大触发器结构

传统的灵敏放大触发器结构[9-10]如图1所示。当时钟SCLK为低电平时,实现预充电功能,MP3和MP4导通将N1_typical和N2_typical节点拉高至电源电压,此时输出Q_typical和/Q_typical不变化,继续维持前一个时钟采样时的状态。当SCLK由低电平跳变到高电平时,MP3和MP4关闭,MN5导通,根据D和/D的状态,MN1和MN2相应导通和关闭,则支路①和支路②也会分别导通放电。放电后,N1_typical或N2_typical节点会相应的降低为低电平,使MP1或MP2导通,进一步将N1_typical或N2_typical节点拉高为高电平,形成正反馈,加速输出锁存变化。当D的电压比/D高时,支路①导通放电降为低电平,而支路②不放电N2被拉高至电源电压Vdd,使得逻辑输出Q_typical=0或Q_typical=1。

图1 传统的灵敏放大触发器结构

在该传统的灵敏放大触发器结构中,当Vdd较低时,N1_typical(N2_typical)的电压能快速降低为0,满足高速采样的需求。但是,当Vdd较高时,由于寄生电容存储的电荷过多,导致N1_typical(N2_typical)节点电压不能实现高速变化,影响了采样速度,不能满足高速采样的需求[11-14]。

作为差分信号采样锁存器应用,差分采样模块最主要的指标是有效的采样信号差分阈值和延时[15]。差分输入摆幅越大,延时越小;反之,差分摆幅越小,延时越大。

(1)

节点N1的电压ΔvN1变化不仅与节点的等效电阻RN1和等效电容CN1有关,还与放电速度i1有关,而放电速度与差分输入电压摆幅Δvdin的平方、MN1晶体管的宽长比W/L及工艺参数kn成正比。因此,要减少灵敏放大触发器延时,在一定的工艺条件下,增加输入差分电压摆幅,减少节点等效电阻和电容,是最直接、有效的方法。在实际设计时,增大W/L虽然会使得放电电流增大,但也会导致等效电阻电容增大,得不偿失。另一方面,由于传输链路的衰减作用,输入差分输入信号的摆幅通常较低,必然会影响触发器正确采样。

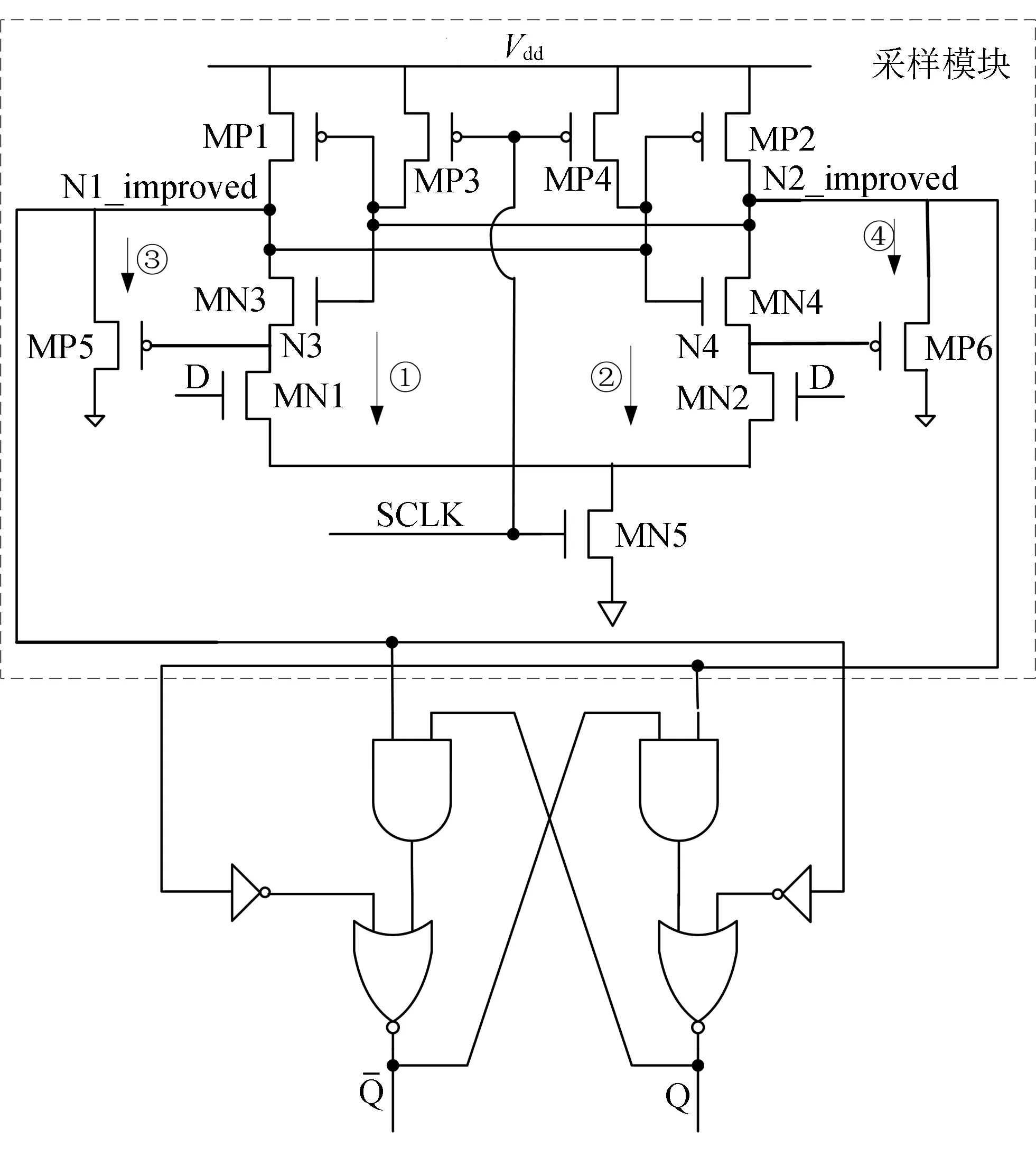

1.2 改进的低延时灵敏放大器结构

改进的低延时灵敏放大触发器结构如图2所示。在传统灵敏放大器结构的基础上,通过增加MP5和MP6两个晶体管,增加了2条放电支路③和④,当节点N1_typical(N2_typical)开始放电时,节点N3(N4)的电压也会相应降低,从而MP5(MP6)导通,通过支路③或④放电,能够加速节点充放电,减少了节点N1_typical(N2_typical)过驱动电压的恢复时间,降低了灵敏放大器的传输延时,从而实现更高速度的信号采样。此时,节点N1的电压变化可表示为

(2)

节点N1的电压变化不仅与差分输入摆幅电压的平方成正比,也与节点N3的电压变化的平方有关,从而实现电压快速变化,满足高电源电压条件下高速采样需求。

图2 低延时改进灵敏放大触发器结构

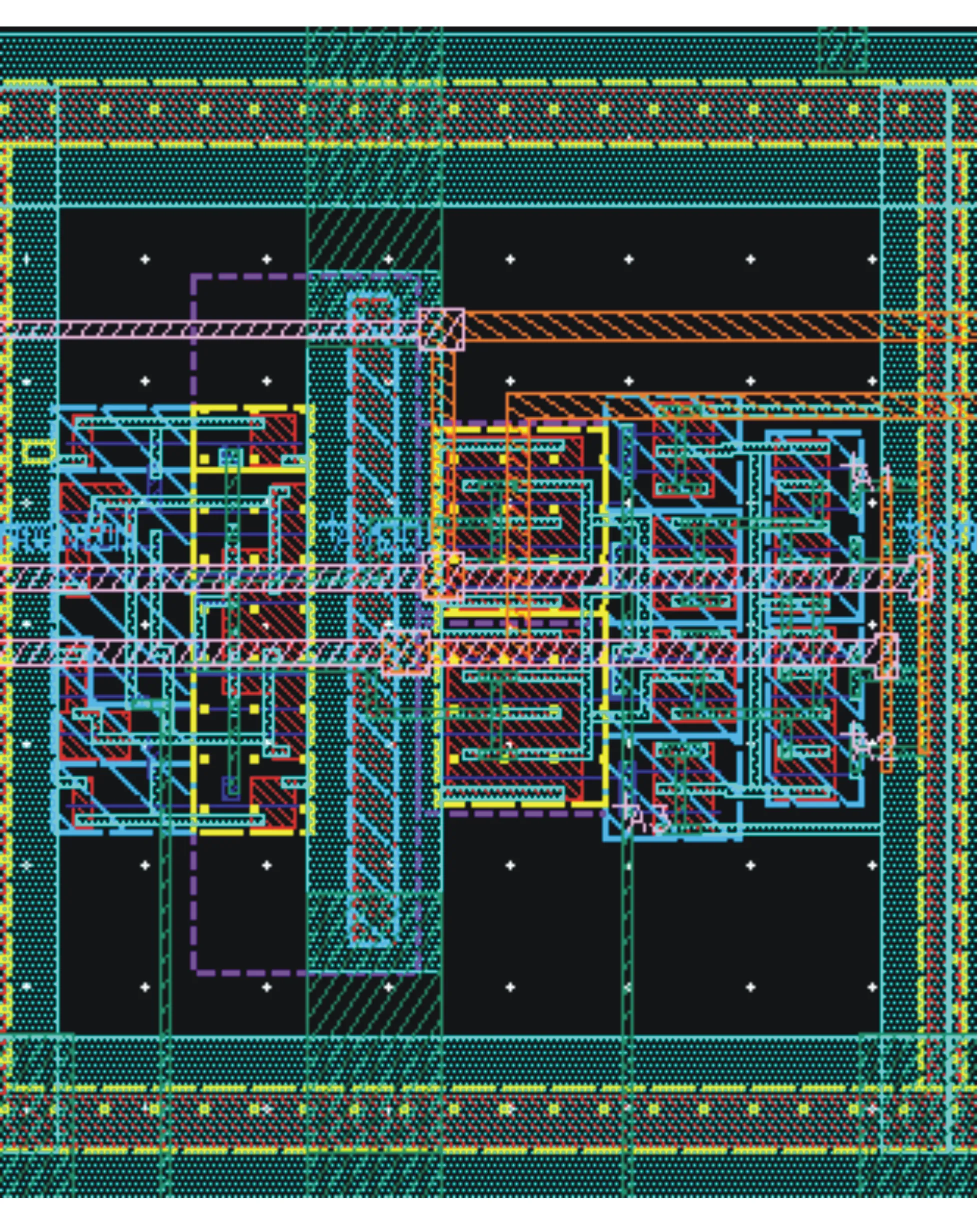

图3为改进的灵敏放大触发器版图,面积为17×35 μm2。版图设计时,采样部分需保证严格对称,以减少输入失调的影响。另外,为了避免模块相互之间的干扰,设计了P+阱隔离。

图3 改进的灵敏放大触发器版图

2 灵敏放大触发器仿真

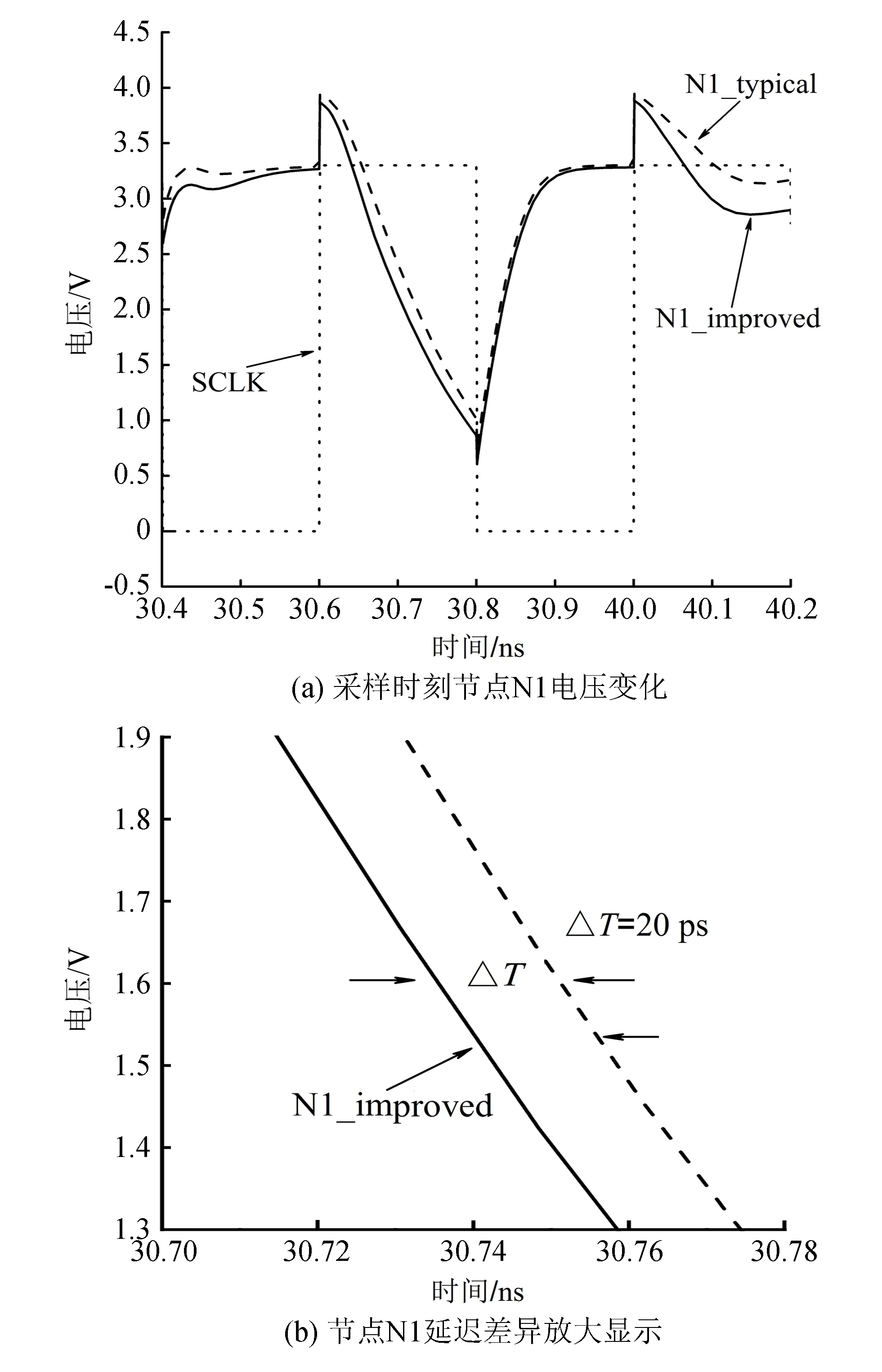

基于0.13 μm CMOS工艺设计灵敏放大触发器,电源电压为3.3 V。传统灵敏放大触发器和改进后的灵敏放大触发器的延时仿真如图4所示。

图4 灵敏放大触发器采样延时仿真

输入激励设置采样时钟SCLK的周期为400 ps,输入差分信号D和/D的差分电压摆幅为400 mV。从图4可看出,当SCLK为低电平时,开始充电上拉,节点N1的电压上升速度基本相同;当SCLK为高电平时,节点N1开始放电,但改进后的灵敏放大触发器结构的N1节点(N1_improved)放电速度要快于传统的灵敏放大触发器结构中的N1节点(N1_typical),使得改进后的触发器放电延时明显小于传统的灵敏放大触发器。

在电源电压和采样时钟不变的条件下,降低差分输入摆幅,改变输入差分信号D和/D的差分电压摆幅为300 mV,灵敏放大触发器采样输出仿真如图5所示。从图5可看出,在传统的灵敏放大触发器结构中,由于节点N1_typical的放电速度慢,当差分电压摆幅过小时,无法正常充放电并采样,输出结果Q(conventional)无法在1/2时钟周期内上升到高电平阈值,使得采样输出出现错误;而改进的灵敏放大触发器结构的节点N1_improved放电速度快,虽然差分输入摆幅降低,但仍能正常地快速充放电、采样并输出正确结果,信号Q_improved能够在半个时钟周期内上升到高电平阈值,采样结果正确。另一方面,改进的灵敏放大触发器的时钟到输出Q的延时Tck-q更小,更适合高速串行信号采样的应用。

图5 灵敏放大触发器采样输出仿真

3 结束语

提出了一种在较高电源电压条件下低延时的灵敏放大触发器结构,在传统的灵敏放大触发器结构的基础上,增加放电支路,实现了高速采样较低输入差分电压摆幅信号的功能,为高速串行接收器的差分转单端采样功能提供了一种可行的设计。