电子束扫描线圈高速驱动器研制

杨波,许海鹰,桑兴华

(中国航空制造技术研究院,北京 100024)

0 前言

电子束高速扫描是实现背散射电子成像、电子束图像扫描、电子束多束焊等技术的基本要求。控制电子束高速扫描在电子束增材制造、电子束物理气相沉积(EBPVD)等领域也有重要作用[1-2]。目前国外在电子束高速扫描的研究领域上较国内领先,且已达到工程化应用。以德国SST公司所研制的电子束高速扫描装置为例,该装置工作频率可达100 kHz,最大输出电流±8 A,直流供电电压160 V[3]。相比国内成熟的电子束焊机上所配备的扫描系统,其频率基本在10 kHz以内,驱动电流大多小于2 A。因此,研究电子束高速扫描技术,研制一套控制电子束高速扫描的装置在打破国外技术垄断,实现高端设备国产化上具有重要现实意义。电子束高速扫描装置包括信号发生器、高速驱动器及偏转扫描线圈,其中高速驱动器是核心部件,是影响电子束扫描性能优劣的关键因素。由于电子是在磁场中受到洛伦兹力的作用发生偏转,在洛伦兹力公式中,电子电荷量及电子速度均为定量,从而改变磁感应强度成为改变电子所受洛伦兹力大小的唯一方式。为实现电子高速偏转扫描,必须要实现扫描线圈中的磁感应强度高速变化。由于扫描线圈等效为电感器,实现其磁感应强度快速变化亦即需要实现电感电流快速变化。因此,要求驱动器能够处理来自波形发生器的高速变化的电流给定信号,同时需要驱动器主回路中电流能够高速跟随给定信号,实现高速变化的电流闭环调节。

文中将根据通用型运放的工作特点、功率晶体管的工作状态及负载特性,分别设计高速跟随的输入级电路、高速动态电流闭环电路及输出电流能高速响应输入信号的主回路电路,并通过Cadence进行电路仿真,优化电路参数,最终实现电路在100 kHz下输出±2 A驱动电流。

1 高速驱动器电路设计

1.1 高速响应输入级电路设计

高速驱动器的输入波形信号来自波形发生器。通常该信号不会直接用作闭环调节,一般先经过由运算放大器及电阻电容构成的差分运算放大电路进行阻抗变换、干扰信号处理后,输入下一级电路中。而采用运算放大器处理高速信号,尤其为高幅值阶跃信号时,电路性能显著受到运放的转换速率SR制约。在运放的SR较低时,其输出电压无法快速通过负反馈电路匹配输入信号,使得输出波形失真。采用高速运放,可以有效提高电路的高频特性。而对于常规运放,由于SR的限制,输出电压无法快速改变。因此,文中通过降压的方式,降低运放输出电压值,亦即降低运放增益的方式减小转换时间。输入级电路如图1所示。

图1 输入级电路

电路由TL082及电阻电容组成,此处Vin电压最大幅值为±10 V,经低寄生参数电阻R1,R2组成的分压电路衰减成±1 V电压信号,通过R4,R3与TL082形成1∶1负反馈电路,TL082输出电压最大幅值为±1 V。TL082的SR为16 V/μs,-1~1 V的理论增长时间为125 ns[4]。

由于电路输入端接收高速突变信号时,在信号的突变沿处,电路输出波形将出现超调现象。为有效减小这部分超调产生的波形失真,在电路中加入补偿电容C1,图1所示。U1的7脚通过给C1充电,调整其电压上升速度,使7脚匹配6脚电压的动态变化速率,改善输出波形。将C1取值为10 pF,其与R3的时间常数为100 ns,此参数对电路的上升时间影响不大。

电路输入端Vin信号先通过R1,R2电阻分压后进行1∶1反向比例运算,而非直接通过10∶1反向比例运算,原因为若采用10∶1反向比例运算电路,在输入信号为方波信号,且发生电压阶跃时,输入信号将通过反馈电阻施加到运放输出端,使得运放输出电压出现尖峰,具体过程将在后续章节的测试波形中进行分析说明。

1.2 高速任意波形闭环调节电路设计

由于驱动器工作于高频动态过程中,电路的输入输出信号均为高速任意波形。在如此快的响应速度下,常规PI调节方式基本无法正常工作,采用PI调节将使电路产生严重振荡现象,输出波形大幅失真。为有效解决上述问题,实现驱动器输出电流波形可靠跟随输入信号,设计电路如图2所示。

此闭环调节电路由运算放大器TL082,推挽三极管BC327,BC337,以及二极管、电阻、电容组成。其中,给定信号Ig来自输入级电路的输出,Drive_H,Drive_L与主回路中功率晶体管基极相连。闭环调节电路、功率晶体管、负载电流采样电阻三者构成射极跟随器,实现电流采样电阻端电压强制跟随于闭环调节电路的输出值,从而达到负载电流高速可控调节的目的。

图2 闭环调节电路

闭环电路主体为1∶1反相比例运算电路,由TL082通过R5,R20构成,电路的输出端采用Q1,Q2组成的推挽电路放大运放输出能力,当输入信号Ig的幅值为±1 V,通过Q1,Q2后输出为等值反向电压±1 V。将R5,R20设为500 Ω,选择较低的阻值,一方面可减小其与电容C2的时间常数,提高电路的响应速度,另一方面提高电阻上的功耗,减小噪声对有效信号产生的干扰。R10,R11,D3,D4构成补偿电路,补偿Q1与Q2的BE间压降,二极管选用1N4148,R10,R11阻值为500 Ω,则电阻上流过的电流约8 mA,满足对Q1与Q2的驱动要求。同理,采用D1,D2的二极管导通压降补偿主电路中TIP41C,TIP42C的BE间导通压降。通过微调R7与R8的阻值,实现主电路晶体管TIP41C,TIP42C处于临界导通状态。R6,R9阻值为100 Ω,在±5 V供电电源的左右下,其上流过约43 mA电流值,满足主回路中功率晶体管的驱动要求。

驱动信号Drive_H,Drive_L信号分别通过功率晶体管TIP41C与TIP42C的BE施加至电流采样电阻R12上,形成射极跟随器,如图2所示,实现采样电阻电压始终反向跟随运放输入电压Ig。通过调节电流采样电阻端电压,实现串联在回路中的线圈电流的实时调节。同时,将闭环电路的输入输出信号幅值均控制在±1V以内,有助于TL082响应更快的频率。

1.3 高速驱动器主回路设计

主回路供电电压为±50 V,需求的最大负载电流为±2 A。由于主回路需满足高频状态下实现任意电流波形的输出,而所驱动的目标负载为对电流具有阻碍作用的电感线圈,因此主回路功率晶体管必须工作在放大状态。为了实现电感电流能够有效跟随输入信号,设计主回路射极跟随电路,通过强制主回路电流采样电阻端电压实时跟随电流给定信号,实现电感电流按要求进行高速变化。通过这种方式代替常规的PI调节,输出电流将不易产生超调、波形振荡现象。考虑到双极性晶体管在射极跟随器的设计上更灵活,文中采用TIP41C,TIP42C作为电路的功率调节器件。设计的电路如图3所示。

图3 主回路电路

由于电路负载为扫描线圈,等效为电感器,当驱动器输入信号带突变特性(如方波)时,在正向信号突变沿,功率晶体管Q3~Q5将快速开通,50 V供电电源快速对负载充电;当负载电流达到目标值时,功率晶体管Q3~Q5内阻增大,电路电流继而维持稳定。实际上,Q3~Q5存在调节时间,此刻负载在正向电压的作用下,电流仍将继续增大,导致负载电流超调,随后发生波形振荡。为减小这部分失真,在主回路中加入电阻R15与R16,与电感负载形成RL电路,在响应阶跃信号时,负载电流的增长受到回路中电阻R15,R16的制约产生了一定的上升时间,通过调整阻值大小,使上升时间匹配Q3~Q5的调节时间,从而达到负载电流的稳定。另一方面,R15,R16的引入可用于分担一部分功率晶体管上的电压,从而减小功率晶体管工作过程中的损耗。受输出电流最大2 A的制约,R15,R16的阻值不能超过25 Ω,阻值过大将增加电感电流上升时间,过小则无法产生良好的调节效果。经综合考虑,此处阻值选为5 Ω,可计算得主回路电流从0 A增长至2A的时间增加47 ns,对系统的响应速度影响较小,同时也够匹配功率晶体管的调节时间。

负载电压变化是通过功率晶体管的调节实现,进而达到改变负载电流变化率的目的。在高速变化过程中,功率晶体管BE间结电容容易与感性负载形成LC振荡,影响输出波形。因此,加入电阻R13,R14,R18,R19,其中R13,R14串联在驱动电路中限制振荡电流幅值,其阻值不宜过大,否则将影响闭环控制的效果,此处选择阻值为10 Ω。R18,R19用于衰减振荡能量,同时可防止功率晶体管间因干扰信号产生的误导通,选值为1 K。R17为负载提供可靠的放电回路。各参数的取值将在仿真软件中进一步验证。

2 高速驱动器电路仿真

电路仿真是验证电路功能、优化电路参数、提高电路工作可靠性的有效工具。由于电路中部分器件的非线性特性,在高频动态下其寄生参数的作用效果明显,导致采用常规方式计算电路参数将存在一定偏差。文中通过Cadence仿真软件对驱动器电路进行仿真分析,验证电路功能并优化参数,进而指导实际驱动器的设计工作。

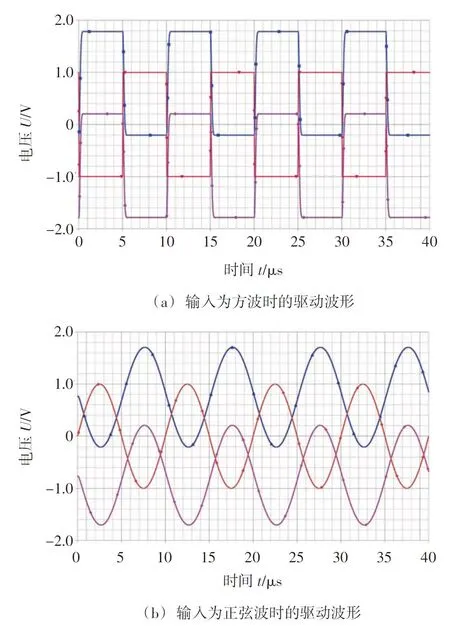

2.1 高速闭环电路仿真

采用Cadence SPB 16.6对闭环电路进行仿真分析,验证上述参数下电路的工作特性,并优化各项电路参数[4]。在Design Entry CIS环境下编辑测试电路,通过Pspice A/D模块对电路进行仿真计算,设定仿真时长为40 μs,每步计算时间为0.01 μs。电压测试点分为位于Ig,Drive_H及Drive_L处,Ig信号由软件自带的电压源提供。测试波形为方波时,波形参数设为幅值±1 V,周期为10 μs,脉宽为4.95 μs,上升沿下降沿均为0.05 μs;测试波形为正弦波时,波形参数设为幅值±1 V,频率100 kHz,相位角0°,两种输入波形状态下,电路的仿真波形如图4所示。图4中红色波形为Ig处电压信号,蓝色波形为Drive_H处电压信号,粉色波形为Drive_L处电压信号。根据仿真结果分析可知,在输入波形为上述参数的方波信号时,Drive_H及Drive_L两处波形与输入波形之间成反相比例关系,跟随性较好,其上升沿与下降沿约200 ns,波形失真度很小,无超调量;相较于输入信号,Drive_H的波形是在原波形基础上直流偏置约0.8 V,Drive_L波形直流偏置电压约-0.8 V。当输入波形为上述正弦波信号时,Drive_H及Drive_L两处波形与输入波形之间成反相比例关系,输出波形失真度很小,可以很好的反映输入波形的状态变化。仿真结果表明,所设计的闭环电路能有效响应100 kHz的高速信号。

图4 驱动电路仿真波形动波

2.2 高速驱动器仿真

对驱动器整体电路进行仿真,在Design Entry CIS环境下编辑输入级电路、闭环电路及主回路电路,通过Pspice A/D模块对其进行仿真,设定仿真时长为40 μs,每步计算时间为0.01 μs。驱动器输入波形为方波,其参数为幅值±10 V,脉宽4.95 μs,上升沿与下降沿0.05μs,周期10 μs,频率100 kHz。测量输入波形,采样电阻端电压,电感电流波形如图5所示。图5中红色波形为输入信号,蓝色波形为电流采样电阻端电压,绿色波形为电感电流。可以看到,在输入为±10 V方波信号时,采样电阻电压与电流波形的一致性较好。按幅值10%~90%的时间计算上升沿与下降沿,两者波形的上升沿与下降沿约为1.8 μs,采样电阻稳定时的端电压为±1 V,对应电感电流为±2 A。根据仿真结果可知,所设计的驱动器能够在100 kHz下有效输出,且波形失真度小。

图5 驱动器仿真波形

3 高速驱动器研制与性能验证

采用上述电路结构与参数研制出了电子束扫描线圈高速驱动器,并分别对输入级电路、高速闭环电路以及驱动器主回路进行性能测试与对比验证。

3.1 输入级电路波形测试与分析

输入级电路如图1所示,采用函数发生器AFG3022在图1中Vin与0 V处施加100 kHz,幅值为±10 V,50%占空比的方波信号,并通过示波器TPS2024测试输出端波形如图6所示。图6a与图6b中同一通道对应的测试点为同一点,其中通道1为函数发生器输出波形,通道2为图1所示电路运放7脚的输出波形,通道3为直接采用10∶1反向比例运算电路时运放7脚的输出波形,即将图1中R1短路,R2,C1断路,R4改为1K时,运放的输出波形,通道4为反向1∶1运算电路运放7脚的输出波形,亦即将图1中R1短路,R2,C1断路时,运放的输出波形。对比四个通道的波形可以看出,通道4因为运放直接采用1∶1反向比例运算电路对输入信号进行处理,因此其输出电压从-10 V上升至10 V所需的时间达到了1.14 μs,且出现一定量的超调;而通道2和3的电压上升时间很短,特别是通道3的上升时间仅116.9 ns,但产生的尖峰电压比较大。其原因分析为:通道1高电平时,电流由Vin通过R3,R4流向运放7脚;当通道1由高电平跳变为低电平时,运放输出电压不能立即发生改变,但电流却变成由运放7脚经R4,R3流向Vin,R4端电压反向,叠加在7脚上,导致7脚出现电压尖峰。采用图1所示电路将Vin先进行分压后再1∶1反向比例运算,可大幅减小这部分电压叠加量,同时由于补偿电容C1的引入,改善了电路的充放电特性,有效减小的运放输出波形的尖峰值,但输出波形的上升与下降时间将适当变长,如图6中通道2波形所示,为258.7 ns,但仍在接受范围内。

图6 输入级电路测试波形图

因此,采用分压、补偿及反向比例运算的方式有效的提高了通用型运放对高速信号的处理速度,使得输入级电路能快速响应高频输入信号。

3.2 高速闭环电路波形测试与对比分析

对图2所示电路进行测试,测试工具包括泰克函数发生器AFG3022一台,泰克TPS2024示波器一台,P2220示波器探头三根。函数发生器产生波形信号输入至Ig处,波形参数为与仿真参数一致的方波与正弦波,分别通过示波器测量Ig,Drive_H及Drive_L处电压波形并进行分析。所测波形如图7所示。图7中通道1为Ig波形,通道2为Drive_H波形,通道3为Drive_L波形。由图可知,测试波形与仿真结果较为接近,输入波形为方波时,驱动波形的上升时间为280 ns,两者的跟随性较好;输入波形为正弦波时,输入波形与Drive_H及Drive_L输出波形的直流偏置电压分别为0.6 V与-0.6 V,波形跟随性良好。可见,闭环电路能够满足100 kHz的工作要求。

图7 驱动电路测试波形

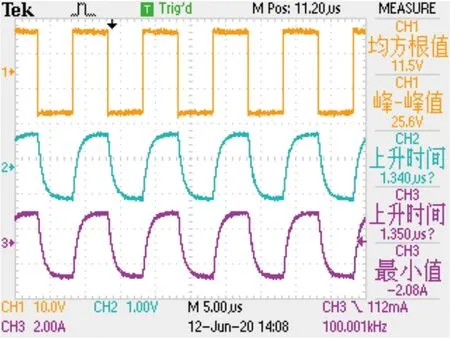

3.3 高速驱动器特性测试与验证

将驱动器输出端接至电感量为10 μH的扫描线圈两端,电路的输入端接收±10 V的100 kHz方波信号,通过示波器测量输入波形,电流采样电阻端电压以及电感电流波形,所得结果如图8所示。图8中通道1为

图8 驱动器实际输出波形

输入信号,通道2为采样电阻端电压,通道3为负载电流波形。可以看到,在输入信号为±10 V的方波信号时,采样电阻电压波形与电感电流波形一致性较好,电流采样电阻端电压正向幅值为1.03 V,负向幅值为-1.06 V,上升时间为1.34 μs,较仿真波形的上升时间短;负载电流正向幅值为2.02 A,达到设计值2 A的101%,负向幅值为-2.08 A,达到设计值的104%,电流上升时间为1.35 μs。

受负载供电电源电压与负载电感量的制约,50 V供电电压下10 μH电感的电流在±2 A间进行跃变的极限时间为800 ns。更好的电流波形意味着更高的线圈供电电压;而供电电压的上升,使主回路电流上升沿变得更陡的同时,也使得电路自身的电磁干扰变得很大,且功率器件的损耗也呈指数级增长,这将对电路的设计及优化提出新的挑战。

而在实际的电子束设备中,控制电子束扫描使其在两点或者多点间跳跃时,在1.35 μs跳跃时间内,电子束能量释放在跳跃路径上的平均线能量相对于3.65 μs定点停留时间下产生的能量而言,其实所占比重并不大。因此,上述负载电流波形可以满足电子束在100 kHz下进行高速扫描。

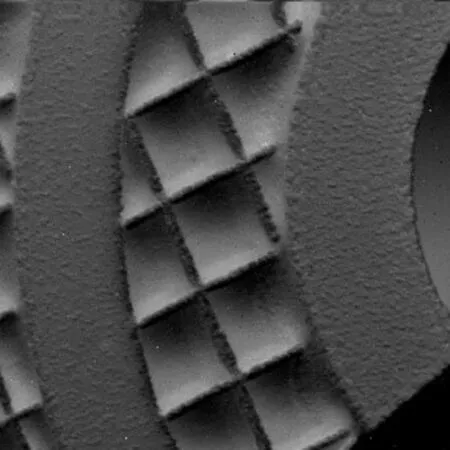

分别在背散射电子成像系统及电子束高速图像扫描系统中验证高速驱动器的实际扫描效果,获得图9所示的扫描图像。图9为背散射电子成像系统对零件实时观测的效果图,图10为控制电子束在金属板件扫进行高速图像扫描的效果图,可见两者图案纹理清晰,电子束扫描效果较好。

上述测试结果表明,所研制的电子束扫描线圈高速驱动器可快速精确的控制电子束进行高速偏转扫描,满足设计要求。

图9 背散射电子成像

图10 电子束高速图像扫描

4 结论

(1)采用分压、补偿及反向比例运算的方式设计高速响应差分输入电路,实现通用运放能快速有效的响应高速电压信号。

(2)通过射极跟随的方式设计驱动器电流闭环电路,强制主回路电流高速跟随输入信号。

(3)通过Cadence仿真软件进行驱动器电路功能验证与参数优化,实现驱动器电路与负载特性匹配。

(4)根据电路设计与仿真结果,研制了电子束扫描线圈高速驱动器,并对其进行测试分析。结果表明,该驱动器驱动电感值为10 μH的扫描线圈时,输出电流波形能在100 kHz高频下可靠跟随输入信号,正向最大电流2.02 A,负向电流最大-2.08 A,满足设计要求。