一种基于比较器共模模式的真随机数发生器设计方案

李 桢,汪鹏君,程 旭,李 刚,张会红

(1.宁波大学 电路与系统研究所,宁波 315211;2.复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

物联网的快速发展使得对信息安全的要求越来越高,而高熵值随机数发生器作为信息安全的重要组成部分受到越来越多的关注.随机数发生器可分为伪随机数发生器(Pseudo Random Number Generator, PRNG)和真随机数发生器(True Random Number Generator, TRNG)两大类.PRNG靠特定算法产生的输出序列尽管统计特性优良,但具有确定性和可预测性等缺点,不适用于信息安全.TRNG则通常选取热噪声、核衰变、宇宙辐射等随机物理现象作为熵源[1],生成的随机序列具有均匀性、独立性和不可预测性3大特点,适用于数据加密.熵源中热噪声的应用最为广泛.热噪声由导体中载流子的热振动引起,它会造成沟道电流微小波动从而在导体两端产生随机波动电压[2].基于热噪声的TRNG电路设计方法主要包括: 环振抖动采样、亚稳态和热噪声直接放大3种方法.环振抖动采样中,由于振荡器电路的热噪声会引起时钟抖动,因此用低频时钟采样高频时钟获得随机序列.该方法虽然电路结构简单,但随机性较差[3].亚稳态则是让双稳态电路工作在亚稳态状态,使得电路输出完全受热噪声影响.该方法有着较高的数据吞吐率[4],但需要占用大量面积.热噪声直接放大法用运算放大器将电阻上的热噪声放大到合适的幅度,之后通过比较器将放大后的热噪声与中间电平比较得到随机信号.该方法可以提供高质量的噪声源[5],然而CMOS器件的热噪声幅值较小,易被电源纹波电压、衬底耦合噪声等周期噪声掩盖.且放大器的有限带宽、失调等非理想因素也会影响输出序列随机性.为此,文献[6]结合亚稳态和热噪声直接放大设计方法,提出将差分比较器共模连接从而抵御电源纹波和周期性噪声,同时令比较器钟控端接高电平使其维持在亚稳态.亚稳态下比较器的热噪声和输入偏置电路热噪声相叠加形成噪声源,利用运放和Slicer电路将热噪声电压转换化为逻辑0或逻辑1.该方案中偏置电路噪声幅度小易被其他环境噪声掩盖,且Slicer结构需要手动调节,占用I/O资源.

鉴此,本文用CMOS开关使热噪声反相器环形连接,使输出端电压收敛并保持在亚稳态电平从而为比较器提供直流偏置和输入噪声,用可配置灵敏放大器将热噪声转换为随机序列,通过反馈控制电路使TRNG具有自适应调节能力,增加其鲁棒性.

1 TRNG电路设计

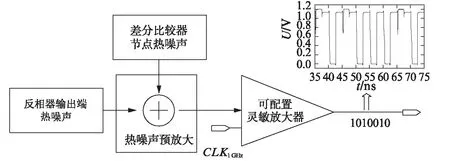

基于比较器共模模式的真随机数发生器的电路结构如图1所示.反相器输入输出端相连形成环路使得输出电压收敛于亚稳态电平从而为比较器输入端提供电压偏置,恒压源连接比较器时钟控制端,使其工作在亚稳态.亚稳态下反相器输出节点热噪声和共模模式下比较器的热噪声相叠加,经灵敏放大器转化为逻辑1或逻辑0再由D触发器采样生成随机输出序列.反馈单元根据输出序列偏向性对灵敏放大器进行调节以补偿环境变化和工艺偏差.

图1 真随机数发生器整体框图Fig.1 TRNG block diagram

1.1 热噪声发生器

热噪声由导体中载流子的热振动引起,它使沟道电流产生微小波动,从而在导体两端产生波动电压.电阻上的热噪声可用一个串联的电压源来模拟,其单边谱密度为

Sv(f)=4kTRf≥0,

(1)

式(1)中:k=1.38×10-23J/K是玻尔兹曼常数;T是热力学温度;R是电阻阻值.晶体管同样具有热噪声,可以用一个连接在漏源两端的电流源模拟,其频谱密度为

(2)

差分比较器结构如图3所示.P2、P3为电流源,为电路提供偏置.P4、P5为比较器输入对管,N2、N3、N4、N5为负载管,其中N2、N3交叉耦合形成正反馈,生成负电阻.N4、N5并联为正电阻,二者相连接其等效交流电阻为2/(gm2-gm1)[8],gm1是N2、N3的跨导值,gm2是N4、N5的跨导值,其中

(3)

式(3)中:un为电子迁移率;Cox为单位面积栅氧化物电容;W为有效高度宽度;L为有效沟道长度;ID为MOS管源漏电流.热噪声反相器、共模模式下比较器和恒压源上的热噪声相叠加后需转换为逻辑电平才能被后级电路采用,因此还需要灵敏放大器.

图2 热噪声反相器结构及电压传输曲线Fig.2 Thermal noise inverter structure and voltage transfer curve

图3 差分比较器结构Fig.3 Differential comparator structure

1.2 可配置灵敏放大器

灵敏放大器具有灵敏度高、运行速度快,结构简单等优点,是将热噪声转化为逻辑电平的理想器件.灵敏放大器结构如图4所示.工作过程可分为预充电阶段和求值阶段.当时钟信号CLK=0时,电路进入预充电阶段,晶体管P6和P9导通,NF1和NF2截止,互补输出端VOP和VON被预充电至高电平;当时钟信号CLK=1时,电路进入求值阶段,晶体管P6和P9截止,NF1和NF2导通,电路开始求值.若晶体管NF1的源漏电流I1大于NF2的源漏电流I2,VOP点电压将通过NF1被优先放电至低电平,交叉耦合结构快速将VON充电至高电平;反之则VOP为高电平,VON为低电平.当灵敏放大器工作电流完全平衡时,若忽略热噪声影响,互补输出VOP和VON在求值阶段最终会稳定在中间电平(VDD/2).实际电路中,在热噪声的影响下,I1、I2大小会随机波动,从而在求值阶段产生随机输出.

灵敏放大器工作电流平衡是获得理想随机序列的关键.但实际电路中,负载失配、工艺偏差等非理想因素都会影响电流大小,使输出序列产生明显的偏向性.为补偿偏差,晶体管NF1和NF2采用可配置NMOS阵列,其结构如图5所示.它由1个主NMOS管N0和10个可配置的从NMOS管N8~N12,NS0~ NS4组成,nconf[4,0]为配置端.

图4 可配置灵敏放大器Fig.4 Configurable sense amplifier

图5 可配置NMOS阵列Fig.5 Configurable NMOS array

以nconf0为例,nconf0高电平时,晶体管开关NS0导通,N8并联在N0两端,可配置NMOS阵列的等效宽长比升高;nconf0为低电平时,NS0截止,等效宽长比降低.被选通的配置端越多,阵列等效宽长比越宽,相应的工作电流越大,反之亦然,可有效补偿工艺偏差从而提高序列随机性.

热噪声反相器和共模模式下比较器的热噪声经叠加后,在时钟的控制下被灵敏放大器转化为逻辑0或逻辑1,其结构如图6所示.输出波形经D触发器采样生成原始随机序列.反馈单元根据原始序列偏向性调节灵敏放大器克服偏差.

图6 噪声叠加示意图Fig.6 Noise superposition diagram

1.3 反馈调节和后处理

为使灵敏放大器可根据原始序列的偏向性调整可配置NMOS阵列来补偿偏差,提出动态补偿算法.算法采用单级等距调节,相较文献[4]中的粗细2级调节,该算法复杂性低且易于实现.动态补偿算法伪代码如图7所示.该算法有动态配置和动态监控2种模式.TRNG在上电启动后首先进行初始化,初始化阶段可配置NMOS阵列的配置端cfop[4,0]和cfon[4,0]全部被置为高电平,标志位flag置为“2”.随后进入动态配置模式.动态配置模式下每4个时钟周期,状态机对TRNG输出的4位数据进行一次读取检测.若输出偏向“1”,令flag=“1”;若偏向“0”,令flag=“0”.根据flag的值按照状态转移图对cfop和cfon进行配置.当输出序列随机时,令flag=“2”,并进入动态监控模式.若检测到输出序列失去随机性,算法返回动态配置模式.否则,状态机维持在动态监控模式,cfop和cfon配置不变.

图7 反馈调节算法Fig.7 Feedback regulation algorithm

为了弥补输出分布的不均匀并消除自相关性,采用XOR纠偏法对原始序列进行后处理.设X和Y分别为2位随机数,其期望值E(X)=E(Y)=u,p是它们的相关性,则

(4)

当u接近1/2时,式(4)可表示为

(5)

由式(5)可知,若X和Y是相互独立的(即p=0),则E(X⊕Y)≈1/2.若有n位彼此独立的随机数进行异或,则其期望值为

(6)

其中m=u-1/2.从式(6)可以看出,随着n的增大,期望趋近于1/2.因此,将40位D触发器组成移位寄存器,选出彼此相邻10位的数据进行异或消除偏差.XOR后处理电路结构如图8所示.

图8 XOR后处理电路Fig.8 XOR post processing circuit

2 计算机模拟仿真结果

整体电路采用Cadence的Verilog/Spectre混合仿真器对模拟电路和Verilog模块进行联合仿真.在1.2V电压、27℃下,令时钟频率为1GHz进行蒙特卡罗仿真,输出序列如图9所示.由图9可知,局部连续输出1的最长时间为7ns(即7个周期),无明显偏向性.

图10以像素点的方式展示了9×104位随机输出序列(300×300),其中: 白色代表1,黑色代表0.由图10 可见,0/1分布整体均匀,无较大偏差.将所得序列输入到Matlab测试自相关特性(用自相关因子(ACF)表示),结果如图11所示.由图11可知,在95%的自信区间内4000位连续数据间的自相关性近似为0.

图9 TRNG输出序列Fig.9 TRNG output sequence

图10 随机输出阵列Fig.10 Random output array

图11 输出序列自相关性Fig.11 Output sequence autocorrelation

表1 NIST测试结果

图12 不同工艺角下的P_valueFig.12 P_value under different process corner

由美国国家标准与技术研究所(National Institute of Standards and Technology, NIST)开发的NIST随机数测试统计包用于判定可能存在于序列中的各种非随机性.将仿真获得的100000位随机序列分成10组,输入到NIST测试套件中进行检测.测试结果如表1所示.P_value大于0.01则通过随机测试.从测试结果可以看出,各项子测试的P_value都处在较高水平,随机性优异.

为了验证电路鲁棒性,TRNG在ff至ss 5个工艺角和-40~125℃的温度下进行仿真,输出序列送入NIST套件进行测试.其中,经频率测试和熵值测试所得的P_value曲线如图12所示.由图可见,频率特性在各工艺角下较为平稳,且保持在较高水平.熵值在ff工艺角下较低,但仍能通过测试.

表2是所设计TRNG与其他文献对比.本设计采用亚稳态和抖动作为熵源,1000Mb/s的吞吐率足以满足应用需要.由于动态功耗与门电路翻转频率呈正比,文献[4,6]的功耗折算到1GHz下分别约为2800μW和1600μW.相较文献[4],本文在反馈单元中引入动态监控模式,在配置完成后降低模块中门电路翻转频率从而节省动态功耗.文献[6]中为实现噪声信号到数字信号的转换采用高带宽运算放大器串联Slicer电路结构,其中高带宽运放的静态功耗约1mW.本设计则采用锁存型可配置灵敏放大器代替高带宽运算放大器,其功耗仅108μW,从而使能耗降低约73.3%.

表2 与同类TRNG的性能比较

3 结 语

本设计首先令热噪声反相器输入输出相连形成环路使输出电压收敛并保持在亚稳态电位.亚稳态下反相器为比较器输入端提供电压偏置,同时输出节点的热噪声与比较器的热噪声相叠加构成噪声源.其次,比较器输入端共模连接从而抑制电源纹波和周期性噪声的影响.最后,利用动态补偿算法根据原始随机序列偏向性对灵敏放大器反馈调节,提高TRNG鲁棒性.所提TRNG电路采用SMIC 55nm CMOS工艺设计,输出序列经NIST套件测试,具有较高的随机性,可应用于密钥生成和信号加密等领域.