基于UVM的FPGA通用接口测试平台设计

王 涛,黄坤超,李晨阳

(中国电子科技集团公司第十研究所,四川 成都 610036)

0 引 言

随着FPGA在航空、航天、通信、识别等领域的广泛使用,以及业内对FPGA验证质量要求的不断提高,传统的仿真验证已难以满足日益增长的验证需求,验证技术也由传统仿真验证逐渐转移到新一代的验证方法学中.

目前主流的验证方法学分别是VMM,OVM和UVM,其中UVM已成为业内广泛使用的验证技术[1],属于TLM级验证,具有较高层次,主流的EDA工具均支持UVM,已成为各大公司验证趋势.国内航天等科研单位都在积极开展FPGA自动化测试技术研究,对UVM验证方法表现出极大兴趣.UVM主要是针对相似的FPGA接口进行验证,据统计,现有的大部分UVM验证平台的实现与DUT呈现紧耦合性[2],导致验证组件不能直接在不同项目平台中使用,其可重用性需要通过重建或替换已有验证平台的部分代码来实现,使得多重测试环境复杂度增加,产生大量的工作量[3,4].

面对多接口的复杂设计环境,为满足多重验证环境需要,利用通用UVM验证平台架构进行重新优化设计,建立一种基于UVM的高层次化测试平台,提出层次化设计、通用数据库共享、事件同步化控制、自动化执行等技术,建立一套新的重用机制,使得重用性即能在相似接口内重用,又可以在多种不同接口的复杂环境中重用,提升测试的可重用性.实验结果表明改进后的平台可使测试时间缩短40%以上,并满足多种接口测试需要.

1 FPGA通用接口自动化测试平台

1.1 通用接口分析

目前FPGA设计较多的是采用DSP+FPGA设计构架,对历届测试项目统计FPGA对外接口主要包括UART,SPI和DSP等.一般情况下UART,SPI和DSP接口设计是通过总线架构形式配合使用,如图1所示.

图1 FPGA通用接口关系

根据UART,SPI和DSP 3种接口支持的不同类型协议,通过思维导图分解接口需求,主要包含DSP的只读、只写、可读可写测试,UART和SPI的收发功能一致性测试、缓冲测试、帧格式测试,校验位测试、帧长测试、毛刺测试、波特率测试等,可通过配置寄存器组合出不同的实现模式.

1.2 通用接口自动化测试平台

基于UVM测试平台,改进后的FPGA通用接口自动化测试平台如图2所示.

图2 通用接口自动化测试平台

FPGA软件通用接口自动化测试平台分为测试平台和管理平台两部分.管理平台为自动化测试平台的实施提供所对应的可视化操作窗口,提供接口参数配置和结果输出界面,通过脚本方式完成管理平台与测试平台之间的数据交互.

测试平台在UVM基础上改进形成,由一个TOP顶层封装起来,首先在TEST层控制发送sequence_high(高层次序列)给序列器sequencer;Sequencer将sequence_high以指针的形式传递给驱动器Driver;其次在BASE_TEST层中建立通用数据库和ENV层之间的各个组件连接关系,建立数据传输通道;Driver根据接收到的高层次序列命令sequence_high,从通用数据库sequence_low_lib中提取相应的底层次序列sequence和系统配置参数sequence_sys,将底层次序列送给被测件DUT;监控器Monitor收集DUT输出数据和覆盖率数据等,将收集好的数据传递给Collect_lib(数据收集库),Collect_lib负责数据统一管理和覆盖率收集;比较器Scoreboard从数据收集库Collect_lib提取要比较的数据,在Scoreboard比较完成后,打印输出结果.最终实现测试指令与测试设计相分离,测试设计与被测设计相分离的设计,完成整个测试过程.

2 关键性技术实现

2.1 层次化设计

对于任何一种新型的验证方法学来说,分层的测试平台是一个关键概念,分层有助于验证平台的可移植性和可维护性[5].研究表明,越是高层次化的验证则验证效率越高[6].传统的仿真采用平面式的验证环境,层次化程度很低,不利于重用,难以处理各种情境下的验证问题.

现有的UVM验证平台在TLM级组件之间的通信通过专门PORT端口传递消息[7],在TEST顶层直接实现和控制测试序列产生,同时还要考虑多序列之间的同步问题,抽象层次级别低,同时验证组件之间呈现紧耦合关系,导致其可重用性较差.当多重环境存在时,验证的复杂度和出错概率都急剧增加[8,9].因此,为提高代码的可重用性,需要在一个UVM验证平台下,即要保留TLM级处理能力,又要同时满足多重环境需要.为此,在UVM基础上设计出一种新的高层次化结构,如图3所示.

改进后的UVM和通用UVM的层次关系不同之处在于:一方面,将原有的测试序列sequence按层次分成4类,分别为高层次序列、底层次序列库、数据收集库和系统配置4个部分,由于原来的序列使用过于直接,级别低,划分不明确,每次测试都需要用户重新开始设计,因此,通过分解,序列不仅提高了重用性,而且提升序列的抽象级别,同时解决了多序列带来的同步化问题,消除了采用vrtual sequencer和virtual sequencer进行同步的复杂序列设计;另一方面,在ENV层中统一Driver,Monitor,Scoreboard和Ref_model4个组件,其中只保留sequencer和Drive组件之间采用PORT端口传递信息,继承UVM特性,其余组件之间信息传递使用通用数据库共享方式替代PORT端口传递消息,取消agent代理层设计,这样做可以大大地简化测试环境之间的耦合关系,不仅提高了可重用性,而且在处理不同信息时得到了扩展,处理方式更加简洁和透明.使用一个平台,即可完成对不同的多接口测试环境需要.

2.2 通用数据库共享

通用数据库是在建立测试用例过程中引入的一种专家知识库概念[10],是一个中央存储数据库,由一组产生各种激励序列的sequence类组成,可以与UVM验证环境中的任何组件进行信息交互,整合了仿真所需要的多个独立的数据库,数据库的创建从需求中提取高价值的信息,结合随机约束特性,进行高效利用.高层次序列、底层次序列库、数据收集库、系统配置4个部分与组件之间的共享方式如图4所示.

图4 数据库与组件之间的共享方式

sequence_high按照需求规格提炼出验证特性,将验证特性进行归类处理后,对应测试用例的功能测试点表示,sequence_low_lib就是每个功能测试点具体输入数据序列的集合.高层次序列抽象级别较高,为决策者,低层次序列是直接测试序列,抽象级别较低,为执行者,两者将决策与具体执行联合在一起.collect_lib主要是收集DUT输出的各种实测数据,同时也收集参考模型或底层序列库传递来的期望数据以及覆盖收集等,在收集数据完成后,产生不同的同步标志信息,供比较器Scoreboard使用.由于DUT是一种时序电路,驱动接口时会有时序参数要求,因此,必须要有sequence_sys系统配置,sequence_sys主要包括建立控制接口信号正确时序关系的各种时序参数,如时钟频率、建立时间、保持时间、发包间隔等.

图5~图8 分别是高层次序列、底层次序列库、数据收集库、系统配置设计示例,每类序列设计允许创建、修改、新增、删除等操作.实现机制采用class形式将序列封装起来形成一组参数化,提高继承者的配置功能和通用功能.通过利用UVM的Field_Automation宏机制注册,使用`uvm_field_*系列宏体注册不同数据类型的变量,宏的使用实际上相当于是一种对数据变量的控制开关,使用if/case判决条件语句判决高层次序列激活时启用不同的数据变量.利用该机制用户能够很方便地产生所需要的各种序列.

图5 高层次序列设计

图8 数据收集设计

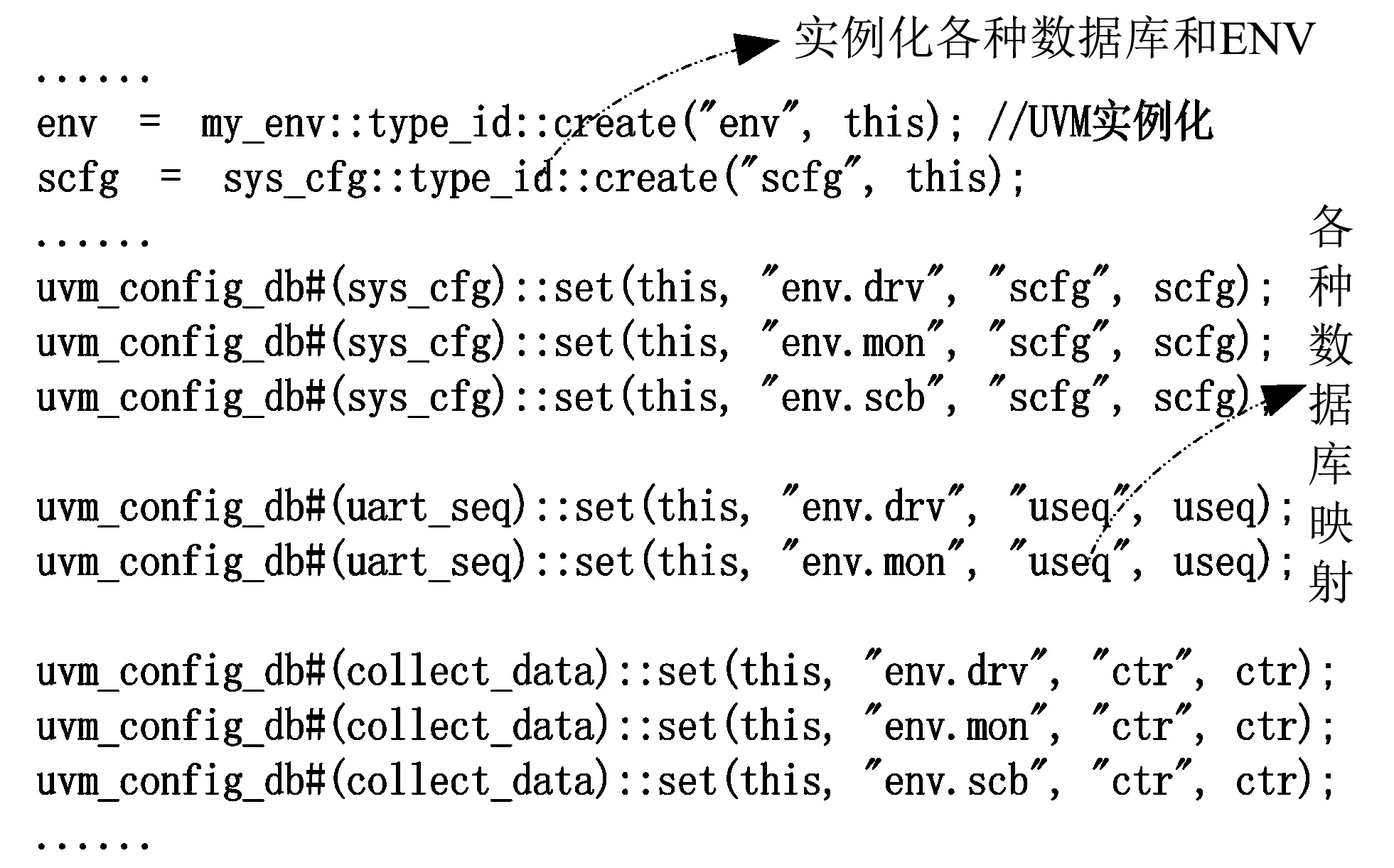

通用数据库是作为uvm_object的class类产生所有相关的数据分类设计,数据库可以在任何的component or object中共享.共享方式在BASE_TEST层完成配置,主要作用是建立数据库和ENV层的各个组件之间连接关系,建立数据传输通道,其基本结构如图9所示.使用uvm_config_db::set(源文件使用)函数将需要共享的数据库传递给指定的模块;组件调用时,使用uvm_config_db::get(目的文件使用)函数将该指定的模块导出共享的数据库.

图9 数据库在不同组件之间的映射

利用数据库充分挖掘UVM验证环境中数据的有用信息,提高数据分析的有效性,支撑决策制定,联合不同的DSP,UART,SPI等接口最优数据格式需求,构建一种可共享和跨项目的通用数据库,有效提高跨组件的通信和互操作能力,实现资源合理配置,满足多个平台重用.

2.3 事件同步化控制设计

测试平台组件Driver,Monitor,Scoreboard 3者之间必须有密切的时序配合才能正常工作,基于时钟周期级的测试平台对于具体时钟的紧耦合性很强,需要处理执行过程中初始化、驱动、监控和比较等组件,组件之间的信息交互难以处理同步化关系,同时还存在一定的时序竞争问题.事件触发对于具体时钟的紧耦合性不强,采用事件触发解决组件之间信息传递同步化处理是一种很好的解决办法,如图10所示.

图10 基于事件的同步化控制

2.4 自动化执行

测试平台的自动化执行,是提升测试效率的有效手段,平台可以同时提供两种自动化执行方法,包括人机交互界面自动调试和命令行的脚本化输入方式.

利用脚本执行测试平台,测试结果自动呈现.脚本的开发关键是要处理好测试平台工作目录配置以及脚本处理对象,即方便脚本设计又可以便利平台重用,利用脚本将平台工作目录下的各个组件衔接形成一个整体进行无缝工作.测试平台的脚本目录及工作流程如图11 和图12所示.

图11 测试平台脚本目录

图12 测试平台工作流程

同时利用Qt工具开发出人机交互界面,用户选择不同接口的预设测试用例即可执行测试,通过调用仿真工具执行并打印测试结果,管理界面如图13所示.

图13 人机交互式的管理界面

3 测试结果分析

利用改进后的自动化测试平台,对一个包含多个接口项目进行测试,软件主要实现功能包括接收DSP接口写入的数据并缓存到FIFO中,再将数据读出通过UART接口发送出去;同时将UART接口接收到的数据缓存到另一个FIFO中,再由DSP将数据读出.通过仿真工具Questa Sim 10.5运行脚本文件run.fdo,仿真完毕后打印测试结果和覆盖率信息,图14 和图15 是测试完成后的部分输出结果.

图14 打印结果

图15 覆盖率报告

经测试,UART接口的波特率余量约为:(39.46~38.46 kHz)/38.46 kHz=2.6%,与通常要求的20%余量相比,其UART模块抗干扰性较差.另外此次测试还检查出奇校验、偶校验报错,无校验正确,与源代码的无校验设计特性相符合,DSP读写功能正常.统计测试过程中的消耗时间,包括脚本编辑、参数配置、接口配置、用例编译链接、结果记录、测试执行、环境搭建等占用时间统计,总消耗时间为13.7 h.同时将该项目在传统测试和UVM验证平台上试运行,统计测试时间分别为36 h和23 h,经对比,该平台有效降低测试时间40%以上,测试效率得到有效提升.

4 结束语

FPGA通用接口自动化测试平台主要面向FPGA软件测试,解决FPGA软件通用接口在测试过程中自动化测试环境缺乏、支撑功能不足等问题.通过利用层次化设计、通用数据库共享、事件同步化控制、脚本执行等技术,改进UVM验证架构,提高测试平台的可重用性和自动化水平.通用数据库还需进一步通过实践检验,形成一种广泛认可方式,将更丰富的方法应用于测试平台,提高软件研制进度和质量.