一种集成化的卫星PCM测控与时间同步性能测试系统设计

杨同智 周汝志 盛开明

(上海卫星工程研究所,上海201109)

1 引言

遥控、遥测与时间同步是卫星平台电子系统的基本功能,是实现卫星功能控制、程控作业与自主管理等高级特性的基础,其性能优劣直接影响卫星效能。以往平台电子系统测试采用单机自检设备和软件,其测试完备性与系统性有所欠缺,很多问题在系统级测试时未能发现,增加了卫星后期更改的开销,因此有必要将卫星综合测试提前引入至系统级测试,提高系统级测试的充分性。此外,卫星系统间高精度协作任务(如运动补偿等)对卫星时间同步性能要求越来越高,需在系统级测试中充分验证星上时间同步设计性能。最后,平台电子系统级测试需进行多次外场对接联调,其测试设备应具备集成化、便携性的特点。

综上需求,本文设计了一套集成化的PCM多功能测试系统,由PCM多功能卡、GPS时间服务器、PCM测控软件和时间同步性能测试软件组成,实现了PCM有线测控与时间同步测试两部分功能。PCM多功能卡可以适配不同码率与格式的卫星PCM测控接口,与综合测试软件无缝集成,实现测控信息处理,充分利用了综合测试软件优良的人机交互界面、多样式遥测数据呈现能力和便捷的遥控指令编辑生成特性,提升了测试的效率与充分性;同时PCM多功能卡可以锁存卫星触发信号对应的地面时间,通过时间同步性能测试软件分析多功能卡锁存的时间和卫星下传数据中的时标信息,实现卫星时间同步性能测试。

2 PCM有线测控

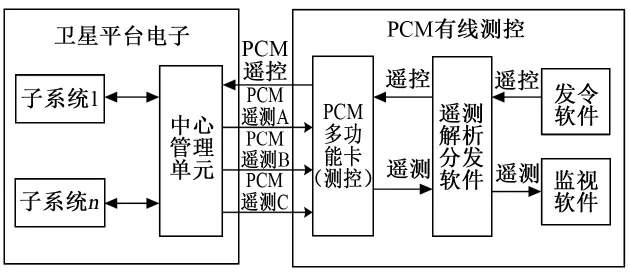

如图1所示,PCM多功能卡收发PCM测控信号,具备与Cortex测控基带[1]一致的网络控制接口,与后端的综合测试软件协同完成遥控发送与遥测监视。

图1 PCM测控测试原理图Fig.1 PCM TM&TC test schematic diagram

2.1 硬件设计

如图2所示为PCM多功能卡的PCM测控逻辑设计总体结构图。设备接收得到的遥测数据及发送到星上单机的遥控指令均通过串口与上位机进行通信,3路遥测数据、应答信号、存储器读写、遥控自闭环等数据流均需要使用串口与上位机进行数据交互。为了避免多个通道同时使用串口,设备在FPGA逻辑设计时引入优先级控制功能。各通道使用串口的优先级从高到低依次为:遥测通道1、遥测通道2、遥测通道3、应答信号、存储器读、遥控自闭环。当通道需要向上位机传输数据时,先向控制单元发送请求命令,控制单元比对当前所有请求通道的优先级,选择传输优先级最高通道的数据。在数据传输过程当中,更高优先级的通道不能切断当前数据传输,必须等当前数据传输结束之后才能开始新一轮的通道优先级比对及数据传输。

图2 PCM测控逻辑设计总体结构图Fig.2 FPGA logic design diagram of PCM TM&TC

为了确保接收遥测数据的完整性和连续性,避免遥测处理单元在传输遥测数据时发生数据丢失,遥测处理单元的数据缓存区采用两个FIFO交叉工作的乒乓缓存,当FIFO1存储了完整的一帧遥测数据之后,控制单元自动将数据缓存切换到FIFO2,并且向控制单元请求传输FIFO1中的数据[2]。

2.2 软件设计

软件总体结构如图3,采用分层模块化设计[3],完成遥测、遥控与配置管理。

图3 PCM测控软件总体结构图Fig.3 PCM TM&TC software overall structure

测控软件应用功能强大的综合测试软件,工作界面如图4所示,其中遥测解析分发软件主要功能为指令转发、解析遥测数据、对帧连续性进行监控报警、将解析的遥测数据分发至监视软件、遥测遥控存盘及回放;监视软件以文本、曲线、图像化等多种方式成像遥测数据,具备遥测数据原码显示、保存回放、波道跟踪、超差报警等多种功能;发令软件具备丰富的指令列表集合和灵活的注数界面,可以根据测试需求修改参数发送临时注数包。

图4 遥测解析分发软件、监视软件与发令软件Fig.4 Telemetry processing,Monitor software and command software interface

3 时间同步测试

如图5,PCM多功能卡接收GPS时间服务器的IRIG-B码[4],使地面时间精度、稳定度与 GPS时间一致;PCM多功能卡接收卫星时标触发信号输入,锁存对应的地面时间;通过时间同步性能测试软件分析多功能卡锁存的时间信息与卫星下传数据流中的时标信息,完成星地时间、星上各系统时间的同步性能测试。

3.1 硬件设计

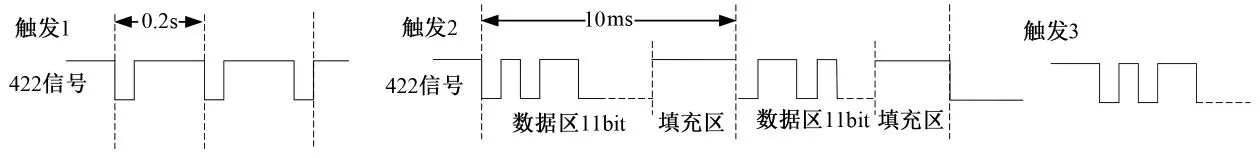

PCM多功能卡以IRIG-B码为外参考时间基准,接收RS422电平的星上时标触发信号,锁存对应的地面时间。如图6所示,卫星时标触发信号类型主要分为三类:触发1为脉冲型触发,触发2为周期性间歇数据流触发,触发3为连续数据流触发。对触发1采用边沿触发锁存时间,对触发2采用边沿触发,使用软件获取所需比特为位置的触发时间,对触发3采用数据触发,可设置1~4字节触发同步头,在检测到同步触发头后,输出触发脉冲信号,锁存对应地面时。对于三种类型触发输入,在检测到配置的触发特征后,发送时间锁存脉冲至时间寄存器锁存单元,锁存相应通道时间。

图5 卫星时间同步性能测试信息流示意图Fig.5 Information flow of satellite time sync performance test

图6 触发信号输入类型Fig.6 Trigger signal types

板卡逻辑设计总体图如图7,接收IRIG-B(DC)码参考输入,对B码进行译码获得GPS时间,刷新板卡时间寄存器,使板卡时间与GPS时间对齐。由于B码为整秒刷新[5],因此通过温补晶振的高稳时钟维持秒内时间更新。为避免触发通道的毛刺输入造成误触发,缓存多拍输入电平值,当电平发生翻转且翻转后电平持续3拍以上,才判定为跳变沿,消除毛刺触发[6]。对消除毛刺的输入进行触发特性(边沿或者触发数据头)检测,在检测到配置的触发特征后,发送触发脉冲至时间锁存单元,锁存相应通道时间寄存器时间。为避免多路同步触发竞争一个时间寄存器,设计了独立时间寄存器,用于锁存对应通道的时间信息,在锁存的时间信息前封装通道号,经格式编排后由网口发送至上位机软件。

图7 触发时间锁存逻辑设计总体结构图Fig.7 FPGA logic design diagram of trigger time latch

3.2 软件设计

时间同步性能测试软件主要完成星地时差监控与卫星时间同步性能测试。如图8,软件接收遥测、载荷、姿控等数据中的卫星时标信息,与PCM多功能卡锁存的对应地面时比对分析,实现星地、卫星各系统的时间同步性能测试。

图8 卫星时间同步性能测试原理图Fig.8 Schematic diagram of satellite time sync performance test

时间同步测试的具体流程如下:

(1)地面时的精度控制:地面时以GPS时间服务器IRGB-B码为参考,授时精度为1μs,保证地面时的准确性;

(2)卫星基准时与地面时对齐:通过星地时差测量,实时控制星地时差在规定范围内,保证卫星基准时向地面时对齐,保证卫星基准时准确;

(3)卫星各个系统时与其触发信号锁存的地面时比对:接收解析卫星下传的遥测、遥感等数据流,从中提取载荷、姿控等各个系统时;PCM多功能卡锁存卫星分系统时标触发信号对应的地面时;比对卫星系统时与对应地面时的时差,若时差超限,则星上时间同步设计需改进;

(4)同步时差分析:通过曲线拟合等方法进行获得时差漂移率等信息[7],用于优化时间同步设计。

卫星时与地面时的同步性能监控软件界面如图9所示。

图9 星地时间同步性能监控界面Fig.9 Monitor interface of time sync between satellite clock and ground clock

以地面时间为横坐标,以计算的星地时差为纵坐标,统计综合测试中5个小时的测试数据,把数据点描绘成测量曲线。

图10 星地时差漂移监测Fig.10 Monitor curve of time difference between satellite clock and ground clock

从图10可以看出,星地时差随时间基本上是线性变化的,可以使用公式y=kx+b进行线性拟合[8],如下

根据最小二乘法,拟合的系数k、b应使各数据点与拟合直线之间的残差平方和最小,k、b计算公式如式(2)所示,计算得到时差漂移率k=9.6ms/d。

同理对卫星各系统时间之间的关系进行线性拟合分析,获得各个系统时间之间的时差漂移率等关系,如此可采用均匀校时等补偿方法,降低时差漂移率,提升时间同步性能。

4 结束语

本文设计了一种集成化的PCM多功能测试系统,基于触发时间锁存的原理,实现了卫星时间同步性能的高精度测试,且可满足了不同码速率与格式PCM测控接口需求,使用综合测试软件进行卫星单机级、系统级测试,增强了卫星平台电子测试的充分性,在卫星研制中起到了一定作用,具有一定工程指导价值。