高频高速PCB多模块子板埋置工艺研究

纪成光 吴泓宇 肖 璐

(生益电子股份有限公司,广东 东莞 523127)

0 前言

同一系统中一般存在多种等级的电信号,包含普通信号、高频信号、高速信号等。局部混压高频高速PCB技术不仅能在满足高频高速信号传输低损耗的情况下大幅降低材料成本、加工难度,还能在一定程度上提高PCB可靠性,并且组合多变的混压结构,成为了同系统中不同等级信号分级传输的完美解决方案[1]。但传统局部混压工艺由于其制造工艺的限制,暂未实现内层不同等级模块间的互连,且对线路布局有限制。目前该工艺的实现可查阅的文献有交界处压合导电胶的专利,但该方法实现难度大,在交界处布置十分密集的线路易产生短路[2]。本文主要研究使用通埋子板的方式实现局部混压且模块间内层互连,以及探究双面对称嵌子板、内埋子板结构的可行性、平整度、可靠性交界处线宽制作能力等。为实现更复杂的多模块局部混压结构以及任意层、任意模块间互联导通结构提供工艺基础[3]。

1 实验部分

1.1 方案简述

多模块混压内层导通实现主要流程如图1所示:(1)两张以上芯板、一张以上的粘结片开槽,埋入其他模块子板;(2)排板压合后陶瓷磨板磨去交界处溢出的多余树脂;(3)化学沉铜后板面电镀加厚铜;(4)将作为内层的一面蚀刻出图形后压合至内层。

图1 内层模块间导通实现方法

1.2 试板与流程设计

实验试板为10层普通FR4材料与高频高速基材混压板,FR-4材料选用高Tg普通环氧树脂玻璃体系材料,Tg大于280 ℃,简称材料A;高频高速材料选用碳氢化合物/陶瓷体系材料,介电常数3.66,2.5 GHz损耗因子0.0031,简称材料B。叠层设计、内层导通处如图2所示。L1-4、L7-10为对称的嵌入B子板的内层导通结构,L5-6为B子板内埋结构(如图2)。

图2 10层实验板叠层结构

制作全流程如下:(1)AB材料所有层芯板流程图形制作→A芯板铣槽、B芯板铣成小块子板;(2)L2-3、L8-9 A材料粘结片铣槽→L1/4、L7/10压合(埋入B1子板)→磨板→沉铜电镀→内层图形制作;(3)L1-10压合(L5-6内埋B2子板)→沉铜电镀→外层图形制作→成品。关键流程的实验参数列于(见表1)。

2 分析与讨论

2.1 子板层间对准度

在埋入子板区域与板边四角分别设计层间对准度测试附连板,制作至成品后分别测试不同批次下的双面嵌子板、内埋子板、板边区域的层偏最大值,实验数据整理如图3所示。TCFA意为图形拉伸系数首板试验,即制作芯板压合首板收集实际图形拉伸系数最终确定更匹配该PCB图形拉伸系数(如图3)。

双面嵌子板整体对准度在TCFA前后提升19.05 μm,提升幅度23%。但对内埋子板对准度能力无明显提升效果。双面嵌子板0.075 mm、0.10 mm、0.125 mm、0.15 mm开槽单边补偿的子板整体对准度均值分别为0.075 mm、0.158 mm、0.062 mm、0.064 mm,极差0.017 mm,对准度与补偿大小并无明显线性规律。而内埋子板对准度与芯板开槽补偿有明显线性规律,对准度能力约等于芯板开槽补偿大小加铣机加工公差0.050 mm。相比内埋子板,双面嵌子板的对准度规律与板边对准度均值对齐性较高。

上述现象的主要因为双面嵌子板在埋入前未制作图形,压合与对应层次的芯板一同制作图形,双面嵌子板的图形与芯板图形有较高的一致性,对准度水平相当,且不会受到开槽补偿大小的影响,而是与图形制作时的涨缩直接相关,因此TCFA对其对准度的提升明显。而内埋子板为先制作子板上的图形后埋入压合,对准度受到芯板开槽大小的影响比较明显,芯板开槽单边补偿0.075 mm、0.10 mm、0.125 mm,对准度能力均值分别为0.12 mm、0.14 mm、0.18 mm。但其对准度与芯板图形的涨缩是否匹配关系较小,TCFA对齐对准度能力几乎无提升。

表1 关键流程实验内容

图3 子板层间对准度结果

在内埋子板排板与压合的过程中,容易产生滑板层错的现象,即因子板太薄,外力作用下滑出槽孔,滑入上下层间,在压后产生明显的板面鼓起。使用铆钉铆合预排与PIN对位排板的层错出现概率分别为16.7%和0,由此可见PIN对位排板减少了子板埋入后的搬运过程以及其他外力的作用,最大程度杜绝了内埋子板层错的发生。

2.2 交界处平整度

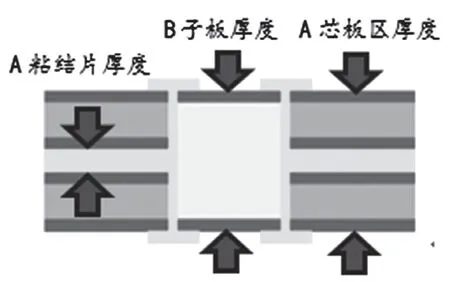

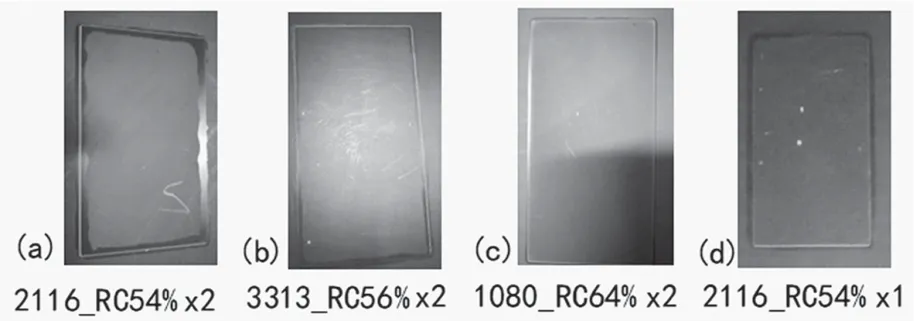

通过A粘结片理论厚度及芯板残铜率计算A粘结片的理论压合后厚度,通过A材料区叠层信息计算A材料区理论厚度,制作切片观察测量实际双面嵌B子板的A、B材料区域压后实际厚度,平整度分析模型(如图4、见表2和图5)。

图4 平整度分析示意图

由图5中的流胶量可知:2116_RC54%×2> 3313_RC56%×2>1080_RC64%×2>2116_RC54% ×1;相对交界的流胶趋势:2116(54)×2向子板内,3313(56)×2分布均匀,1080(64)×2向子板外,2116(54)×1向子板外。由表中的平整度数据可知2116_RC54%×2理论厚度与实际厚度相当,其余三种方案实际厚度均高于理论厚度,其中1080_RC64%×2与2116_RC54%×1实际高于理论厚度约50 μm,而3313_RC56%×2仅高于理论厚度25 μm且与B子板厚度相当。

表2 平整度分析结果

图5 各粘结片方案流胶情况

由此可推论:(1)当A芯板区理论厚度>B子板厚度,A芯板区板材受压,实现理论压后厚度且表面流胶量大,而B子板厚度相对固定,则A芯板区实际厚度≈A芯板区理论厚度>B子板厚度,A芯板区界面偏高,如方案1所示;(2)当B子板厚度-50 μm≤A芯板区理论厚度≤B子板厚度,A芯板区区域轻微失压或不失压,约50 μm以内的高度落差在双粘结片的调节能力之内,A芯板区实际厚度≈B子板厚度,界面平整度较好,如方案2所示;(3)当A芯板区理论厚度<B子板厚度-50 μm,B子板受压,A芯板区区失压,但高度落差超过粘结片调节能力,因此A芯板区理论厚度<A芯板区实际厚度<B子板厚度,B界面偏高,如方案3、4所示。因此该通埋子板结构在叠层设计时,混压区A芯板区的理论厚度应较通埋子板理论厚度少0~50 μm为宜,给予A芯板区粘结片调整自身板材区域厚度的空间,且尽量使用多张粘结片压合,避免填胶空洞导致子板脱落的情况。

2.3 交界处线路制作

内层制作图形后在末端的Pad处测试线路的通断情况,每种线宽测试96组,分垂直于倾斜45°跨越交界处,制作良率(如图6)。

当交界处线宽制作由50 μm(2 mil)提升良率也呈正比上升,当线宽在125 μm(5 mil)以上时良率在100%。实验中线路设计垂直跨过交界的内层导通线以及倾斜45°跨越交界处两种。垂直走线与倾斜走线的良率分别为98.2%和92.1%,良率存在差距,垂直走线的良率更高,主要原因为在线路跨过交界处的过程中,因为交界处仅有沉铜电镀的铜厚,线宽会变细,原料芯板底铜18 μm(0.5 oz)时,线宽变细约18 μm~25 μm,垂直走线可尽可能缩减线路变细的距离。交界导通线制作良率除了受线路设计,干膜、曝光、蚀刻等图形制作流程影响外,也受平整度影响,平整度较差时导致交界两边基材平面错位,交界周围残胶难除,影响线路制作。

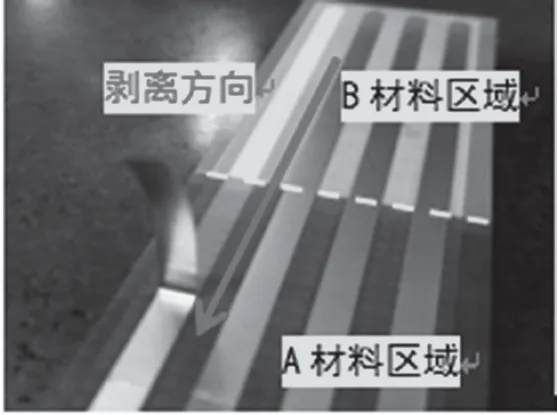

2.4 剥离强度

制作宽度为2.54 mm的铜条横跨交界线,用于测试导体剥离强度,如图7所示。测试设备使用剥离强度测试仪,由B向A材料剥离,剥离速度调整至尽可能低,在B与A材料区取数值稳定后的均值,在交界区剥离强度取经过交界过程的数据的最小值。

图6 跨交界处线路制作良率与表观图汇总

图7 剥离强度测试方法

实验除正常制作与测试组外,2组对照组分别为化学铜(离子钯体系)前进行等离子体粗化处理,以及正常制作样品的260 ℃峰温回流3次后的测试结果,数据(如表3)。

实验中常规流程制作的B与A材料上的导体剥离强度属于该板材正常水平。在化学铜之前的进行等离子处理,结果中A材料与B表面剥离强度变化较小,交界处的剥离强度提升24%,证明增加交界处化学铜与树脂接触的表面积。回流焊后各区域剥离强度均有下降,B子板下降幅度大。

2.5 耐热可靠性

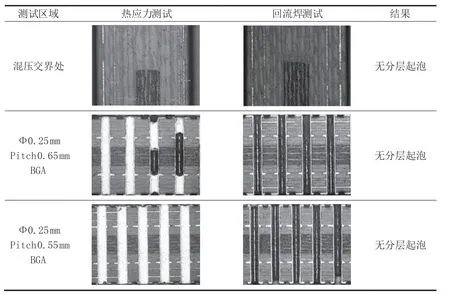

测试条件:(1)热应力测试无铅漂锡:(288±5)℃,10~1s,3次;(2)无铅回流焊测试:217 ℃以上120~150s,峰温(260±5) ℃,255 ℃以上20~30s,5次。测试对象:双面嵌子板与内埋子板的混压交界处以及多种规格的BGA密集孔区域,耐热可靠性测试结果(如图8~图9)。

由图8可知双面嵌子板结构的混压交界处仅0.25 mm孔径、0.55 mm Pitch 密集孔阵在A材料的7038的粘结片层在回流漂锡后均出现了玻纤分层开裂的情况,主要原因为7038粘结片树脂含量较小,玻纤层较厚,树脂浸润性较差,该规格耐可靠性能力普遍相对较低,BGA制作能力在0.65 mm以上Pitch的密集孔阵。由于该分层现象与双面埋子板的可靠性关联较小,在BGA的混压交界面均无分层,可认为双面嵌埋子板的耐热可靠性符合要求。

表3 剥离强度测试结果(单位:lb/in)

图8 双面嵌B1子板可靠性测试结果

图9 内埋B2子板可靠性测试结果

由图9测试结果可知无分层起泡的现象,说明内埋混压结构以及板材耐热可靠性符合要求。

3 结论

双面嵌子板结构下的模块间内层导通工艺以及内埋子板工艺设计具备实际产品可行性。满足高频高速PCB的导体剥离强度要求,交界处导体剥离强度为0.31 N/mm,化学铜前等离子体清洗可一定程度提升交界导体结合力;跨交界处线路制作良率50 μm线宽在90.2%以上,线宽增加良率也提高,能力满足要求;双面嵌与内埋子板的混压结构的热应力测试与回流测试均符合要求。

双面嵌子板结构对准度能力提升的主要途径为涨缩系数匹配试验,对准度能力与整板水平相当,与开槽尺寸设计无关。内埋子板对准度提升主要途径为减小开槽大小,与整板对准度能力无关,使用PIN对位排板压合以及子板厚度≥0.5 mm可降低层错位的风险;为保证双面嵌子板的压合平整度与填胶量,局部混压嵌子板的芯板区理论厚度设计应较埋子板理论厚度少0~50 μm为宜,这样可获得较好的埋入界面平整度,并保证模块间连通线路具有较高的制作能力。