抗辐照工艺器件ESD性能研究

谢儒彬,纪旭明,吴建伟,张庆东,洪根深

(中国电子科技集团公司第五十八研究所,江苏无锡214035)

1 引 言

随着半导体技术的不断发展,超大规模集成电路(Very Large Scale Integrated circuit,VLSI)的性能在过去的几十年里提高了5 个量级,集成电路芯片不断向小型化、高密度化和多功能化方向发展,相应地,集成度也不断得到提升,目前的集成电路芯片己具备集成数以亿计的晶体管的能力。然而与此同时,工艺尺寸的缩小也面临着很多障碍,例如器件与电路的可靠性问题。在可靠性问题方面,静电放电/静电过应力(ElectrostaticDischarge/Electrical Over Stress,ESD/EOS)则是导致集成电路(Integrated Circuit,IC)失效的主要原因[1]。统计表明有近30%~50%的芯片失效是由ESD/EOS 导致的[2-3]。

随着工艺特征尺寸的降低,芯片面积不断缩小,芯片能够承受的ESD 耐压水平则不断下降,从高于3000V 降低到1000V 左右。同时随着电源电压的不断降低,ESD 设计窗口也在趋于向低压领域发展。总体来看,CMOS 工艺尺寸的持续缩小使ESD 设计窗口变得更窄,使得电子工程师在进行电路设计及芯片可靠性防护设计时的难度也日益提高[4-5]。IC 工艺发展与ESD 设计窗口示意图如图1所示。

图1 IC 工艺发展与ESD 设计窗口关系示意图

国外对于ESD 的研究始于上个世纪末,国际上最早在1979年成立了EOS/ESD 研究协会,主要研究的就是集成电路的EOS 和ESD 问题。另外,美国军方为保证电子器件能在恶劣环境下安全可靠地使用,提出了美国军用ESD 测试标准[6],而国内军用集成电路规范也对芯片的抗ESD 能力提出了明确要求,军品电路的抗ESD 能力必须大于2000V。

故此,基于抗辐照0.18μm CMOS 工艺对器件的ESD 性能进行研究,为提升电路的抗辐照性能,采用薄外延衬底材料片,并引入总剂量工艺加固技术[7]。针对在研究过程中发现的工艺加固措施对器件抗ESD 能力的影响,也对器件结构与ESD 工艺进行了优化。

2 器件研究

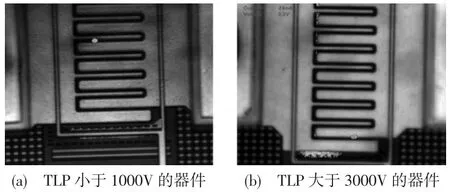

ESD 保护器件是芯片ESD 保护设计中最核心的基本单元。单个器件的设计成功与否直接关系到整个芯片保护设计能否实现。常规的ESD 保护器件有二极管、BJT 晶体管、栅极接地NMOS 晶体管(Grounded Gate NMOS,GGNMOS) 和可控硅 SCR等,可根据应用情况选择不同的ESD 保护器件。在CMOS 工艺中,一般是采用GGNMOS 器件作为ESD保护器件,其ESD 保护原理示意图如图2所示。

图2 GGNMOS 器件ESD 保护原理示意图

在ESD 事件发生时,起保护作用的ESD 保护器件要承受大电流与高电压,而在大电流与高电压的情况下,半导体器件的工作方式会发生很大的变化。ESD 事件是短时间的大电流放电事件,因此研究ESD 单体器件在此状况下的工作机制非常有必要。

在普通NMOS 的基础上对源电极、栅电极、体电极和地短接。它的保护方向是由漏到源,当漏端承受ESD 应力时,由于栅极接地,NMOS 处于关闭状态,漏区与P 阱的反向PN 结承受大部分的ESD 电压。当其承受的反向电压达到此PN 结的反向击穿电压时,P 阱中就会有少量电流通过,当P 阱体电位的电势大于PN 结的正向开启电压0.7V 时,P 阱与源极导通,从而促使整个NMOS 管导通,将漏源电压钳位在一定的电压范围内,ESD 电流可以通过导通的NMOS 进入GND,达到保护内部电路的目的。

单指条GGNMOS 往往保护能力有限,无法达到所需的ESD 保护等级,因此在版图设计中常常将GGNMOS 画成多指条结构。通常为达到一定的ESD水平需要较大的器件宽度,但若无限增大单叉指GGNMOS 保护器件的宽度,一方面达不到IC 版图布局中对面积利用率的要求,另一方面也容易引发叉指导通均匀性问题,因此一般需将保护器件叉指布局为梳状交叉的多叉指结构,以多个NMOS 管并联的方式增大器件总宽度来提高ESD 耐受水平。

3 实验与分析

从器件ESD 保护原理图上可以看出,为保证多叉指结构的均匀开启,需要提升P 阱体区的电阻,使得体电位能够尽快达到PN 结正向开启电压0.7V,但是在抗辐照薄外延工艺中,需要通过减小外延层的厚度来提升体区的掺杂浓度,以解决器件单粒子闩锁问题,因此抗单粒子辐射加固工艺措施与ESD性能提升方案相矛盾。由此可见,在抗辐照薄外延工艺中,器件的抗ESD 能力会出现减弱的问题。

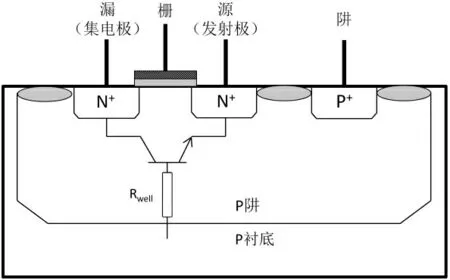

鉴于上述分析中薄外延工艺会对电路的抗ESD能力造成影响,先对采用薄外延工艺制备的电路进行ESD 测试,将其与厚外延工艺制备的电路进行比较,对比结果如表1所示。

表1 不同工艺电路抗ESD 能力对比

从表中可以看出,薄外延工艺的电路抗ESD 能力较弱,无法满足要求,同时比较标准工艺与加固工艺电路的抗ESD 能力,加固工艺电路抗ESD 能力更差。

针对加固工艺的GGNMOS 器件进行TLP 分析,结果显示器件的It2均小于0.67A,说明器件抗ESD 能力均小于1000V。具体I-V 特性曲线见图3。

图3 加固工艺ESD 保护器件TLP 测试结果

1#~4#器件分别表示不同的DCGS 设计尺寸,从上图分析可得,对DCGS 进行细微的拉偏,器件的二次击穿电流It2变化不明显,说明对器件的抗ESD 能力影响不大;而所有的器件二次击穿电压Vt2都小于一次击穿电压Vt1,说明叉指导通后电压骤回,之后由于漏电压无法达到触发电压而使其他叉指无法导通,使多叉指保护器件远没有发挥其全部性能而过早击穿失效。由此说明,不均匀导通现象是导致多叉指结构器件的抗ESD 性能下降的主要原因。

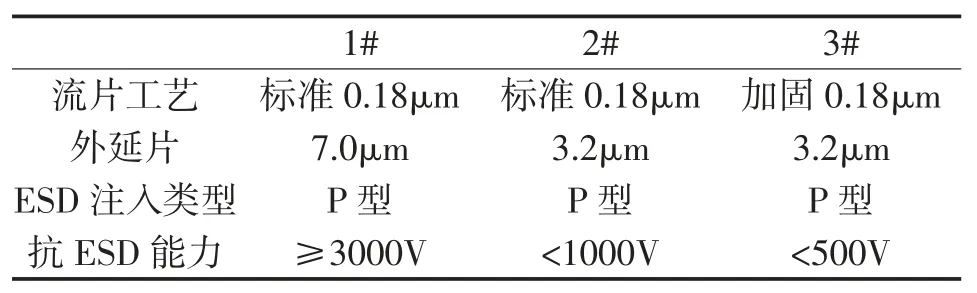

对击穿的保护器件进行EMMI 分析,如图4所示。由图中可发现击穿位置位于器件中间区域,该部分区域的叉指器件应该是最先触发的,说明可能该部分区域叉指器件触发并击穿后,其他区域的叉指器件仍然没有触发;对比抗ESD 能力正常的保护器件,可以发现,其击穿区域在边缘位置,说明边缘的叉指器件得到了充分的利用。

图4 叉指保护器件EMMI 分析

通过分析可以认为,由于采用了薄外延衬底,其衬底电阻值较小,因此无法有效触发寄生双极管,导致多叉指结构器件触发不均匀,使得器件的抗ESD能力下降。

同时对 3.2μm 与 4μm 外延材料器件的 TLP 测试结果做出对比,其结果如图5所示。图中,器件的总沟宽为480μm,两种外延材料所制备的器件均未采用ESD 注入。

图5 不同外延材料GGNMOS 器件TLP 结果对比

从结果上可以看出,采用 4.0μm 外延的GGNMOS 器件抗ESD 结果优于3.2μm 外延的器件。4.0μm EPI 器件的TLP 曲线中出现了二次骤回的现象,说明不止一个叉指结构发生了触发,因此器件的It2明显增大;与之相对,3.2μm EPI 器件的 TLP 曲线中,只能看到一次骤回现象,结合之前的EMMI 试验结果,可认为只有中间部分的叉指结构发生了触发,触发不均匀导致器件抗ESD 能力变弱。

从电路的ESD 结果还可以看出,采用了加固工艺后,电路的抗ESD 能力出现下降的情况。通过分析可认为这是由于加固工艺造成漏端边缘的电阻值下降,使得击穿的位置出现在有源区边缘而不是在漏端下方。

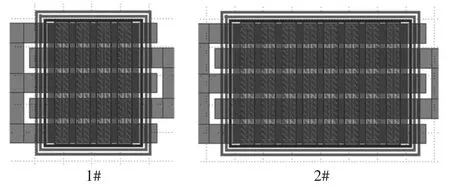

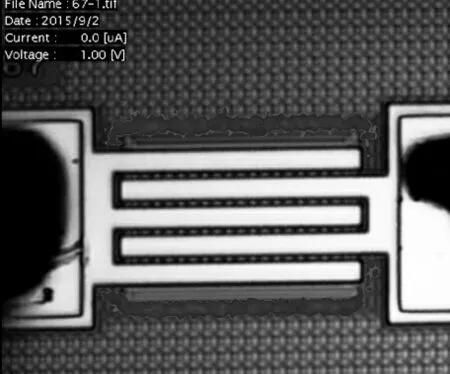

为此针对加固工艺的3.3V GGNMOS 器件做了TLP 测试,将击穿后的器件进行了OBIRCH 分析。两种GGNMOS 测试结构的版图形态如图6所示,其中1#结构为8 指,2#结构为16 指。

图6 3.3V GGNMOS 器件测试结构示意图

1#测试结构TLP 测试曲线及测试后的I-V 曲线如图7所示。可见,其TLP 能力在2.6A。由曲线还可看出该测试结构经TLP 打坏后已成为一个电阻,阻值约160Ω。

图7 1#测试结构TLP 相关曲线

对1#测试结构再进行OBIRCH 分析,如图8所示。结果显示其亮点位置位于有源区中间部分,说明器件的击穿无明显异常。

图8 1#测试结构TLP 后OBIRCH 分析结果

2#测试结构TLP 测试曲线及测试后的I-V 曲线如图9所示。可见其TLP 能力在1A 左右。器件漏电突然变大,但并没有完全击穿;I-V 曲线显示漏端接3.3V 时,漏电流为38nA。

图9 2#测试结构TLP 相关曲线

对2#测试结构再进行OBIRCH 分析,如图10所示。结果显示,亮点位置在TO 边缘,说明击穿位置在有源区边缘而不在漏端下方,由此造成器件的抗ESD 能力变弱。

图10 2#测试结构TLP 后OBIRCH 分析结果

因此,随着叉指数目变大(从8 到16),3.3V GGNMOS 击穿点由有源区中间转移到边缘,不利于寄生BJT 开启,起不到ESD 保护的作用。

针对由于引入抗辐照薄外延加固工艺造成的ESD 能力下降的问题,对ESD 工艺进行优化,目标是使漏端中间位置比边缘位置更早击穿,实现寄生BJT 的开启,提高抗ESD 能力。

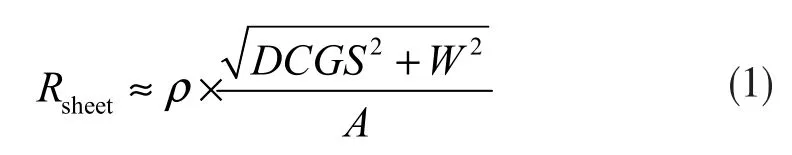

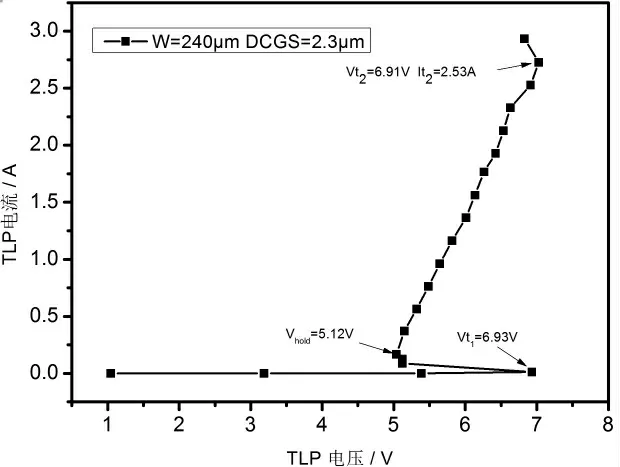

根据文献[8]调研可知,漏极接触孔到栅极的间距(DCGS)将影响器件的二次击穿电流。通过实验分析发现,随着DCGS 的增大,保护器件的二次击穿电流It2呈增大趋势。当DCGS 刚开始增大时失效电流水平几乎是成倍地快速增大,但当DCGS 增大到一定值后失效电流值的增速明显降低,趋于饱和值。不同DCGS 尺寸器件的TLP 能力如图11所示。由图中可以看出,对于本工艺的GGNMOS 器件,最优的 DCGS 尺寸为2.3μm。

图11 不同DCGS 尺寸器件的TLP 能力

通过分析,可以认为当DCGS 值增大时,在正向ESD 应力下的反偏漏衬结电容值会增大,并且由于静电应力注入的总电荷不变,因此结上的电压将随DCGS 的增大而减小,从而导致寄生LNPN 导通面积增大,这有助于扩展ESD 电流沿着叉指宽度均匀分布,从而改善了二次击穿电流的有效值。

另外,漏扩散区中的薄层电阻值可由如下公式估算:

其中ρ 为电阻率,W 为器件宽度,A 为漏区在ESD应力下的导通面积。当DCGS 增大时,薄层电阻值将增大。但是,根据前述分析可知DCGS 的增大还伴随着导通面积的增大以及漏衬结反偏电压的下降,因此寄生LNPN 管的有效导通电阻会减小。因此,在较大DCGS 值下二次击穿电流It2增幅趋于饱和。

综上所述,可通过优化ESD 工艺和DCGS 尺寸,来提高器件的抗ESD 能力。优化之后的TLP 结果如图12所示。从TLP 测试结果来看,经过优化后GGNMOS 器件的抗ESD 能力明显提升,器件抗ESD 水平大于3500V。为研究ESD 注入的均匀性,取圆片上不同位置的9 个点,测试3.3V GGNMOS器件的TLP 结果,分析此9 点测试数据,统计结果如图13所示,可见器件抗ESD 水平的均匀性良好。

图12 优化后GGNMOS 器件TLP 测试结果

图13 ESD 注入均匀性测试概率图

至此,可得出以下结论:

1)采用薄外延工艺提升电路的抗单粒子闩锁能力,减小器件体区电阻,由此会造成GGMOS 器件抗ESD 能力减弱,采用场区加固工艺的NMOS 器件,由于加固工艺造成GGNMOS 器件场区边缘提前击穿。

2)通过优化ESD 工艺,使得有源区中间位置比边缘位置更早的击穿,实现寄生BJT 的开启,提高抗ESD 的能力;

3)通过工艺优化,GGNMOS 器件抗ESD 能力大于3500V,将器件应用于抗辐照DSP 电路中,可令电路的抗ESD 能力大于3000V。

4 结束语

通过介绍抗辐照薄外延加固工艺对GGNMOS器件ESD 保护能力的影响,分析工艺中薄外延材料及抗总剂量辐射加固工艺造成器件的抗ESD 能力下降的情况,在GGNMOS 器件设计中对器件的关键尺寸进行了优化,同时还需配合ESD 优化工艺,最终可保证电路的抗ESD 能力大于3000V,满足科研开发中的实际应用需要。