大容量存储器高可靠性3D封装技术研究

刘 笛

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引 言

存储器电路在网络数据安全、分布式计算、高速数据采集、大数据存储、工业智能化、太空数据存储、电子信息对抗等领域被广泛使用。特别是大容量、高可靠存储器电路在飞机、卫星和火箭上的需求越来越大。我国的存储器电路产品,一般以单芯片塑封为主,有效存储容量与封装面积的比例不高,不能满足尖端行业对大容量存储的需求。一些封装厂商采用多芯片3D 堆叠封装的方法,可以大幅度提高存储容量与封装面积的比例,但提出的3D 封装方案基本上也都是以塑封为主[1-3]。3D 塑封方案虽然在存储容量上有所提升,但由于塑封自身特点,在可靠性上存在不足之处。总而言之,现阶段国内产品很难同时满足航空航天等领域对存储器产品的大容量和高可靠需求。

故此研究一种大容量存储器电路高可靠堆叠封装方法,以陶瓷外壳完成存储器芯片的3D 封装。不但可提高单只电路的储存容量,还可以满足国内外各类尖端行业对储存器产品的高可靠性需求。

2 储存器3D-SiP 产品可靠性设计

2.1 3D-SiP方案设计

对于高可靠3D 堆叠,行业内还没有公认的最优解决方案,各个封装厂商根据自己的优势采用不同的方法来实现用户的需求,主要途径有4 个:

第一:塑封方案,如图1所示。在3D 堆叠方面,塑封较为容易实现。但塑封本身存在气密性、热应力等问题,在高可靠领域仍然不具备优势。

图1 军品3D 塑封方案外观示意图

第二:类3D-Plus 模块灌封方案,如图2所示。依靠多层基板和多层芯片叠装灌封,再通过侧面金属化、互连和涂漆保护,完成模块封装。该种方案可以实现更为复杂的堆叠互连,但与塑封类似,所完成的模块产品在可靠性上存在先天不足。另外这种方案的造价也很高。

图2 类3D-Plus 模块灌封方案

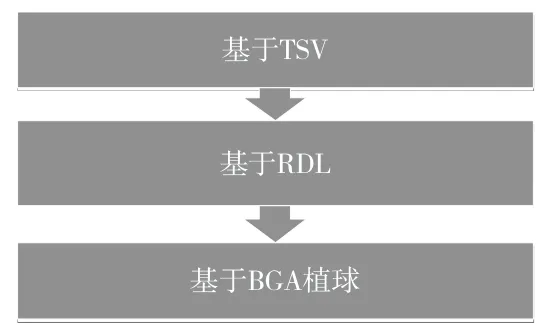

第三:基于TSVRDLBGA 植球的晶圆级3D 堆叠方案,如图3所示。这种方案技术含量较高,成本也较高。同时,如果需要TSV 通孔,芯片在设计时需要先预留出通孔空间。

图3 基于TSVRDLBGA 晶圆级3D 堆叠方案

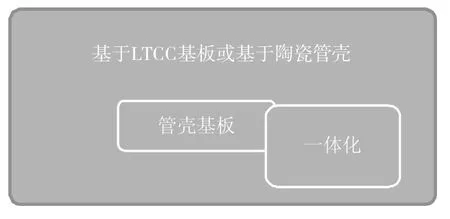

第四:基于LTCC 基板或者基于陶瓷外壳的管壳基板一体化的堆叠方案,如图4所示。

图4 管壳基板一体化堆叠方案

四种方案相比,能实现气密封装的是方案3 和方案4,此两种方案都有达到宇航级要求的潜力。考虑到技术成熟度和自主可控,方案4 更佳。

2.2 3D-SiP工艺设计

所设计的产品采用陶瓷气密封装,如图5所示。外壳采用CQPF 封装形式,引脚可以从外壳底面引出,也可以从外壳侧面引出,按照用户习惯选择。电路设置64 只外引脚。外壳具有多层键合指,键合指高度按照芯片堆叠后的高度设计,使芯片PAD 点高度与键合指高度基本保持一致。

图5 3D 封装陶瓷外壳及互联关系设计

产品采用国内堆叠封装比较常用的双腔管壳设计方案,在上下两个独立的腔体内分别堆叠芯片[4]。各芯片采用引线键合的方式与陶瓷外壳完成电连接。各芯片间的互联关系由陶瓷外壳中间层内部布线完成,并引出至管壳外引脚。电路组装结构如图6所示。

图6 3D 封装陶瓷外壳及互联关系设计

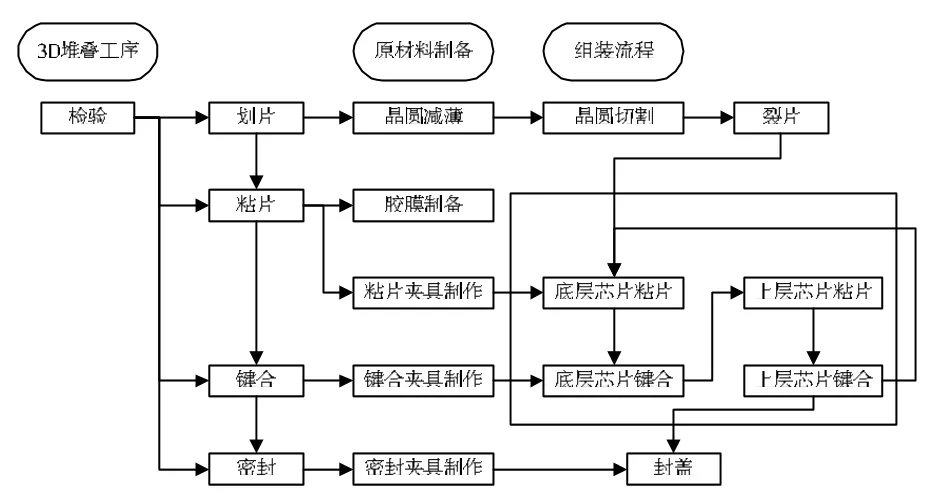

组装过程中,为了控制芯片贴装精度和芯片粘接材料的流淌范围,选用不导电胶膜作为粘接材料。为了实现叠层芯片的低弧度键合、避免键合引线与上下层芯片发生短路,选用BSOB 引线键合技术。为了降低电路的组装过程温度,最后的封盖方式选用平行缝焊工艺。该电路3D 堆叠工艺的核心步骤是多层芯片的粘接和键合,晶圆减薄工艺和平行缝焊密封工艺也较为关键,整体工艺流程如图7所示。

图7 3D 堆叠封装工艺选择及组装流程

2.3 高可靠产品考核试验设计

按照用户的需求,该电路质量等级至少满足一般民用和工业级要求,研制目标瞄准宇航级标准。为此,所设计的考核试验条件参照GJB548B-2005相关要求。针对样品电路进行了考核试验。表1 中列出了一些关键的考核项目和条件。

表1 关键考核试验及条件

3 3D-SiP封装典型失效模式及优化方案

3.1 芯片叠层粘接中的热应力

热匹配是3D 封装要考虑的重要因素,纵向多芯片的堆叠更是如此。早期研制过程中,考虑到目检可以观察到粘接剂从芯片四周溢出的轮廓,在芯片下方悬空的部分进行了不导电胶的填充和加固。将硅片切割成与待封装芯片同等尺寸的大小,堆叠至两层、三层、四层,按照表1 中的关键试验项进行摸底试验。结果表明,填充了不导电胶的电路发生了热失配现象,在温度循环后,上层芯片均发现了不同程度的裂纹,裂纹沿底层芯片边缘位置延展,逐步扩展,最终横向贯穿整个芯片,如图8所示。

图8 芯片堆叠出现裂纹

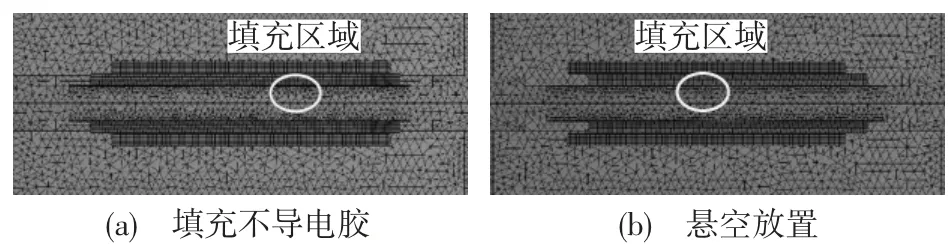

建立3D-SiP 器件的有限元模型,对温度循环热应力进行仿真分析。第一层和第二层芯片之间不导电胶填充区域模型网格划分如图9所示,材料属性如表2所示。

图9 不导电胶填充区域模型网格划分

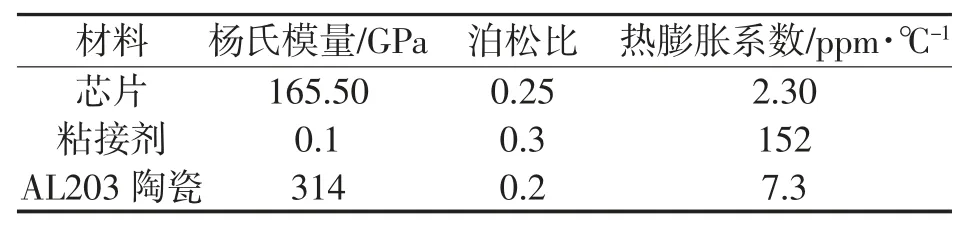

表2 材料属性表

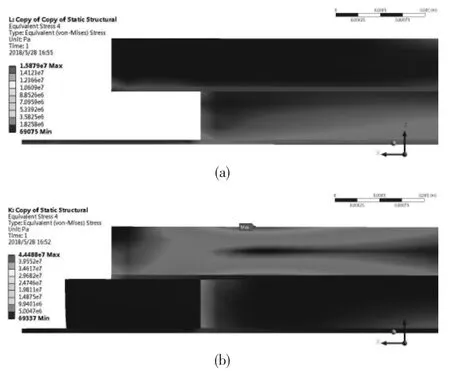

如图10所示为堆叠样品第一、第二层芯片在温度循环试验中的热应力分布情况。从仿真结果看,填充不导电胶之后,在温度循环试验过程中,上层芯片最大应变为44.4MPa,如图10(a)所示。如果不填充,上层芯片相同位置的应变则为3.7MPa,如图10(b)所示,相对减小了91.7%;上层芯片最大应力位置出现在芯片中央,数值为15.9MPa,比填充不导电胶的最大应力减小64.1%。因此,在后续的产品中,皆采用芯片悬空堆叠的方法,并且注意胶膜的选型,以保证外壳、芯片、粘接剂等材料间的热匹配性。

图10 堆叠样品热应力分布仿真

3.2 双面叠层引线键合中的质量控制

引线键合过程中,涉及到双面键合、低弧键合、悬臂键合等多项关键技术,其中部分区域还应用到了Die-To-Die 引线键合技术,因此,应从工艺参数、设备选型、劈刀定制、外壳设计等多个方面进行协同设计。考虑到金丝在上述工艺技术中具有良好表现,键合方案采用金丝球键合工艺。

本项目以BSOB 作为核心键合技术: 预先在芯片焊盘植一个金球形成凸点,线弧第一点落在管壳键合指或基板上,第二点落在芯片焊盘的金凸点上。BSOB 技术使芯片端弧高明显降低,可达到80 微米以下,同时避免了引线-芯片短路。此外,预先形成的金凸点有效保护了芯片焊盘,减小了芯片受损的可能性[5-6]。如图11所示为采用了BSOB 技术的样品。

图11 BSOB 键合技术实物图

芯片叠层为键合带来了两个问题:

(1) 键合温度梯度。由于芯片堆叠,加热台预热温度传导受到阻碍,使得上层芯片温度低于下层芯片温度,形成温度梯度。

(2) 键合压力缓冲。叠层封装的上层芯片边缘悬空,悬空部分对劈刀施加的能量起到分散减弱的作用,不利于键合。

问题主要体现在两个方面,一个是短尾(Short Tail,SHTL),另一个是引线焊盘不粘(Non-Stick On Pad,NSOP)。应对措施是优化键合参数,针对不同层芯片采用不同的键合工艺方案,每一层都在功率、压力和时间之间寻找最优匹配。

由于高可靠的要求,在键合后,对电路抽样进行300℃、1h 的高温烘焙,确保键合质量的可靠性。

3.3 双面平行缝焊的焊接应力

国内双腔管壳多采用双面金锡焊料环熔封或单面金锡焊料环熔封、单片平行缝焊等工艺。鉴于芯片贴装的工艺温度较低,在设计密封温度梯度时不宜采用熔封工艺,以免对芯片粘接的可靠性造成影响。据了解,采用双面平行缝焊密封工艺在国内几乎没有先例,技术关键点在于密封过程工艺参数的优化,避免温度和应力造成的陶瓷管壳裂纹,以及焊接应力在考核试验中的释放所导致的漏气[7]。

应对措施是减小平行缝焊功率,增大电极X、Y向移动速度,缩短焊接总功率[8]。采用工艺优化方案后,电路在考核试验后可依旧保持良好性能。

4 结束语

提出大容量数据存储电路的3D-SiP 封装方案,采用叠层芯片粘接、BOSB 键合及双面平行缝焊工艺等可靠性设计及工艺优化,极大提高了陶瓷外壳内堆叠芯片的数量,使单一电路的存储容量达到世界一流水平,可适用于大数据和云计算等战略性新兴产业以及高可靠性如飞机、雷达和卫星等领域。