计算机专业数字逻辑实验的设计与实践

唐志强

(复旦大学计算机科学技术学院,上海200433)

0 引言

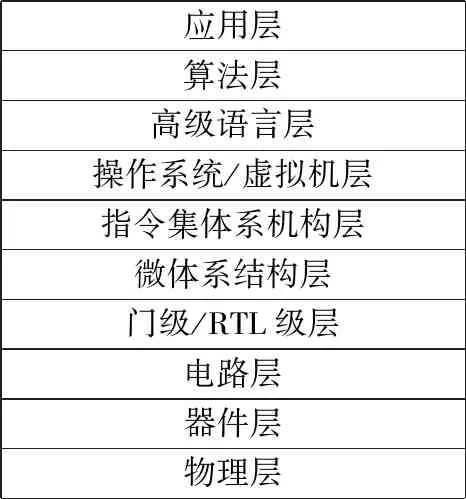

计算机硬件类核心课程有数字逻辑、计算机组成原理和计算机体系结构[1-4],根据计算机系统的层次(见图1),数字逻辑电路位于相关课程的底层,相当于电路结构层和门级/RTL级层,传统设置的这些课程相互独立,没有关联,缺少课程之间的衔接,有的内容重复;学生学完这些课程后,对计算机的系统结构,特别是CPU的设计实现仍然不是很清楚。要深入理解计算机系统的硬件架构,必须掌握数字逻辑电路,而上面一层中的微体系结构,就是计算机组成原理,其核心是CPU的设计技术,属于复杂数字系统设计。有限状态机和寄存器传输控制是CPU设计的核心;指令集体系结构,属于更高层次的计算机体系结构。根据ACM CS2013规范对数字逻辑课程的知识点[5]进行了重新梳理,为学生提供良好的实践环境,克服计算机专业学生中普遍存在的“欺软怕硬”的现象。同时,结合十二五国家级实验教学示范中心建设[6-7],对计算机专业硬件类课程进行了重新规划:把传统的数字逻辑改成数字逻辑与部件设计,增加了计算机部件的设计,设计了新的实验体系,并根据系统观的要求设计了计算机硬件一体化实验仪,用于数字逻辑、计算机组成及计算机体系结构的实验。

1 实验内容

ACM CS2013规范中,数字逻辑课程的知识点涉及三个知识单元[8-10]:数字逻辑与数字系统、功能模块及计算模

应用层算法层高级语言层操作系统/虚拟机层指令集体系机构层微体系结构层门级/RTL级层电路层器件层物理层

图1 计算机系统的层次结构

型。数字逻辑与数字系统知识单元包含传统数字逻辑的知识点:组合逻辑和时序逻辑;逻辑设计和CAD工具;状态机,计数器;数字构造模块;寄存器传输符号表示/硬件描述语言(Verilog/VHDL) 。功能模块知识单元包含计算机组成部分知识点:单周期数据通路及的实现。计算模型知识单元包含:数据通路+控制+存储器。数字逻辑与数字系统知识单元对应的实验有:Verilog语言及Vivado开发环境[11-13];编码器和译码器;七段显示译码器;加法器和算术逻辑单元;计数器和有限状态机。

1.1 编码器和译码器实验

编码器和译码器是计算机中最常用的基本电路。译码器用来完成对操作码的译码。编码是把输入的高低电平信号编成一个对应的二进制码。实现编码操作的电路称作编码器;按是否有优先权编码,可分为普通编码器和优先编码器。

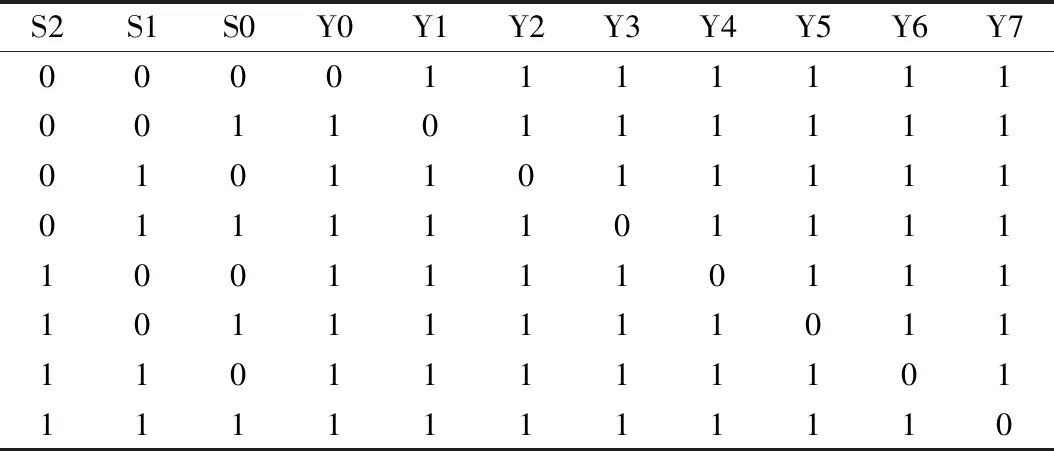

3-8译码器有3个输入S0、S1、S2,8个输出Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7。3-8译码器的真值表如表1所示。

表1 3—8译码器的真值表

需要注意的是三个控制信号,变量tmp=G1&~G2A&~G2B为1时,译码器工作。

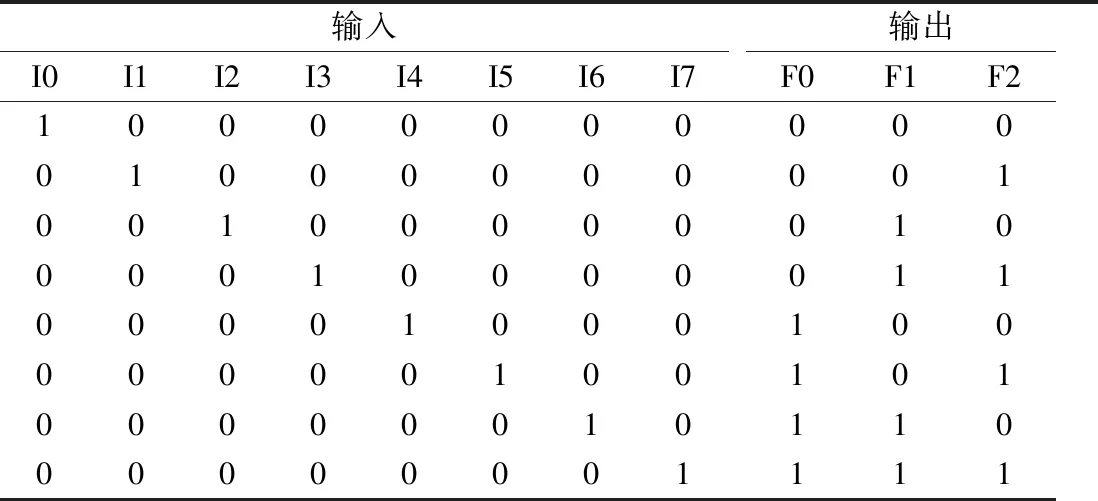

8-3编码器有8个输入I0、I1、I2、I3、I4、I5、I6、I7,3个输出F0、F1、F2。8-3编码器的真值表如表2所示。

表2 8—3编码器的真值表

要求用Verilog语言实现编码器和译码器,然后下载到实验板,用开关作为输入,用LED表示输出。

1.2 算术逻辑单元实验

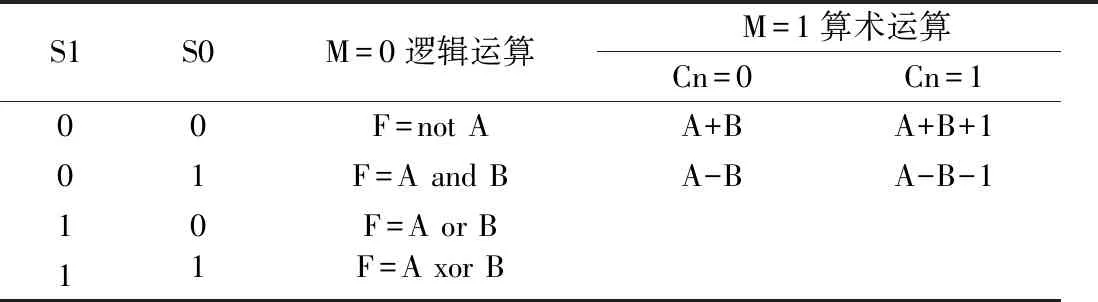

算术逻辑单元是CPU的核心部件,实现算术及逻辑运算。实验内容:设计一个8位算术逻辑单元,输入信号为:两组8位数据信号(A7—A0,B7—B0),一个进位信号Cn;数据输出信号为:8位数据信号(F7—F0),一个进位输出信号Cn+8。功能控制信号S1、S0、M,当M=0时为逻辑运算,M=1时为算术运算,S1、S0的功能如表3所示。

表3 算术逻辑单元的功能

1.3 时序电路实验

基本时序电路的实验为计数器的设计[14],计数器是记录输入脉冲累计个数的功能部件,输入脉冲一般称为计数脉冲,也就是同步计数器的时钟脉冲。按计数脉冲引入方式不同,可分为同步计数器和异步计数器。按计数器的容量不同,可分为二进制计数器和N进制计数器;按计数器中数值增减的趋势不同,可分为加法计数器、减法计数器和可逆计数器。

74LS163是一个同步二进制计数器,它有4位数据输入D、C、B、A,4位数据输出QD、QC、QB、QA;同步清零端CLR,同步置数端LOAD,计数允许端P、T,进位输出RCO,时钟信号CLK。

1.4 总线实验

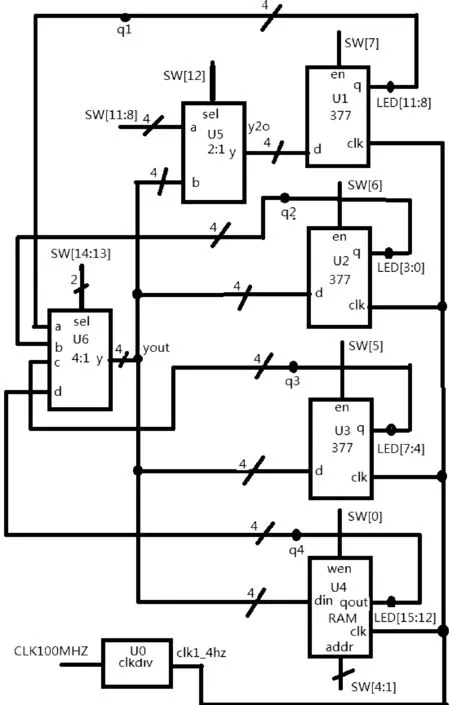

功能模块的实验有:总线实验;单周期数据通路的实现。总线实验见图2,系统由三个74377寄存器(U1,U2,U3)、一片RAM(U4)、一个2:1多路器(U5)、一个4∶1多路器(U6)及时钟分频电路(U0)组成。按图2要求,用Verilog结构模型描述上述系统,用SW开关模拟控制器控制微操作:把x存入U2,把y存入U3;以U4为暂存处,实现U2及U3寄存器内容的交换。重点掌握总线的分时特性、微操作及控制器控制微操作的概念[15-17]。

图2 总线实验框图

操作步骤如下:

第一个数x存入U2:先将SW[12]=0,U5选择输入端选中a,再拨动SW[11:8]=x输入到U5中。打开U1使能端SW[7]将U5中暂存的值传入U1,LED[11:8]显示x;再将4:1选择器U6的选择端SW[14:13]置00传入U1中暂存的值x.打开U2使能端SW[6],将x传入U2中暂存,再关闭SW[6]。此时输出端口LED[3:0]显示x。

y存入U3:同理,对U5,U6进行类似操作将y存入U5,U6,LED[11:8]显示y。打开U3使能端SW[5],将y存入U3,。此时LED[7:4]显示y.

将x和y互换:将U6选择端SW[14:13]置01存入U2中的值,打开U4选择端SW[0],LED[15:12]显示x,U2中的值存入U4;再打开U3使能端SW[5],将U2存入U3,关闭U3,U4使能端,将U6选择端置10存入y,打开U2使能端,将y存入U2,关闭U2使能端。最后将SW[14:13]置11,存入U4中暂存的x,打开U3使能端将x存入U3完成演示操作。Verilog代码如下:

module clkdiv(input mclk , output clka);

reg [28:0]q = 0;

always@(posedge mclk)

begin

q <= q + 1;

end

assign clka = q[24];

endmodule

module reg377(input [3:0] d , input en , input clk,

output reg [3:0] q);

always@(posedge clk)

begin

if(en)

q <= d;

end

endmodule

module MUX41(input [1:0] s , input [3:0] a , input [3:0] b

, input [3:0] c , input [3:0] d , output [3:0] bus);

assign bus =

s == 2'b00 ? a :

s == 2'b01 ? b :

s == 2'b10 ? c :

s == 2'b11 ? d :

4'b0000;

endmodule

module MUX21(input s , input [3:0] a , input [3:0] b , output [3:0] bus);

assign bus =

s == 1'b0 ? a :

s == 1'b1 ? b :

4'b0000;

endmodule

module ram2_4(

input clk,

input wen,

input [3:0] addr,

input [3:0] din,

output [3:0] qout

);

reg[3:0] ram[0:15];

always@(posedge clk)

if(wen)

ram[addr]<=din;

assign qout=ram[addr];

endmodule

module top(input CLK100MHZ , input [14:0] SW , output [15:0] LED);

wire myclk;

clkdiv(CLK100MHZ , myclk);

wire [3:0] q1 , q2 , q3 , q4;

assign LED[11:8] = q1;

assign LED[3:0] = q2;

assign LED[7:4] = q3;

assign LED[15:12] = q4;

wire [3:0] bus;

MUX41(SW[14:13] , q1 , q2 , q3 , q4 , bus);

wire [3:0] sub_bus;

MUX21(SW[12] , SW[11:8] , bus , sub_bus);

Reg377(sub_bus , SW[7] , myclk , q1);

Reg377(bus , SW[6] , myclk , q2);

Reg377(bus , SW[5] , myclk , q3);

ram2_4(myclk , SW[0] , SW[4:1] , bus , q4);

endmodule

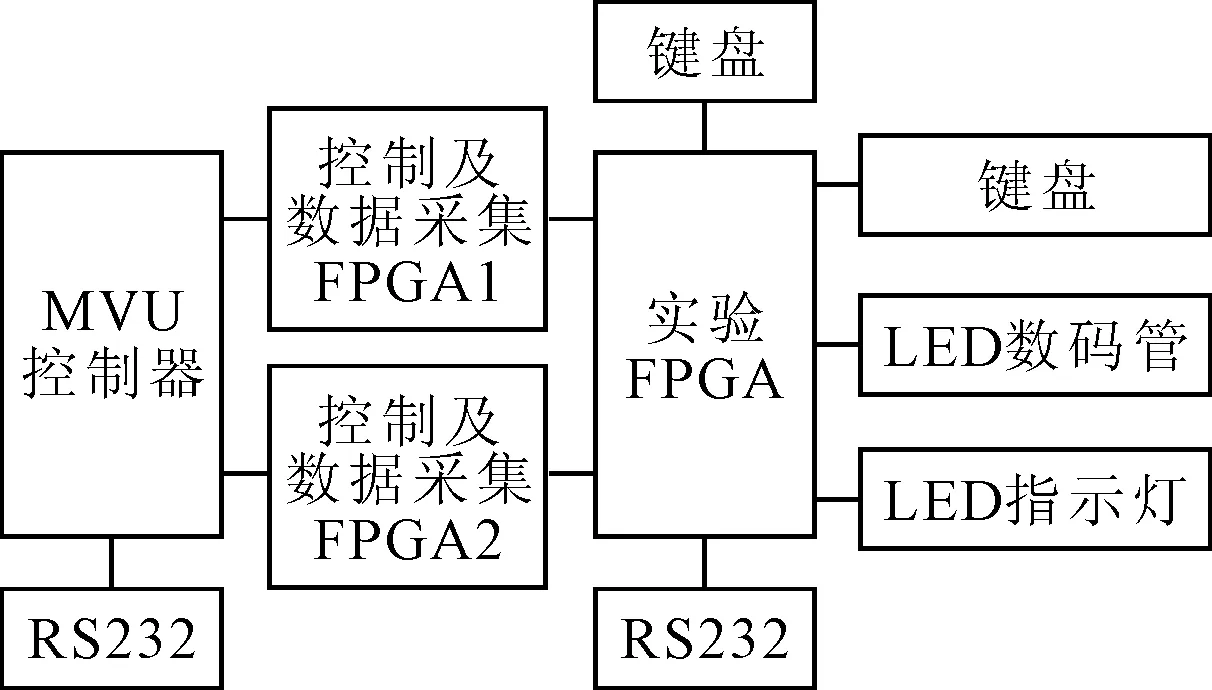

2 实验仪器的设计

整个硬件实验仪的核心板包含两片FPGA,其中一片FPGA上实现MCU与通信控制器连接;通信控制器再通过以太网与服务器主机相联,实现“互联网+FPGA”远程计算机硬件实验系统,可以远程在线进行数字逻辑电路、计算机组成原理和计算机体系结构一系列核心课程的实验[18-20]。配合其他实验板,可以开设微机原理、嵌入式系统、操作系统、编译原理、软硬件协同设计等课程。

控制及数据采集FPGA采用Xilinx Sparten6,实验FPGA采用高速、高容量的XC7K325T,外接64位宽的静态存储器,高速数字视频接口,用于数字逻辑、计算机组成、计算体系结构课程的配套实验。Kintex FPGA提供了更大的容量、更高的性能以及比Virtex-5更多的资源:包含50950个逻辑片,每个逻辑片含有4个6输入的查找表和8个触发器;多达16兆位的高速块RAM;10个时钟管理单元,每个都含有锁相环;840个DSP片段;内部时钟最高可超450MHZ;片内模数转换XADC;1800Mbps的32位DDR3接口。

实验板提供了很多接口及外设,包含:USB-UART桥;32个用户开关,8个按钮;OLED接口;VGA接口;XADC连接端;HDMI接口;10/100/1000以太网物理接口;USB2.0 Host/Device/OTG物理接口;Micro SD卡接口;3.5mm音频接口;串行flash; USB键盘和USB鼠标接口。可以选择从U盘、microSD、板上flash引导。含32个输出LED及8位数码管,用于显示输出的状态及运算结果。根据不同的配置,高速缓存可以用片内块RAM,也可以用片外的静态RAM;主存用DDR3同步动态RAM,虚存用microSD卡或者U盘;或者高速缓存用片内块RAM,主存用片外SRAM,因为SRAM相对比较容易配置。 XC7K325T的容量足够实现32位五级流水线,带高速缓存及存储器管理的MIPS处理器[9-10]。A/D转换模块可以输入模拟量,增加了外设的能力,除此之外,输出数据可以通过UART口接PC机的控制台,通过超级终端与实验CPU进行数据交互,完成比较复杂的程序,而不是简单的LED指示。满足了数字逻辑、计算机组成和计算机体系结构三门课的实验。

图3 计算机硬件系统一体化实验仪核心板框图

3 结语

对计算机专业硬件类课程按系统观的要求进行整合,根据不同知识点在计算机系统抽象层次上的位置,结合ACM CS2013规范,重新设计了数字逻辑的课程及实验内容,并采用硬件描述语言来描述数字逻辑电路与计算机部件,并且根据课程内容的要求,重新设计了计算机硬件系统一体化实验仪,目前已用于数字逻辑实验、计算机组成实验,以及计算机体系结构实验。经过这几年的实践,取得了良好的教学效果。下一步,将实验仪连上互联网,实现远程实验,供学生课余时间使用。在实验内容上,按照ACM CS2013规范,把单周期CPU的设计引入数字逻辑电路实验。