X波段SICL小型化带通滤波器的设计

唐瑞瑞,黄玉兰,唐 磊

(西安邮电大学 电子工程学院,陕西 西安 710121)

0 引言

随着无线通信技术的普及,现代滤波器需要满足小型化、高集成度、低成本等要求[1-3]。基片集成波导(SIW)具有尺寸小[4],品质因数(Q)值高[5],损耗低和易于集成的特点[6-7]。电子科技大学已将SIW应用于K波段的滤波器中,其中心频率可以达到19.75 GHz[8],针对Wi-Fi设计的SIW型带通滤波器回波损耗可达-34 dB[9]。但由于SIW的尺寸不能随意缩小,造成SIW在较低频段尺寸较大[10]。因此,一种具有屏蔽的、非色散特性结构的基片集成同轴线(SICL)结构应运而生[11]。和SIW相比,SICL在保持高性能屏蔽结构优点的基础上,设计尺寸更灵活,同时又可用简单且廉价的印制电路板(PCB)、CMOS、微机电系统(MEMS)甚至薄膜电路等工艺实现,易与有源器件系统进行集成[12-13]。目前,已运用SICL结构研究出滤波器、功分器及耦合器等多种微波器件。东南大学微波实验室提出一种以中心频率2.2 GHz的SICL技术的小型表面挂载滤波器[14]。电子科技大学设计出了一种新型的基于SIW和SICL复合结构的双带带通滤波器[15]。Mathieu Cariou等在SICL技术的研究上,利用8层金属化组成的多层PCB设计和制造了一种三阶的X波段滤波器[16-17],但由于SICL器件的物理结构,测试要求使用夹具进行,则测试结果受夹具精度的影响较大[18]。

本文针对SIW滤波器尺寸过大和SICL的使用夹具测试引起的损耗问题,主要分析了阶跃阻抗(SIR)型SICL谐振器的设计原理和方法,提出了利用共面波导(CPW)向SICL谐振器提供激励的方法,利用电耦合方式,设计了一种X波段带通滤波器,滤波器阶数仅为三阶。利用SIR结构有效地增加了带宽,获得了较低插损和较小尺寸。

1 SIR型SICL谐振器设计

1.1 SIR型SICL谐振器的原理

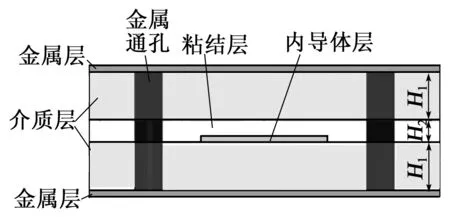

如图1所示,SICL是一种屏蔽平面同轴传输线,由2层介电质层、3层金属层及2排金属通孔构成。图中,H1为介质层厚度,H2为粘结层厚度。SICL主要类似于一个矩形的同轴线,它保留了与平面电路相结合的优点和进一步的兼容。本文的介质板材选用Taconic公司的多层PCB板,介质材料的相对介电常数为2.2,介质损耗角为0.000 9,厚为0.254 mm;粘结层相对介电常数为3.0,介质损耗角为0.003 8,厚为0.12 mm;敷铜厚为0.036 mm。

图1 SICL结构模型

SIR型谐振器是由2个及2个以上具有不同特性阻抗的传输线,通过阻抗阶跃结合面组合而成的横向电磁场或准横向电磁场模式的谐振器。SIR谐振器的开路端和短路端具有电容效应,可达到减小滤波器尺寸的目的。此外,SIR滤波器还可控制滤波器的寄生通带。通过控制谐振器的阻抗比来控制谐振频率,结合SIR设计出SICL型谐振器如图2所示。图中,p、d分别为相邻金属通孔间距和金属通孔直径,A为两排金属通孔距离,代表SICL结构的外导体直径,w1、w2分别为SICL内导体直径,L1、L2分别为SIR结构中的短路端及开路端传输线的长度。谐振阻抗比为

(1)

式中:Rz为SIR结构2个特性阻抗之比;Z1、Z2分别为短路端及开路端阻抗。

图2 SIR型SICL谐振器

1.2 谐振器激励的引进

为了解决用夹具测量SICL器件引起的滤波器损耗问题,设计引进了谐振器激励。SICL由很多周期的金属化通孔构成,外加SICL集成于介质基片上,由于大多测试要使用夹具进行,使测试结果受夹具精度的影响较大。又因CPW可传输准横电磁波(TEM),与SICL传输模式相同,因此,本文设计一种用CPW结构引进谐振器的激励,其结构如图3所示。图中,w3为CPW中心导带宽度加上2个缝隙的总距离。盲孔是由上层介质上表面至粘结层下表面处,盲孔内均填铜,目的是使SICL的内导体与CPW结构相连。根据谐振腔内部结构,选择抽头式馈电,抽头外接CPW结构,由CPW结构连接平面电路。

图3 SICL谐振器的激励引进结构图

1.3 激励引进结构数据分析

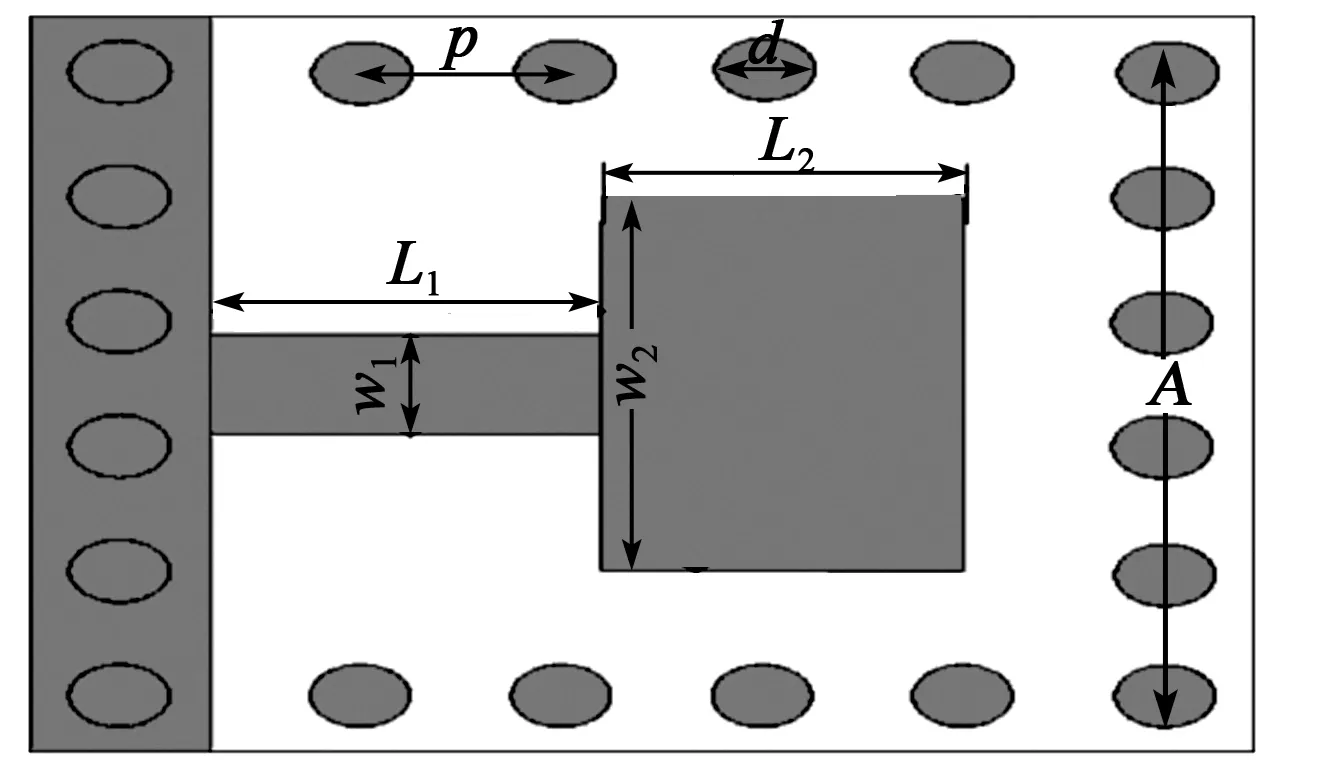

谐振器外接CPW结构阻值为50 Ω,CPW与抽头的连接部分会造成信号的衰减,从而影响谐振器的性能。因此,我们改变CPW的盲孔直径d1,得到d1和谐振器反射系数S11的关系曲线,如图4所示。通过调节抽头与接地端的距离S1可控制外接Q滤波器群时延的大小,群时延与S1的关系曲线如图5所示。

图4 S11与d1仿真曲线

图5 S11群时延与S1仿真曲线

根据图4、5可看出:

1) 随着d1的增大,反射系数S11相应减小。d1越大,信号传输性能越好,表现出谐振通带衰减越小,通带内反射系数的衰减越大。

2) 随着d1的增大,谐振频率随之增大。d1的大小影响谐振器中的电磁场模式,随之反映出谐振频率的变化。

3) 当S1变大时,群时延变大,群时延又与外界品质因数正相关,即抽头越接近接地端,外界品质因数越大。

4) 当S1变大时,谐振频率会相应减小,反之也成立。这说明滤波器内部抽头会影响其谐振频率,滤波器的频率会降低。

因此,设计滤波器时,应配合相应的盲孔直径和抽头与接地端的距离,适当调节连接CPW结构谐振器的谐振频率,防止因盲孔和抽头与接地端距离而导致频率误差。

2 滤波器的耦合及优化仿真

2.1 谐振器的耦合

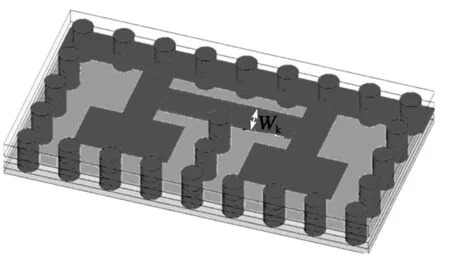

本文通过组合3个SICL型谐振器,应用耦合系数法设计了中心频率为10 GHz,带宽1.5 GHz的滤波器。使用HFSS仿真谐振器间的耦合系数,双谐振器的耦合方式如图6所示,耦合系数大小通过耦合线的宽度Wk来调节。

图6 耦合系数仿真模型

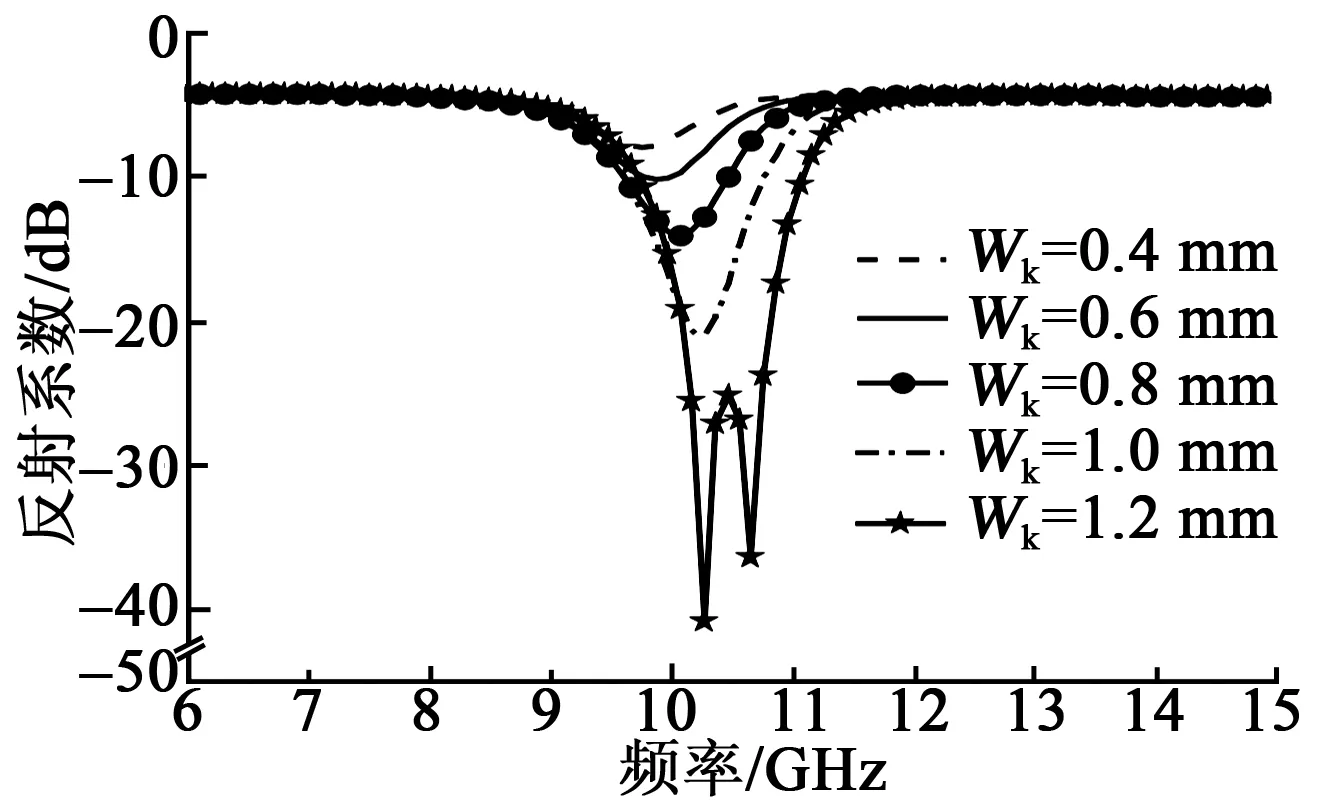

图7为耦合系数k随Wk变化的曲线。由图可看出,随着Wk的增大,耦合系数相继增大,且k>0.08,为强耦合。Wk的增大不仅改变了耦合系数,也相应地改变了滤波器的反射系数,图8为反射系数随Wk的变化曲线。由图可看出,当Wk增大时,反射系数、谐振带宽随之减小,滤波器的中心频率变大。

图7 耦合系数随Wk的变化曲线

图8 反射系数随Wk的变化曲线

2.2 滤波器仿真结果

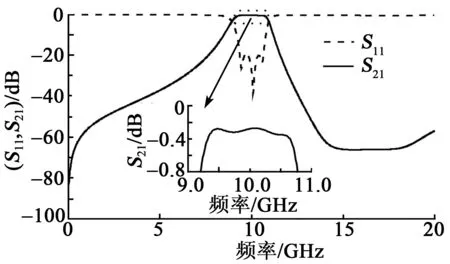

图9为三阶带通滤波器的结构。使用HFSS软件进行优化仿真,确定得到尺寸的最终值,如表1所示。

图9 SICL型滤波器结构图

Sk/mmWk/mmL1/mmL2/mm10.62.41.3S1/mmw1/mmw2/mmWt1/mm10.232.730.2

SICL型滤波器占用空间为13 mm×7 mm,标准化体积为0.43λ0×0.023λ0(λ0为中心频率在自由空间中的波长),得到的曲线如图10所示。

图10 SICL型滤波器仿真曲线图

由图10可看出,SICL型滤波器的中心频率为10 GHz,在通带9.25~10.75 GHz内,最小插入损耗为0.8 dB,其中包括CPW结构引起的损耗,回波损耗大于19.5 dB。

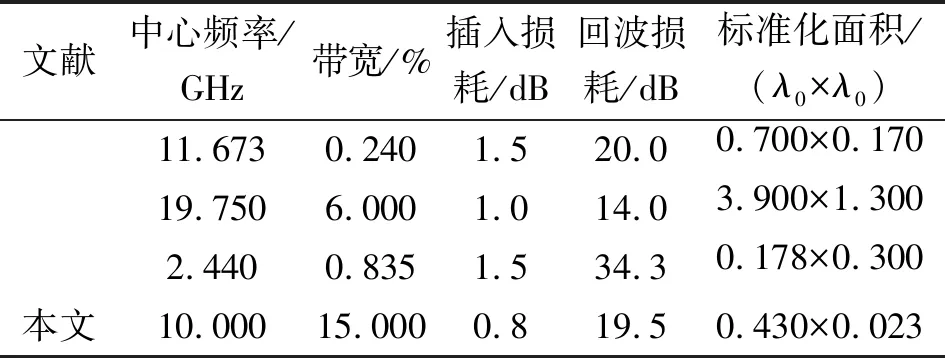

2.3 滤波器性能对比

为突出SICL结构的性能,将SICL滤波器与现今的主流结构SIW型滤波器进行对比分析,表2为SICL滤波器与SIW型滤波器的参数比较。

表2 SICL结构与SIW结构滤波器的参数比较

由表2可看出,与文献[7-9]中SIW滤波器相比,本文SICL滤波器的插入损耗较高,带宽宽,且标准体积较小。SIR结构的加入,使谐振器的带宽加宽,标准体积的改善是由于SICL谐振器的宽度尺寸由内、外导体比值确定。与文献[8]相比,由于SIW谐振器的窄带宽,造成其所设计滤波器的谐振器数量增大,则尺寸相应增大。文献[9]是低频波段SIW的应用。由表2还可看出,若SIW滤波器面积小,同时带宽会更小,验证了SIW更适合窄带滤波器的设计,SICL型滤波器适合宽带滤波器。

3 结束语

本文研究了SICL谐振器的性能,设计了中心频率为10 GHz、带宽15%的滤波器。提出由CPW引进激励于SICL谐振器的方式,激励引进结构中的盲孔直径会影响谐振器的本征频率和传输性能。滤波器面积为13 mm×6 mm的谐振器,可与小型螺纹连接的同轴连接器 (SMA)接口直接连接。与SIW谐振器相比,SICL结构尺寸缩小,且还可进一步缩小。由此可得,SICL滤波器的面积可达0.43λ0×0.023λ0,损耗仅有0.8 dB。与SIW结构相比,SICL结构损耗低且便于集成。本设计为SICL结构在微波领域的发展提供了一定的参考价值。