合理运用SI技术快速收敛高速数字电路设计

贾明福,宋舒雯,王 宁,袁 寰

(北京自动化控制设备研究所,北京 100074)

0 引言

近年来,随着半导体工艺技术的迅猛发展,晶体管的体积越来越小,芯片的集成度越来越高,单位芯片内的晶体管数量逐渐增加,数字电路系统朝着高密度和低成本的趋势不断发展[1]。与此同时,板级电路信号速度不断提升,串扰、反射、振铃等信号完整性问题日益突出[2]。

作为典型的数字电路,惯性捷联导航系统的数字时钟速率也不断提升,由此带来的信号完整性问题已不容忽视。随着捷联惯性技术的不断发展和成熟,惯性导航系统正向着更宽更广的领域发展,如智能炸弹、水下无人制导系统及车载导航等[3-7]。应用领域的拓展和工作速率的提升使得产品的功能性要求和可靠性要求越来越高。各功能电路信号完整性的好坏将直接影响整个惯导系统的可靠性。

在高速数字电路中,若信号完整性问题不能够得到及时解决,将会直接导致信号失真、时序紊乱等,从而造成系统误工作甚至系统崩溃[8]。传统的经验设计已无法满足现代半导体产业高速、低电压的技术路线,在电路设计中加入信号完整性仿真成为保证产品可靠性的必需环节[9]。

本文以惯性捷联导航系统为例,针对传统经验设计下的某导航计算机SDRAM时钟信号异常问题进行了信号完整性仿真与分析,通过对SDRAM时钟信号传输路径进行合理的端接设计,得到了符合时序要求的时钟波形。仿真和实验结果表明,将信号完整性仿真融入高速数字电路设计中,有利于指导设计,提高电路可靠性,提前规避风险。

1 系统简介

嵌入式导航计算机作为捷联式惯性导航系统的核心设备,主要分为两部分功能电路,分别是信息预处理部分和导航计算部分。其中信息预处理部分主要完成惯性信息的采集及预处理等功能;导航计算部分主要完成惯导系统导航解算以及与外部设备的信息传递[10]。

导航计算机硬件电路主要由电源、时钟、处理器、存储器和外围设备组成。其功能电路结构示意图如图1所示。处理器系统由DSP扩展外部程序存储器FLASH和数据存储器SDRAM组成。

图1 导航计算机功能电路结构示意图Fig.1 Schematic diagram of circuit structure for navigation computer

2 信号完整性概念

信号完整性可以泛指信号的电压、电流在互连结构传输中的信号质量问题,包括噪声、干扰以及由其造成的时序影响等[11]。信号完整性需要保证信号的质量,即要保证信号在驱动端、互连结构上,特别是接收端上的特性,避免产生功能性和稳定性方面的问题[12]。

从传统意义上的数字波形来看,信号质量主要从过冲、振铃、边沿单调性等几个方面进行评判[13-14]。具体定义如下:

1)过冲包括上过冲(Overshoot_High)和下过冲(Overshoot_Low)[15]。上过冲是信号高于信号供电电源电压Vcc的最高电压,下过冲是信号低于参考地电压Vss的最低电压。过大的过冲会导致信号误触发、损坏芯片或者影响其使用寿命。

2)振铃(Ringing)是信号跳变之后的振荡。振铃会使信号的噪声容限减小,过大会造成逻辑错误,而且会使信号的高频分量增加,加剧电磁干扰(Electromagnetic Interference, EMI)问题[16]。

3)边沿单调性(Monotonicity)是指信号上升或下降沿的回沟。对于边沿判决的时钟信号,波形边沿在翻转门限电平处的非单调性可能造成逻辑判断错误[17]。

除此之外,广义的信号质量还包括所有可能引起信号接收、时序、工作稳定性或者电磁干扰方面的不正常现象[18]。因此,在进行数字电路设计时,要合理地运用信号完整性技术手段,反复验证,不断优化,以保证信号的传输质量。

3 信号完整性仿真分析

3.1 信号完整性问题定位

在某惯导系统研制过程中,采用传统经验设计方法设计了一款导航计算机。在系统进行测试的过程中发现处理器通电自检时报用户区程序CRC校验错误,未完成通电加载。连接仿真器对FLASH区及SDRAM区进行测试,多次测试FLASH区并未发现错误,但对SDRAM区进行测试时,出现读出和写入数据不相符的情况,所以此次故障发生的原因为处理器访问SDRAM异常。

SDRAM各信号包括时钟信号、复位信号、读写控制信号、地址总线信号以及数据总线信号。使用实验室最高带宽的示波器(2GHz采样率/500MHz带宽)对上述信号进行测量,波形未见异常,但在测量ECLKOUT信号时SDRAM访问故障消失,说明ECLKOUT信号完整性可能存在问题,但现有仪器无法准确测量。用仿真软件对SDRAM各信号进行信号完整性仿真扫描,除时钟信号网络ECLKOUT外其余信号波形均未发现异常。ECLKOUT仿真波形如图2所示。

图2 ECLKOUT信号仿真结果Fig.2 Simulation result of ECLKOUT signal

由图2可以看出,在时钟信号的上升边和下降沿出现了非单调性问题。对于时钟沿采样的信号,如果存在非单调性,就可能引起器件的时序错误,进而导致功能错误,如采样延迟或者在周期内无法完成采样、出现误触发而产生误码等。

借用安捷伦开放实验室高带宽有源探头示波器测得SDRAM时钟输入管脚处信号波形如图3所示。

图3 装配22Ω端接电阻ECLKOUT信号测量波形Fig.3 Measurement waveform of ECLKOUT signal with 22Ω resistance

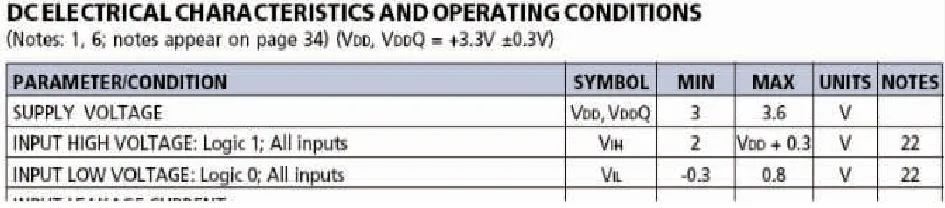

从图2和图3中可以看出,信号的仿真结果与实测结果基本一致,ECLKOUT信号上升沿在1.82V附近存在不单调现象,下降沿在1.31V附近存在不单调现象。图4所示的SDRAM数据手册要求高电平判决门限VIH为2V,低电平判决门限VIL为0.8V,即0.8~2V为信号判决门限的未定态区间。

图4 SDRAM直流电气特性Fig.4 DC electrical characteristics of SDRAM

若时钟信号ECLKOUT在未定态区间存在不单调现象,会引起器件采集时钟信号错误,导致器件读写时序错误或者造成器件内部状态机工作错误。这样会造成处理器访问SDRAM错误,导致处理器加载异常。

3.2 改进措施

一般来说,在电路板投产前可以通过引入信号完整性仿真,从阻抗匹配、更改PCB走线、改变端接拓扑结构等方面改善信号完整性。但在该导航计算机产品已投产,PCB走线已确定的情况下,最好不改变走线的拓扑结构,选择在已有设计的基础上通过信号完整性仿真优化改变端接电阻的方式进行调整。

该导航计算机时钟信号ECLKOUT的拓扑结构如图5所示。在原版设计中,ECLKOUT信号经过22Ω的串行端接电阻后,驱动SDRAM和FPGA这2个串行负载。其中端接电阻R1后端到SDRAM的走线长度为31.4706mm,SDRAM到FPGA之间的走线长度为90.805mm。

图5 ECLKOUT信号拓扑结构图Fig.5 Topology diagram of ECLKOUT signal

根据图5拓扑结构及走线长度在仿真软件中建立仿真模型,如图6所示。

图6 ECLKOUT信号仿真模型Fig.6 Simulation model of ECLKOUT signal

对该模型中R1进行参数扫描,选取起始值为0Ω,考虑到阻抗匹配,终值选取50Ω,步进为4。启动扫描仿真得到ECLKOUT波形如图7所示。

图7 0~50Ω端接电阻ECLKOUT信号扫描仿真波形Fig.7 Simulation waveform of ECLKOUT signal with 0~50Ω resistance

从图7可以看出,改变R1阻值上升沿和下降沿不单调现象依然存在,而且阻值越小不单调的重叠区域和过冲越大;但随着阻值的减小,上升沿非单调性的位置不断上升,下降沿非单调性的位置不断下降。从边沿采样的角度来说,非单调性偏离2V和0.8V的位置越远越好,查询SDRAM数据手册,考虑过冲阈值的前提下,选取0Ω端接电阻非单调性位置偏离未定态最远,满足SDRAM数据手册参数要求。

用高带宽示波器测量得到实际串联0Ω端接电阻下的时钟信号波形如图8所示。

由图8可知,当端接电阻阻值改为0Ω时,信号上升沿不单调区间发生在2.53V附近,信号下降沿不单调区间发生在0.6V附近,与仿真波形一致。在0.8~2.0V的未定态区间不存在信号上升沿或者下降沿不单调的情况,可以避免时钟信号电平误判。

为了验证仿真模型的正确性,将端接电阻R1改为16Ω和33Ω,测量得到ECLKOUT管脚信号波形如图9、图10所示。

图8 装配0Ω端接电阻时ECLKOUT信号Fig.8 Measurement waveform of ECLKOUT signal with 0Ω resistance

图9 装配16Ω端接电阻时ECLKOUT信号Fig.9 Measurement waveform of ECLKOUT signal with 16Ω resistance

图10 装配33Ω端接电阻时ECLKOUT信号Fig.10 Measurement waveform of ECLKOUT signal with 33Ω resistance

测量结果同样显示,信号上升沿不单调的位置随着端接电阻阻值的变小而逐步提高,将端接电阻换成0Ω后非单调性的位置最高,改成16Ω和33Ω时过冲较小,但非单调性的位置较低。将产品中端接电阻由22Ω更改为0Ω,单板进行-40℃~70℃范围内的变温试验验证,温度变化速率为不大于2℃/min。温度变化过程中,连接仿真器,配置DSP参数后,加载SDRAM测试程序,对SDRAM每个地址分别写入0x5555、0xAAAA和0~0xFFFF递加三种数据。然后对读出和写入数据进行比较,测试过程中读出写入数据次数大于1×108次,未发现读出写入数据不符的情况。

由上述分析和测试可知,去除R1端接电阻,ECLKOUT信号完整性能够满足器件要求。但值得注意的是,去除R1端接电阻,虽然使得信号非单调性处的电压不处于未定态区间,但端接电阻过小会使得信号的过冲加大,过大的过冲可能导致芯片损坏或者影响芯片的使用寿命。此时要将过冲控制在相应的总线规范和芯片数据手册中规定的限定值内,在后续设计中应在PCB投产之前进行阻抗匹配和拓扑结构等方面的综合设计,完成信号完整性仿真,以确定最优的设计方案和参数。

4 结论

本文以某导航计算机为例,运用信号完整性分析技术分析了传统经验设计下端接电阻阻值匹配不当引起的边沿非单调性问题。通过对导航计算机电路板进行信号完整性分析和测试,得到如下结论:1)端接电阻阻值选取不当会引起SDRAM的时钟信号的非单调性问题,造成数据读取异常;2)进行信号完整性仿真有助于在既定PCB布局下快速选取保证数据正常读取的最佳端接电阻阻值;3)仿真和实验结果表明,在正常的高速数字电路研制流程中,加入信号完整性仿真可以在不进行投产的情况下遍历所有取值情况,可以提前规避风险,有效缩短高速电路研制周期,降低研制成本。