存储式弹载数据记录仪存储可靠性技术研究

朱金瑞,王代华,苏尚恩,王晓楠

(1.中北大学仪器科学与动态测试教育部重点实验室, 太原 030051; 2.中北大学电子测试技术国家重点实验室, 太原 030051; 3.北方导航控制技术股份有限公司, 北京 100176)

导弹从飞行到落地整个过程中,弹载数据采集系统对其内部各类参数信号进行采集分析,能够判定飞行状态是否正常,评定其性能指标。因此,数据采集系统的研究在导弹研制过程中具有重要的作用。弹载数据记录仪是为实现对导弹飞行过程中各通道数据的采集存储,并在试验结束后能够进行准确回收而研制的一种多通道数据采集系统[1-3]。按照存储介质的种类,可分为磁带式与固态式存储系统,其中,磁带式数据存储系统是以磁带录音技术为基础,利用磁性材料上的剩磁效应将被测信号存储下来,但因其采用大量机械元件,致使体积、功耗都比较大,且磁带式数据存储系统在读数时仅支持顺序寻址,读数过程耗时长,为数据读取带来很大的困扰[4]。相对于磁带存储系统,固态式存储系统以半导体介质为基础。半导体存储介质内部以半导体电路为基础,具备微体积、存储速率高以及操作简单的优点。常用元件有SRAM、DRAM、SDRAM、EPROM、EEPROM以及Flash等,其中Flash存储芯片具有掉电不丢失、微体积、低功耗的优点[5-6]。

本文选用NAND Flash存储器,以FPGA为主控芯片,设计实现对弹上16路模拟信号和8路数字信号采集存储的弹载多通道数据记录仪。针对导弹飞行过程中强冲击、高过载的恶劣工作环境,重点开展了NAND Flash的无效块管理和ECC校验可靠性存储技术的研究。

1 系统指标及存储逻辑设计

系统主要完成对弹上各类型传感器模拟信号、数字接口信号的采集存储,在飞行结束后,通过以太网接口对数据进行回读并分析。根据研制任务的要求,系统主要完成对以下各通道信号的采集存储:

1) 模拟通道参数:4路5 V输入电压,采样率为1 kHz;4路32 V输入电压,采样率为10 kHz;4路±5 V输入电压,采样率为1 kHz,采样精度优于±1%;

2) 数字通道参数:8路RS422通道,其中4路波特率为115 200 b/s、4路波特率为230 400 b/s。

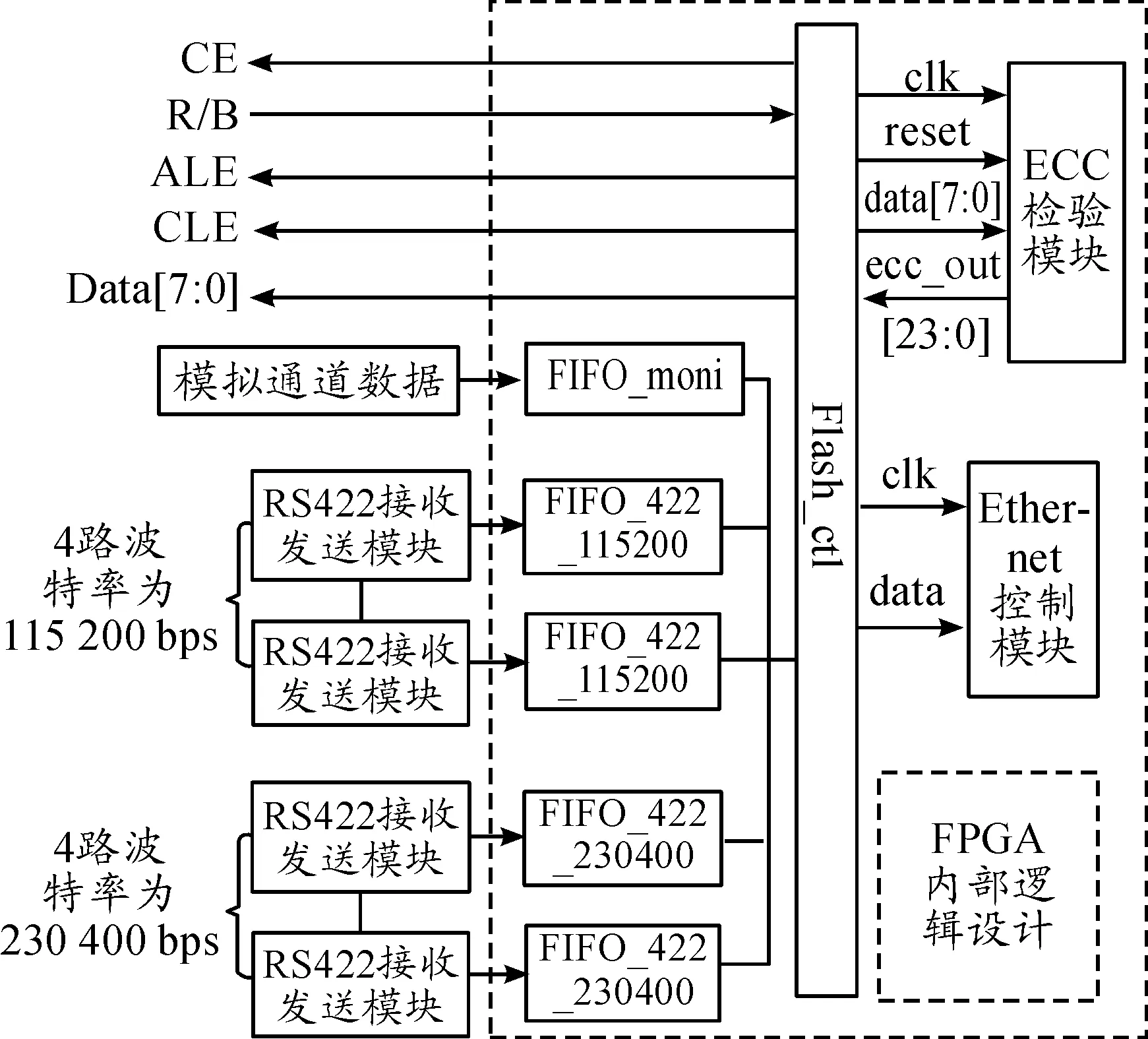

系统由Xilinx公司Spartan-6系列的FPGA编程实现对NAND Flash芯片的时序控制,进而完成对模拟通道、RS-422数字通道采样后数据的可靠存储。基于FPGA的数据存储模块的逻辑设计如图1所示。

图1 系统存储模块FPGA逻辑设计

Flash_ctl模块用于产生控制NAND Flash的CE、R/B、WE、RE、ALE、CLE等信号;在数据存储状态下,接收外部所有通道的采集数据;在上位机读数状态下,读取芯片内部数据,并发送至Ethernet控制器。Flash前端的FIFO模块除在数字通道数据的基础上加入帧头、帧尾等识别字节的功能之外,主要用于缓存数据,以匹配模拟通道、RS-422数字通道的数据输出、Flash的写操作三者间的速率,确保数据在Flash页编程中不丢失。ECC校验模块对采集到的数据生成ECC校验码,以提高数据存储的准确性。Ethernet控制模块实现介质访问层(MAC)的功能,对数据编码封装,实现与物理层(PHY)芯片的数据和指令的传输。

2 存储可靠性关键技术

2.1 无效块管理

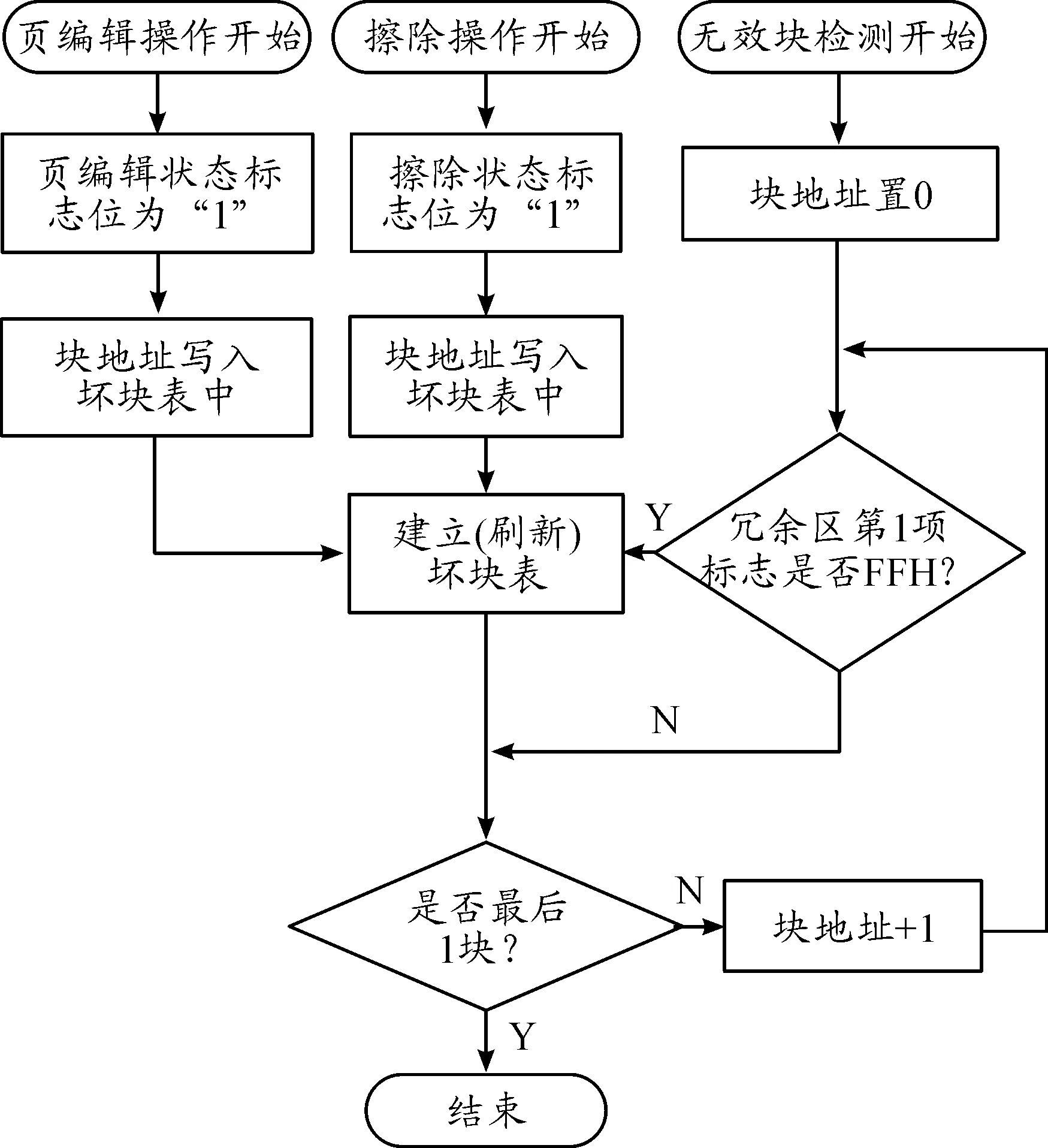

NAND Flash的芯片工艺导致其生产和使用期间会产生无效块,故无效块的管理一直是NAND Flash管理的关键和难点[7-9]。传统无效块管理方法是将无效块列表存放至NAND Flash的第一块中,虽然Flash在出厂时保证第一块是完好的,但超过一定的次数,该块也可能会变成无效块,降低了无效块列表存储的可靠性。本设计中,将无效块列表存储至FPGA内部RAM中。由于该Flash芯片共有1 024块,块地址为10位,则在FPGA内部分配一个2 kB的缓存即可满足无效块表的容量。当进行存储操作时,FPGA首先对要存储的地址和无效块列表中的地址进行对比,之后将数据存储到好块中;当数据进行读取操作时,同样由FPGA依据无效块列表中得出的好块地址读取数据。无效块表的建立和更新流程如图2所示。

图2 无效块检测流程

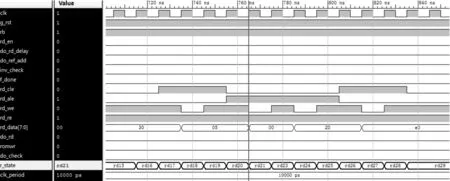

系统每次上电工作后,首先由FPGA访问NAND Flash,无效块检测仿真如图3所示,由随机读命令(05H、E0h)读取无效块标志位,若输出数据为“00h”,则表明该块为无效块,之后将相应地址写入无效块表中。无效块管理的设计实现了存储地址的透明化,使NAND Flash的存储区域的逻辑地址仍然能进行连续读写。

图3 无效块检测仿真时序图

2.2 ECC校验

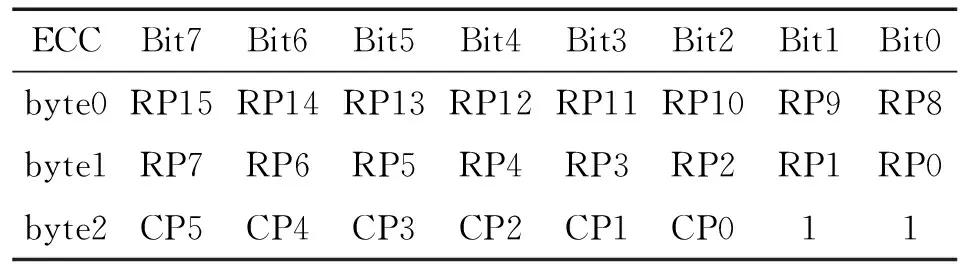

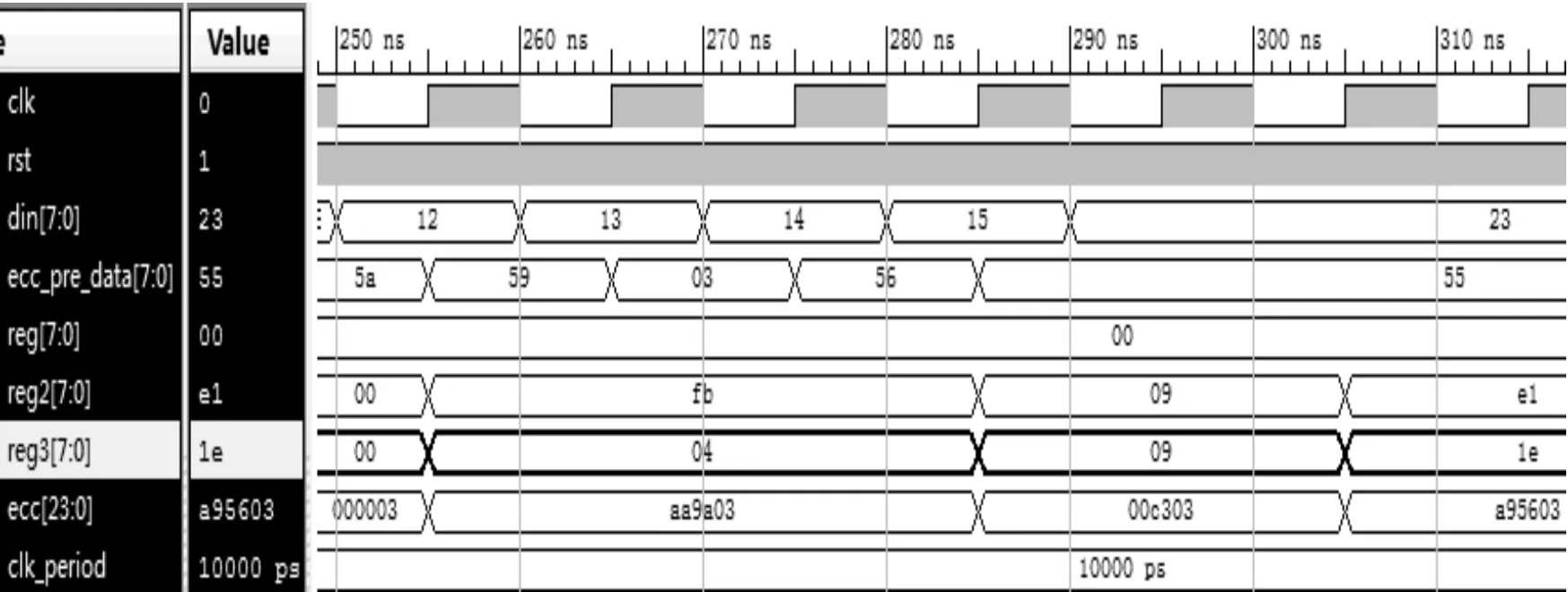

NAND Flash的结构特点导致数据存储过程中可能存在误码,ECC(Error Correcting Code)作为一种数据检错纠正算法,通过增加冗余数据对存储于NAND Flash中的数据进行编码,是NAND Flash在使用时确保数据准确存储的一项关键技术[10-12]。本文设计了一种基于汉明码高性能ECC校验方法,采用FPGA实现并应用于NAND Flash存储逻辑设计中。每256 byte原始数据通过计算得到6 bit列校验码、16 bit行校验码,共22 bit,存放于NAND Flash的冗余区,存放格式如表1所示。为加快FPGA的计算速度,实现逻辑中事先计算好256个数的各自的列校验码,并存储至FPGA内部。此方法是以牺牲FPGA内部逻辑单元来换取处理速度,利用查找表找出行校验码和列校验码。该表以字节数做下标,采用FPGA编程计算并存储0~255个字节的行校验码和列校验码。查找表中的每个字节的各bit位的含义如表2所示,各字节校验的仿真结果如图4所示。

表1 ECC校验码存放格式

表2 查找表中各Bit位对应的内容

1) 列校验码的计算

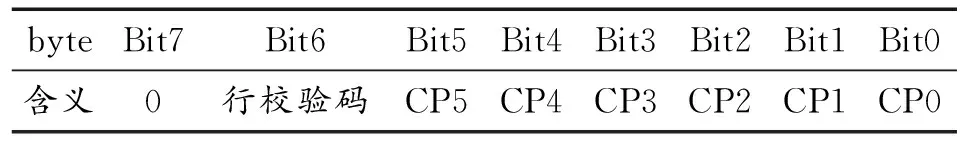

校验256字节的数据则相应地进行256次查表,通过索引各字节校验值的查找表,得到ECC索引表的值ecc_pre_data,取出相应的列校验值ecc_pre_col,与上字节的列校验值reg1异或运算,由此得到256 byte数据的列校验值。仿真结果如图5所示。关键代码如下:

ecc_pre_col<=ecc_pre_data and 0x3F;

reg1<=reg xor ecc_pre_col;

reg<=reg1;

图5 列校验码仿真计算

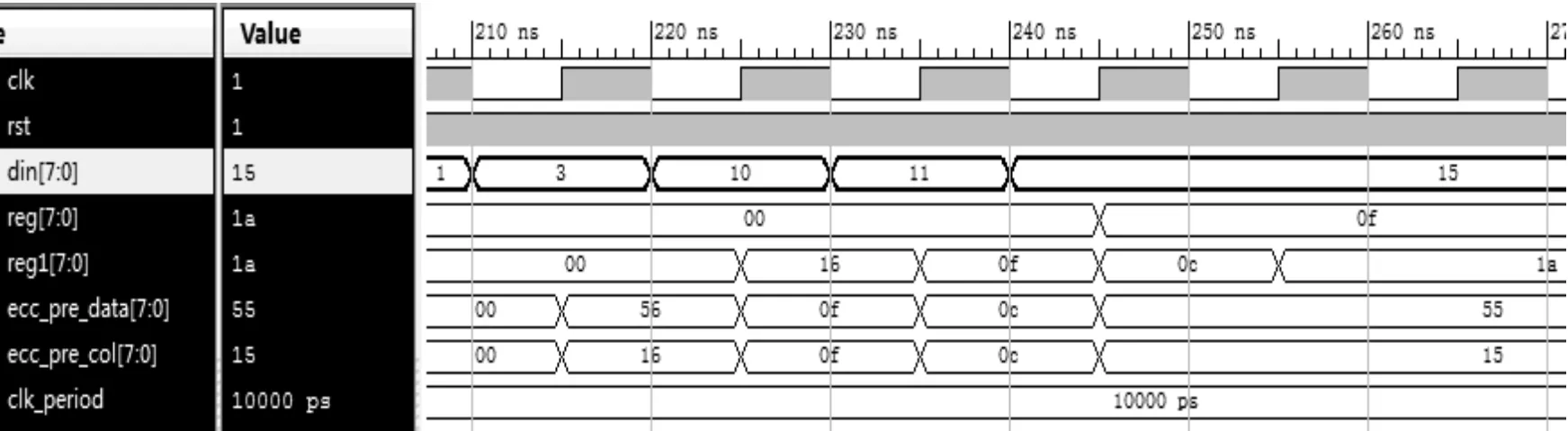

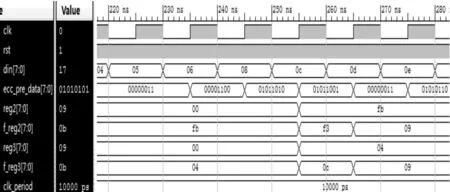

2) 行校验码的计算

由表2可知,ECC索引表中第6位存放每个字节的行校验码,对输入数据依次索引查表,若ECC校验值的bit6=1,则表示该字节的行校验为1。根据行校验原理,RP0只计算bit0=0的字节,RP1计算bit0=1的字节,RP2计算bit1=0的字节,RP3计算bit1=0的字节,以此类推。因此,将全部行校验为1的输入数据按位异或,得到的结果保存在reg3中,reg3的bit0、bit1…bit7则分别得出RP1、RP3、RP5…RP13计算范围内行的数量。相应的寄存器reg2的值表示属于RP0、RP2、RP4…RP14计算范围内行的数量。行校验码仿真结果如图6所示。实现代码如下:

if(ecc_pre_data(6)=’1’)then

reg3<=reg3 xor data;

reg2<=reg2 xor (not data);

end if;

256 byte数据全部计算完成后,按表1的格式排序,即可得到最终的ECC校验码。ECC校验码仿真结果如图7所示。

图6 行校验码仿真计算

图7 ECC校验码仿真计算

3) ECC纠错

原ECC校验码与读出数据计算出的ECC校验码进行按位异或,若结果为0,表示读数过程中不存在错误;若结果中11 bit为‘1’,表示有1 bit数据传输错误,并可纠正;其它结果表示传输出错且错误无法纠正。由列校验生成规则可知,若256字节中有1 bit数据出现错误,则列校验结果中3 bit的数据发生翻转,同理,行校验结果中有11 bit数据翻转。

查找出错位的方法是:首先依据行校验码确定哪个字节出现错误,然后依据该字节的列校验值确定哪个bit位出现错误。以列地址为例,根据列校验值与各bit位之间的关系,若新旧ECC校验码异或后,CP5为1,则表明错误发生在该字节的高4位,反之,低4位出现错误;在检测出的4位中,若CP3为1,错误位置定位在高2位;如此依次检测,即可确定列地址。同理,通过检测行校验值异或结果中的RP15、RP13、RP11、RP9、RP7、RP5、RP3、RP1位,即可判断出具体的字节位置,从而找出错误比特位的具体位置。实现代码如下:

ECC_old_even<=RP14&RP12&RP10&RP8

&RP6&RP4&RP2&RP0&CP4&CP2&CP0;

ECC_old_odd<= RP15&RP13&RP11&RP9

&RP7&RP5&RP3&RP1&CP5&CP3&CP1;

ECC_new_even<= RP14&RP12&RP10&RP8

&RP6&RP4&RP2&RP0&CP4&CP2&CP0;

ECC_new_odd <= RP15&RP13&RP11&RP9

&RP7&RP5&RP3&RP1&CP5&CP3&CP1;

ERROR_location<=ECC_old_odd xor ECC_new

_ odd;

3 存储可靠性功能测试

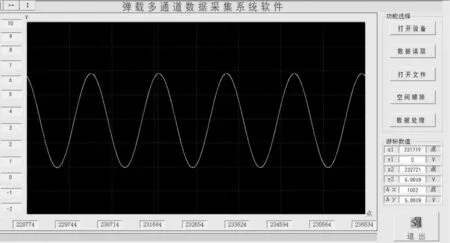

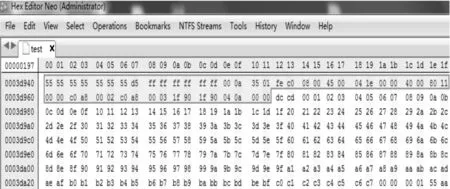

系统设计完成后,从模拟量存储和数字量存储两个方面对系统存储可靠性进行测试分析。首先,在保证各模拟通道中信号调理电路和A/D转换电路达到设计要求的前提下,利用数字信号发生器对一路模拟通道输入峰峰值为5 V、频率为100 Hz的正弦信号,经系统采集存储后通过上位机软件进行显示。图8为上位机读出的该正弦信号的波形。其次在FPGA中编写一段测试代码,生成00H~C7H递增的232 byte的数据,循环写入NAND Flash中,替代模拟通道的每一大帧数据,通过上位机读取显示。写入递增数据的目的是为了清晰方便地检测数据存储和传输过程中有无丢帧误码等现象。利用软件HEX EDITOR打开上位机接收到的数据包,测试结果如图9所示,其中55H~00H为每个数据帧的以太网帧头、IP报文头部以及UDP首部,“DCCD”为每帧数据的帧头,紧接着“0001”为帧计数字节,最后“55AA”为帧尾标志。实验证明,系统可对模拟信号进行精确采集,且经存储模块后可在上位机上显示完整的数字化波形;由数字信号存储过程可看出系统的存储传输性能完好,满足设计指标要求。

图8 频率为100 Hz的正弦波

图9 上位机接收的数据包

4 结论

1) 本文将无效块管理和ECC校验两项存储可靠性技术成功应用于NAND Flash的存储方案中,实现对无效块的有效管理,提高ECC纠错能力,保证了系统数据存储的可靠性和完整性。

2) 通过FPGA仿真分析和存储可靠性功能测试,在对模拟量和数字量的采集存储过程中,能够准确地对原输入信号进行波形还原和数据显示。

3) 本文设计的NAND Flash数据存储可靠性方案,也适用于其他采用NAND Flash的存储式数据采集系统,具有良好的可移植性和实用性。