一种相控阵雷达时序控制装置设计

孙高俊12

(1.中国电子科技集团公司第三十八研究所, 安徽合肥 230088;2.孔径阵列与空间探测安徽省重点实验室, 安徽合肥 230088)

0 引言

相控阵雷达的时间资源和能量资源的管理是相控阵雷达的重要环节。通过波束资源调度,实时编排雷达探测波束和波形,产生全机定时信号和工作时序,实时产生雷达工作参数,能够对重点目标和监视区域分配更多的扫描时间和能量资源,实现对重点目标的快速发现和跟踪[1]。

随着军事斗争的发展,对数字阵列相控阵雷达规模和性能的要求越来越高。例如某相控阵雷达阵元数多,工作模式多,不同的工作模式对资源的调度和时序产生的控制都不相同,波束驻留时间长短差别也较大。为应对此需求,需要研制一种新型的时序控制装置。该装置要求外部接口丰富,具备较强的数据传输和处理能力,并且要具备良好的可测试性。

1 时序控制装置设计1.1 硬件架构设计

为了满足某雷达整机时序产生任务的需求,需要专门研制一种高性能、可扩展的时序控制装置。在工程研制中,结合项目实际需求采用了CPCI (Compact Peripheral Component Interconnect)总线+ FPGA (Field Programmable Gate Array)的系统架构。CPCI总线由于其良好的抗震性和通风性,还可以热插拔,广泛应用于雷达、飞行器等探测领域[2],同时利用FPGA逻辑资源丰富、处理速度快、可在线编程和可灵活配置的特点。

该装置物理形式为基于FPGA的符合CPCI总线标准的专用板卡,硬件架构主要由CPCI总线接口、14路高速差分输入输出通道、2路光电转换接口模块、RS422接口模块、TTL接口模块和RS232接口模块等组成。该装置的原理框图如图1所示。

图1 时序控制装置原理示意图

FPGA用于时序信号的控制和产生、数据交互以及数据格式转换。CPCI总线接口用于实现FPGA与外部CPCI计算机的通信和数据传输。14路高速差分输入输出通道用于实现FPGA与外部处理器之间的数据高速串行交互;光电转换接口模块用于实现FPGA中的数据与外部光纤信号数据的转换及交互;RS422接口模块用于实现RS422信号的输入和输出;TTL接口模块用于实现TTL信号的输入和输出;RS232接口模块用于实现RS232信号的输入和输出。

1.2 详细设计

1.2.1 CPCI总线接口设计

目前CPCI总线接口主要有两种实现方式:使用专用PCI接口芯片和采用可编程器件。专用芯片如PLX公司的PCI9054等可以实现完整的PCI接口功能,可将复杂的PCI总线接口转换为相对简单的用户接口,缺点是缺少灵活性。采用FPGA的优点在于其灵活的可编程性,PCI接口可以依据需求进行优化设计,而不必实现所有的PCI功能[3]。其次将其他用户逻辑与PCI接口逻辑集成在同一个芯片上,可实现紧凑设计。

在本设计中FPGA采用ALTERA公司的StratixⅡGX系列中型号为EP2SGX90FF1508的芯片,器件中等价逻辑单元(LE)有90 960个;片内存储器4.3 Mbit;支持16路高速GTX收发器通道,每路传输速率高达6.375 Gbit/s;接口电平支持:LVTTL,LVDS,PCI等众多I/O标准。EP2SGX系列芯片内部有支持PCI电气特性的区域和管脚,适合于CPCI接口的开发。

CPCI总线接口采用直接调用FPGA自带IP核的方式实现。在FPGA自带IP核的基础上,根据CPCI总线规范协议,添加PCI外围接口逻辑,实现面向用户的接口功能,如I/O端口读写、DMA读写、PCI中断处理等。

1.2.2 时序控制模块设计

时序控制模块是本装置的核心模块,其主要工作流程是接收波束调度计算机通过CPCI总线送来的时序参数和波束调度信息,并据此产生各种不同工作模式下的雷达整机时序信号,并将各种工作参数和波束调度信息通过多种接口形式转发至雷达其他分系统,从而实现雷达时间和能量资源的实时分配,控制各分系统在统一时序下协同工作。

时序控制模块的设计是在FPGA内部完成的,采用硬件描述语言VHDL来实现具体的逻辑功能。在设计中充分采用了参数化的设计思路,时序信号和控制参数全部可实现动态重配置。该模块的设计主要包括以下内容:整机时钟处理、DMA数据接收处理、雷达时统设计、时序产生模块和时序发送模块等,其组成如图2所示。

时序产生的具体实现是根据雷达各种工作模式、波束驻留时间和时序参数产生对应的时序信号,然后通过时序发送模块将时序信号通过RS422接口或TTL接口直接发送出去,或者通过光纤数据编码,将时序打包在光纤数据中发送出去。产生的雷达基本工作时序框图如图3所示。

图2 时序控制模块组成框图

图3 雷达基本工作时序框图

1.2.3 高速通道及光纤接口设计

为满足本雷达高速数据传输的需求,共设计了16路高速差分输入输出通道。其中14路高速通道通过两个ZD系列高速连接器替代传统的CPCI连接器实现高速数据交换;另外2路高速通道通过光电转换模块转换为光纤信号与外部实现数据交换。高速通道的连接如图4所示。

图4 高速通道连接示意图

两个光电转换模块的工作流程具体如下:发送数据时,FPGA调用内部的GTX收发器,把待发送的并行数据转换为高速串行数据,送至光电转换模块的发送通道,光电转换模块把串行高速差分信号转换成光信号实现光纤输出。接收数据时,来自光纤的光信号经光电转换模块转换成高速串行的差分信号送到FPGA,FPGA调用内部的GTX收发器,把高速串行数据转换成并行数据,送用户逻辑进行后续处理。光电转换模块的接收和发送端口直接与GTX收发器的发送端和接收端相连,使用时只需要编写接口及复位程序即可[4]。FPGA内部高速通道模块的例化示意图如图5所示。高速通道传输速率为2.4 Gbit/s,数据位宽为16 bit。高速模块的使用中要注意:FPGA内部接发送端的数据(tx_datain)必须与发送时钟(tx_clk)同步,接收端的数据(rx_dataout)必须与接收时钟(rx_clk)同步,否则高速通道的数据传输会出现误码。

图5 高速通道模块配置图

1.2.4 RS422接口及TTL接口设计

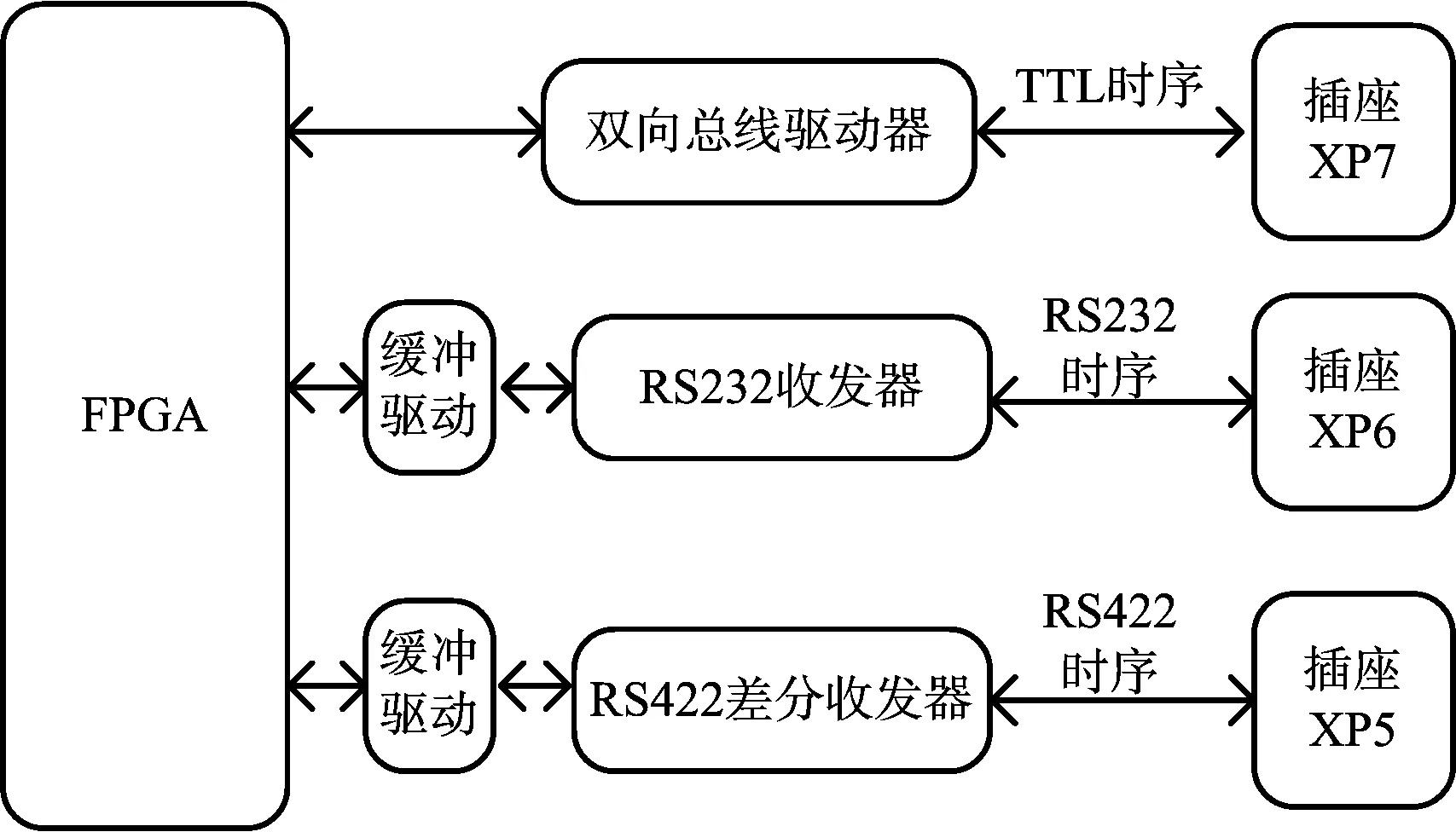

由于雷达规模大,组成设备较多,同时与各设备间的信号接口也不同。为将时序信号同步送至雷达各功能处理设备,本时序控制装置需要提供不同的时序输出接口。除上述光纤接口外,还需具备以下接口:TTL电平的时序输出接口、RS422电平的时序输出接口和RS232电平的时序输出接口等。RS422及TTL接口设计示意图如图6所示。其中,TTL电平接口芯片选用双向驱动芯片IDT74FCT164系列,实现LVTTL电平到TTL电平的转换;RS422电平接口芯片选用SN65LBC174系列,实现RS422电平的时序信号输出;选用MAX202ESE芯片,实现RS232电平的时序信号输出。

图6 RS422及TTL接口设计示意图

2 测试性设计

2.1 CPCI总线接口测试设计

CPCI总线接口的测试可利用WinDriver软件来实现,该软件是一款简洁高效不涉及操作系统底层编程且兼容性很好的驱动开发工具[5]。具体测试流程如下:通过软硬件配合,在FPGA内部专门设计1个32位的读写寄存器,利用WinDriver软件对该寄存器进行读写操作,例如写入测试数据“55AAAA55”,检查读出的数据是否与此相同,如果相同,则判定CPCI总线工作正常。否则,CPCI总线有故障。利用WinDriver软件还可以识别时序控制装置的VenderID、DeviceID、分配的基地址和分配的中断信息等。

2.2 时序控制模块测试设计

时序控制模块的测试思路如下:在FPGA内部设计独立的时序采集测试模块,对本雷达产生的时序信号BW、CPI和PRF信号进行采集和计数;同时将采集到的数据送至测试计算机与计算机写入时序产生模块的时序参数进行比对,如果参数一致,表示时序控制模块工作正常。例如在规定的测试时间周期内对PRF脉冲的个数和周期分别进行采集和计数,计数结果保存到测试寄存器内,在测试周期结束后,CPCI测试计算机读取PRF周期测试寄存器和PRF数量测试寄存器的数值,与原来写入时序产生模块的数值进行比对是否一致。时序控制模块的测试框图如图7所示。

图7 时序控制模块测试框图

也可通过SignalTap软件抓取典型信号的波形来辨别时序信号是否正常。

2.3 光纤接口测试设计

光纤接口的测试流程如下:FPGA通过光电转换模块输出的光纤信号,通过光纤跳线器,接至光电转换模块的输入端,进行闭环测试。在Quartus软件中调用SignalTap软件,对光纤发送和接收的数据进行比对。光纤接口测试框图如图8所示。

图8 光纤接口测试框图

在正常情况下,光纤接收到的数据和发送的数据是相同的。在测试时,需要同时关注rx_errdetect[1..0]信号是否出现高电平的跳变。rx_errdetect[1]表示16位接收数据中的高8位有没有接收到错误的数据,rx_errdetect[0]表示16位接收数据中的低8位有没有接收到错误的数据。正常情况下,rx_errdetect[1]和rx_errdetect[0]均为低电平,表示光纤通道中没有接收到错误数据。

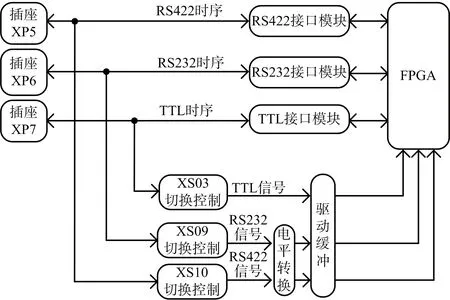

2.4 RS422接口和TTL接口测试设计

在时序控制装置硬件设计时,就考虑到了RS422接口、TTL接口和RS232接口的测试性设计。时序信号测试模块的连接示意图如图9所示。

图9 RS422接口及TTL接口测试框图

如图9所示,FPGA输出至高速连接器插座的RS422电平的时序信号、TTL电平的时序信号和RS232电平的时序信号等通过切换控制经各种电平逆变换后,再接回FPGA,在FPGA中通过SignalTap软件对信号进行波形采集并与原输出信号比对,可验证输出信号是否正常。

3 结束语

本时序控制装置采用标准CPCI总线+FPGA的系统架构,创造性地利用ZD系列高速插座替代传统CPCI连接器,从而实现高速数据的内外交换;本时序控制装置具有完善的自我测试功能:所有功能模块和输入输出信号均可自我测试。具有16路高速输入输出通道,数据吞吐率达80 Gbit/s;具备多种时序输出接口:支持光纤接口、TTL电平、RS422电平、RS232电平等输出接口;参数化、

可编程的时序设计方法可适应相控阵雷达波束扫描和时序产生的需求。本时序控制装置已成功应用在某雷达中,取得了良好的验证效果。